IEC 62014-4:2025

(Main)IP-XACT, Standard Structure for Packaging, Integrating, and Reusing IP within Tool Flows

IP-XACT, Standard Structure for Packaging, Integrating, and Reusing IP within Tool Flows

IEC 62014-4:2025 describes an eXtensible Markup Language (XML) schema for meta-data documenting intellectual property (IP) used in the development, implementation, and verification of electronic systems. This schema provides both a standard method to document IP that is compatible with automated integration techniques and a standard method (generators) for linking tools into a system development framework, enabling a more flexible, optimized development environment. Tools compliant with this standard will be able to interpret, configure, integrate, and manipulate IP blocks that comply with the IP meta-data description. The standard is independent of any specific design processes. It does not cover behavioral characteristics of the IP that are not relevant to integration. This standard enables the creation and exchange of IP in a highly automated design environment.

This standard is published as a double logo IEC-IEEE standard.

General Information

- Status

- Published

- Publication Date

- 24-Jun-2025

- Technical Committee

- TC 91 - Electronics assembly technology

- Drafting Committee

- WG 13 - TC 91/WG 13

- Current Stage

Relations

- Effective Date

- 14-Mar-2025

Overview

IEC 62014-4:2025 - IP‑XACT, Standard Structure for Packaging, Integrating, and Reusing IP within Tool Flows defines an XML schema for IP meta-data used in the development, implementation, and verification of electronic systems. Published as a double‑logo IEC‑IEEE standard (aligned with IEEE Std 1685), this edition standardizes how intellectual property (IP) is described so tools can automatically interpret, configure, integrate, and manipulate IP blocks across tool flows. The standard is process‑agnostic and focuses on integration‑relevant metadata rather than IP behavioral details.

Key topics and requirements

- XML schema for IP meta‑data: standardized format to describe components, ports, buses, memory maps, registers, and models for automated exchange.

- Component and design descriptions: rules for packaging component definitions, interfaces, interconnections, file sets, and clear‑box elements.

- Interface definitions: busDefinitions, abstractionDefinitions, ports (wire, transactional, grouped), qualifiers, and complex interconnections.

- Addressing and memory maps: address spaces, memory mapping, remapping, and rules for calculating bit and bus addresses.

- Registers and type definitions: register files, fields, enumerations, access policies and semantic consistency checks.

- Generators and generator chains: standardized mechanism to link tools into a development framework (component generators, generatorChain, selectors).

- Design configurations & catalogs: design views, configuration of interconnections and abstractors, and catalog management for IP exchange.

- Abstractors and models: abstractor descriptions, views, and models to enable simulation and verification abstraction.

- Data visibility & semantic rules: rules for bit visibility, address translation, and consistency to ensure interoperable exchanges between tools.

Applications and who should use it

- IP vendors packaging reusable IP blocks for third‑party integration.

- SoC architects and system integrators assembling multi‑vendor designs.

- EDA tool developers implementing import/export, configuration, and generator support.

- Verification engineers automating model and testbench generation from IP meta‑data.

- Embedded systems teams using automated flows for register access, memory mapping, and address translation.

Practical benefits include reduced manual integration effort, improved automation in tool chains, consistent IP documentation, and easier exchange of IP between organizations.

Related standards

- IEEE Std 1685 (aligned standard; IEC 62014‑4:2025 published under IEC‑IEEE double logo)

- Other IP‑XACT family documents (referenced within IEC 62014‑4) for broader interoperability and tooling guidance.

Keywords: IEC 62014‑4:2025, IP‑XACT, IP meta‑data, XML schema, IP packaging, generator chains, memory map, register description, tool flows, IEC‑IEEE.

Get Certified

Connect with accredited certification bodies for this standard

BSI Group

BSI (British Standards Institution) is the business standards company that helps organizations make excellence a habit.

National Aerospace and Defense Contractors Accreditation Program (NADCAP)

Global cooperative program for special process quality in aerospace.

CARES (UK Certification Authority for Reinforcing Steels)

UK certification for reinforcing steels and construction.

Sponsored listings

Frequently Asked Questions

IEC 62014-4:2025 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "IP-XACT, Standard Structure for Packaging, Integrating, and Reusing IP within Tool Flows". This standard covers: IEC 62014-4:2025 describes an eXtensible Markup Language (XML) schema for meta-data documenting intellectual property (IP) used in the development, implementation, and verification of electronic systems. This schema provides both a standard method to document IP that is compatible with automated integration techniques and a standard method (generators) for linking tools into a system development framework, enabling a more flexible, optimized development environment. Tools compliant with this standard will be able to interpret, configure, integrate, and manipulate IP blocks that comply with the IP meta-data description. The standard is independent of any specific design processes. It does not cover behavioral characteristics of the IP that are not relevant to integration. This standard enables the creation and exchange of IP in a highly automated design environment. This standard is published as a double logo IEC-IEEE standard.

IEC 62014-4:2025 describes an eXtensible Markup Language (XML) schema for meta-data documenting intellectual property (IP) used in the development, implementation, and verification of electronic systems. This schema provides both a standard method to document IP that is compatible with automated integration techniques and a standard method (generators) for linking tools into a system development framework, enabling a more flexible, optimized development environment. Tools compliant with this standard will be able to interpret, configure, integrate, and manipulate IP blocks that comply with the IP meta-data description. The standard is independent of any specific design processes. It does not cover behavioral characteristics of the IP that are not relevant to integration. This standard enables the creation and exchange of IP in a highly automated design environment. This standard is published as a double logo IEC-IEEE standard.

IEC 62014-4:2025 is classified under the following ICS (International Classification for Standards) categories: 25.040.01 - Industrial automation systems in general; 35.240.50 - IT applications in industry. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 62014-4:2025 has the following relationships with other standards: It is inter standard links to IEC 62014-4:2015. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 62014-4:2025 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 62014-4 ®

Edition 2.0 2025-06

INTERNATIONAL

™

IEEE Std 1685

STANDARD

IP-XACT, Standard Structure for Packaging, Integrating, and Reusing IP

within Tool Flows

ICS 35.240.50; 25.040.01 ISBN 978-2-8327-0468-4

All rights reserved. IEEE is a registered trademark in the U.S. Patent & Trademark Office, owned by the Institute of

Electrical and Electronics Engineers, Inc. Unless otherwise specified, no part of this publication may be reproduced or

utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission

in writing from the IEC Central Office. Any questions about IEEE copyright should be addressed to the IEEE. Enquiries

about obtaining additional rights to this publication and other information requests should be addressed to the IEC or

your local IEC member National Committee.

IEC Secretariat Institute of Electrical and Electronics Engineers, Inc.

3, rue de Varembé 3 Park Avenue

CH-1211 Geneva 20 New York, NY 10016-5997

Switzerland United States of America

Tel.: +41 22 919 02 11 stds.ipr@ieee.org

info@iec.ch www.ieee.org

www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC/IEEE publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigendum or an amendment might have been published.

IEC publications search - webstore.iec.ch/advsearchform IEC Products & Services Portal - products.iec.ch

The advanced search enables to find IEC publications by a Discover our powerful search engine and read freely all the

variety of criteria (reference number, text, technical publications previews, graphical symbols and the glossary. With a

committee, …). It also gives information on projects, replaced subscription you will always have access to up to date content

and withdrawn publications. tailored to your needs.

IEC Just Published - webstore.iec.ch/justpublished

Electropedia - www.electropedia.org

Stay up to date on all new IEC publications. Just Published

The world's leading online dictionary on electrotechnology,

details all new publications released. Available online and

containing more than 22 500 terminological entries in English and

once a month by email.

French, with equivalent terms in 25 additional languages. Also

known as the International Electrotechnical Vocabulary (IEV)

IEC Customer Service Centre - webstore.iec.ch/csc

online.

If you wish to give us your feedback on this publication or need

further assistance, please contact the Customer Service

Centre: sales@iec.ch.

IEEE Std 1685™‐2022

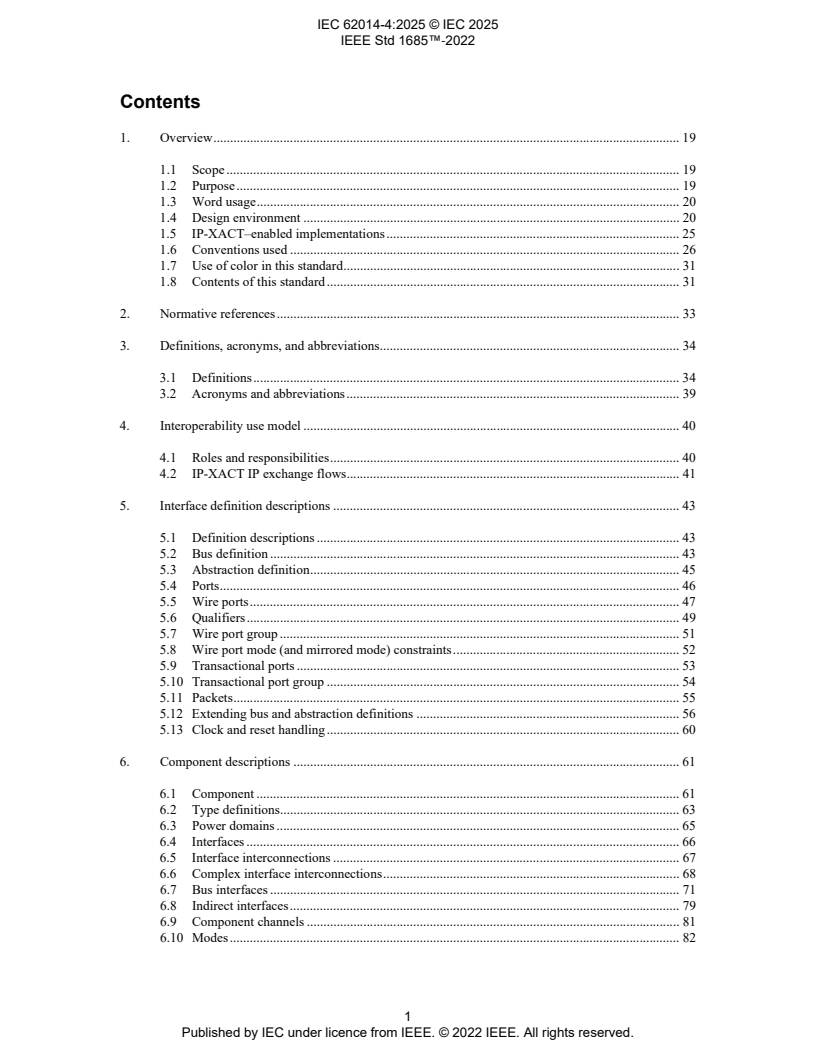

Contents

1. Overview. 19

1.1 Scope . 19

1.2 Purpose. 19

1.3 Word usage. 20

1.4 Design environment . 20

1.5 IP-XACT–enabled implementations. 25

1.6 Conventions used . 26

1.7 Use of color in this standard. 31

1.8 Contents of this standard. 31

2. Normative references. 33

3. Definitions, acronyms, and abbreviations. 34

3.1 Definitions. 34

3.2 Acronyms and abbreviations. 39

4. Interoperability use model . 40

4.1 Roles and responsibilities. 40

4.2 IP-XACT IP exchange flows.41

5. Interface definition descriptions . 43

5.1 Definition descriptions . 43

5.2 Bus definition . 43

5.3 Abstraction definition. 45

5.4 Ports. 46

5.5 Wire ports. 47

5.6 Qualifiers. 49

5.7 Wire port group . 51

5.8 Wire port mode (and mirrored mode) constraints. 52

5.9 Transactional ports . 53

5.10 Transactional port group . 54

5.11 Packets. 55

5.12 Extending bus and abstraction definitions . 56

5.13 Clock and reset handling. 60

6. Component descriptions . 61

6.1 Component . 61

6.2 Type definitions. 63

6.3 Power domains . 65

6.4 Interfaces . 66

6.5 Interface interconnections . 67

6.6 Complex interface interconnections. 68

6.7 Bus interfaces . 71

6.8 Indirect interfaces. 79

6.9 Component channels . 81

6.10 Modes. 82

Published by IEC under licence from IEEE. © 2022 IEEE. All rights reserved.

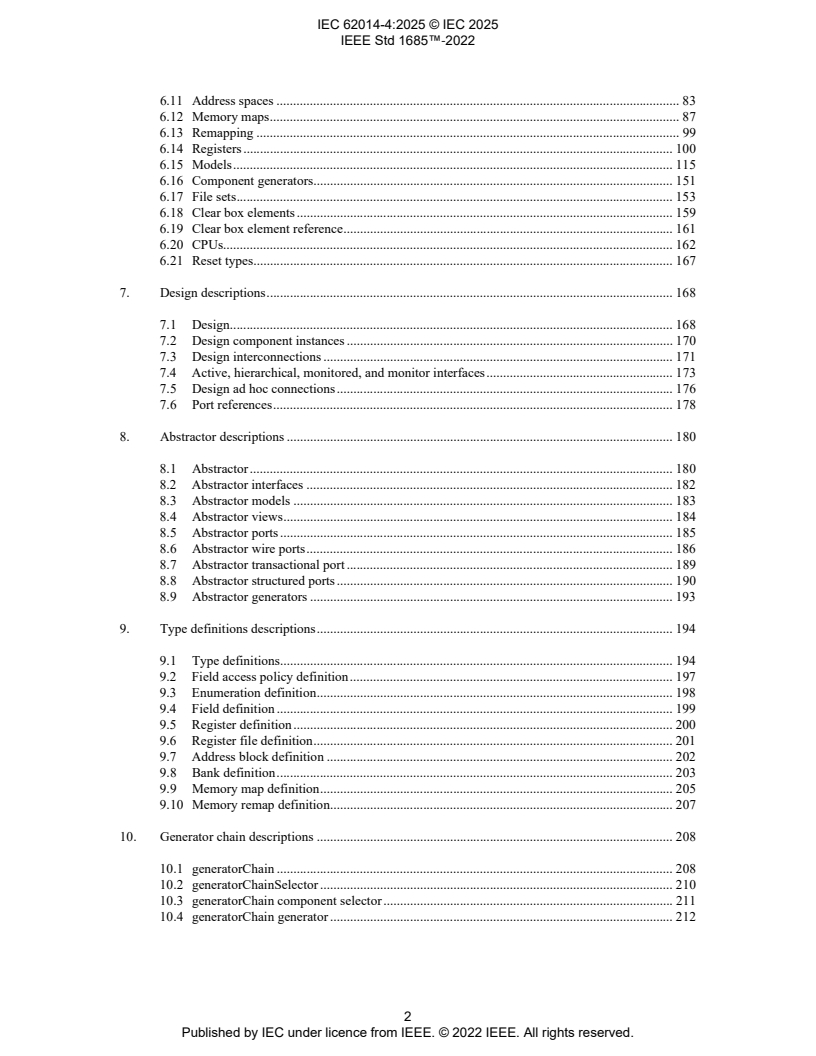

IEEE Std 1685™‐2022

6.11 Address spaces . 83

6.12 Memory maps. 87

6.13 Remapping . 99

6.14 Registers. 100

6.15 Models. 115

6.16 Component generators. 151

6.17 File sets. 153

6.18 Clear box elements. 159

6.19 Clear box element reference. 161

6.20 CPUs. 162

6.21 Reset types. 167

7. Design descriptions. 168

7.1 Design. 168

7.2 Design component instances . 170

7.3 Design interconnections . 171

7.4 Active, hierarchical, monitored, and monitor interfaces. 173

7.5 Design ad hoc connections. 176

7.6 Port references. 178

8. Abstractor descriptions . 180

8.1 Abstractor. 180

8.2 Abstractor interfaces . 182

8.3 Abstractor models . 183

8.4 Abstractor views. 184

8.5 Abstractor ports. 185

8.6 Abstractor wire ports. 186

8.7 Abstractor transactional port . 189

8.8 Abstractor structured ports. 190

8.9 Abstractor generators . 193

9. Type definitions descriptions. 194

9.1 Type definitions. 194

9.2 Field access policy definition. 197

9.3 Enumeration definition. 198

9.4 Field definition . 199

9.5 Register definition . 200

9.6 Register file definition. 201

9.7 Address block definition . 202

9.8 Bank definition. 203

9.9 Memory map definition. 205

9.10 Memory remap definition. 207

10. Generator chain descriptions . 208

10.1 generatorChain . 208

10.2 generatorChainSelector . 210

10.3 generatorChain component selector . 211

10.4 generatorChain generator . 212

Published by IEC under licence from IEEE. © 2022 IEEE. All rights reserved.

IEEE Std 1685™‐2022

11. Design configuration descriptions . 214

11.1 Design configuration. 214

11.2 designConfiguration . 215

11.3 interconnectionConfiguration. 216

11.4 abstractorInstance. 217

11.5 viewConfiguration. 218

12. Catalog descriptions. 219

12.1 catalog . 219

12.2 ipxactFile. 221

13. Addressing . 222

13.1 Calculating the bit address of a bit in a memory map or address space. 222

13.2 Calculating the bus address at the bus interface. 224

13.3 Calculating the address at the indirect interface. 224

13.4 Address modifications of a channel . 225

13.5 Address translation in a bridge. 225

14. Data visibility. 226

14.1 Mapped address bits mask. 226

14.2 Address modifications of an interconnection. 226

14.3 Bit steering in a channel. 226

14.4 Visibility of bits. 227

Annex A Bibliography . 230

Annex B Semantic consistency rules . 231

B.1 Semantic consistency rule definitions. 231

B.1.1 Compatibility of busDefinitions. 231

B.1.2 Interface mode of a bus interface . 231

B.1.3 Compatibility of abstractionDefinitions. 231

B.1.4 Element referenced by configurableElementValue element. 231

B.1.5 Memory mapping . 231

B.1.6 Port connection equivalence class. 232

B.1.7 Logical and physical ports. 232

B.1.8 Addressable bus interface. 232

B.1.9 Field connection graph . 232

B.2 Rule listings . 234

B.2.1 Cross-references and VLNVs . 234

B.2.2 Interconnections . 238

B.2.3 Channels, bridges, and abstractors . 240

B.2.4 Monitor interfaces and monitor interconnections . 243

B.2.5 Configurable elements . 244

B.2.6 Ports . 247

B.2.7 Registers . 255

B.2.8 Memory maps . 259

B.2.9 Addressing . 260

B.2.10 Hierarchy . 261

B.2.11 Hierarchy and memory maps . 262

Published by IEC under licence from IEEE. © 2022 IEEE. All rights reserved.

IEEE Std 1685™‐2022

B.2.12 Constraints . 262

B.2.13 Design configurations . 264

B.2.14 Expressions . 265

B.2.15 Access handles . 268

Annex C Common elements and concepts. 269

C.1 accessHandles . 269

C.1.1 simpleAccessHandle . 269

C.1.2 slicedAccessHandle. 270

C.1.3 portAccessHandle. 271

C.1.4 sliceType . 272

C.1.5 portSliceType . 272

C.2 accessPolicies. 273

C.2.1 Schema . 273

C.2.2 Description . 273

C.3 Access resolution . 274

C.4 arrays. 275

C.4.1 Configurable arrays with arrayId . 275

C.4.2 Configurable arrays without arrayId . 276

C.4.3 Memory arrays with stride . 276

C.4.4 Field arrays with bit stride. 277

C.5 assertions. 278

C.5.1 Schema . 278

C.5.2 Description . 278

C.6 attributes. 279

C.6.1 Schema . 279

C.6.2 Description . 280

C.7 complexBaseExpression . 281

C.7.1 complexTiedValueExpression . 282

C.7.2 qualifiedExpression. 282

C.7.3 realExpression . 283

C.7.4 signedLongintExpression . 284

C.7.5 stringExpression . 285

C.7.6 unresolvedStringExpression. 285

C.7.7 unresolvedUnsignedBitExpression . 286

C.7.8 unresolvedUnsignedPositiveIntExpression. 286

C.7.9 unsignedBitExpression. 287

C.7.10 unsignedBitVectorExpression. 287

C.7.11 unsignedIntExpression . 288

C.7.12 unsignedLongintExpression . 289

C.7.13 unsignedPositiveIntExpression . 290

C.7.14 unsignedPositiveLongintExpression . 291

C.8 choices . 292

C.8.1 Schema . 292

C.9 configurableElementValues. 293

C.9.1 Schema . 293

C.9.2 Description . 293

C.10 configurableLibraryRefType . 294

C.10.1 Schema . 294

C.10.2 Description . 294

C.11 documentName group. 295

C.11.1 Schema . 295

C.11.2 Description . 295

Published by IEC under licence from IEEE. © 2022 IEEE. All rights reserved.

IEEE Std 1685™‐2022

C.12 Endianness . 296

C.13 fieldReferenceGroup. 297

C.13.1 Schema . 297

C.13.2 Description . 297

C.14 fieldSliceReferenceGroup. 299

C.14.1 Schema . 299

C.14.2 Description . 300

C.15 fileSetRef . 300

C.15.1 Schema . 300

C.15.2 Description . 301

C.16 fileType. 301

C.16.1 Schema . 301

C.16.2 Description . 301

C.17 indices . 302

C.17.1 Schema . 302

C.17.2 Description . 302

C.18 libraryRefType. 303

C.18.1 Schema . 303

C.18.2 Description . 303

C.19 Name groups . 304

C.19.1 nameGroup group. 304

C.19.2 nameGroupNMTOKEN group. 305

C.19.3 nameGroupOptional group. 306

C.19.4 nameGroupPort group . 307

C.19.5 nameGroupString group. 308

C.20 nameValuePairType. 308

C.20.1 Schema . 308

C.20.2 Description . 309

C.21 parameters. 309

C.21.1 Schema . 309

C.21.2 Description . 309

C.22 partSelect . 310

C.22.1 Schema . 310

C.22.2 Description . 310

C.23 pathSegments . 311

C.23.1 pathSegment . 311

C.23.2 portPathSegment . 311

C.24 Power constraints. 312

C.24.1 transactionalPowerConstraints . 312

C.24.2 wirePowerConstraints . 312

C.25 range. 313

C.25.1 Schema . 313

C.25.2 Description . 313

C.26 Vectors . 314

C.26.1 vectors . 314

C.26.2 extendedVectorsType. 314

C.27 vendorExtensions. 315

C.27.1 Schema . 315

C.27.2 Description . 315

C.28 versionedIdentifier group. 315

C.28.1 Schema . 315

C.28.2 Description . 316

C.28.3 Sorting and comparing version elements . 316

C.28.4 Version control. 317

Published by IEC under licence from IEEE. © 2022 IEEE. All rights reserved.

IEEE Std 1685™‐2022

C.29 viewRef. 318

C.29.1 Schema . 318

C.29.2 Description . 318

C.30 xml:id . 318

C.31 Component vs. Abstraction Definition Ports. 318

Annex D Types. 320

D.1 boolean. 320

D.2 float . 320

D.3 ID or IDREF . 320

D.4 instancePath . 320

D.5 integer . 320

D.6 libraryRefType. 320

D.7 Name. 320

D.8 NMTOKEN . 321

D.9 NMTOKENS . 321

D.10 portName . 321

D.11 ipxactURI. 321

D.12 string . 321

D.13 token. 321

Annex E SystemVerilog expressions. 322

E.1 Overview. 322

E.2 Data-types . 322

E.2.1 bit data type . 322

E.2.2 byte data type . 322

E.2.3 shortint data type . 323

E.2.4 int data type . 323

E.2.5 longint data type . 323

E.2.6 shortreal data type . 323

E.2.7 real data type . 323

E.2.8 string data type . 323

E.2.9 Signed and unsigned data types . 324

E.2.10 Unresolved data types . 324

E.3 Assignments. 324

E.3.1 Single value assignment . 324

E.3.2 Parameter type. 324

E.3.3 Parameter signing. 325

E.3.4 Vector assignment . 325

E.3.5 Array assignment. 325

E.3.6 Identifiers . 326

E.3.7 Identifier references. 326

E.4 Operators. 328

E.5 Functions. 329

E.5.1 Integer function . 329

E.5.2 Real functions. 329

E.5.3 String function. 330

E.5.4 IP-XACT specific functions. 332

E.5.5 IP-XACT specific escape sequences. 334

E.6 Expression language formal syntax (BNF). 335

E.6.1 Declarations: declaration data types. 335

E.6.2 Behavioral statements: Case statements. 335

Published by IEC under licence from IEEE. © 2022 IEEE. All rights reserved.

IEEE Std 1685™‐2022

E.6.3 Expressions. 336

E.6.4 General: Identifiers. 337

E.7 SystemVerilog conversion steps. 338

E.7.1 Convert parameter . 338

E.7.2 Convert expression. 338

E.8 SystemVerilog reference. 338

Annex F Tight generator interface. 341

F.1 Method of communication. 341

F.2 Generator invocation. 341

F.2.1 Resolving the URL. 342

F.2.2 Example. 342

F.3 TGI API . 343

F.3.1 TGI fault codes. 344

F.3.2 Administrative commands. 344

F.3.3 Return values. 345

F.4 IDs and configurable values . 345

F.5 TGI messages. 346

F.6 Vendor attributes. 346

F.7 TGI calls . 346

F.7.1 Category index .

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...