IEC 62530:2021

(Main)SystemVerilog - Unified Hardware Design, Specification, and Verification Language

SystemVerilog - Unified Hardware Design, Specification, and Verification Language

IEC 62530:2021(E) provides the definition of the language syntax and semantics for the IEEE 1800™ SystemVerilog language, which is a unified hardware design, specification, and verification language. The standard includes support for behavioral, register transfer level (RTL), and gate-level hardware descriptions; testbench, coverage, assertion, object-oriented, and constrained random constructs; and also provides application programming interfaces (APIs) to foreign programming languages.

This edition corrects errors and clarifies aspects of the language definition in IEEE Std 1800-2012.1 This revision also provides enhanced features that ease design, improve verification, and enhance cross-language interactions.

This publication has the status of a double logo IEEE/IEC standard.

General Information

- Status

- Published

- Publication Date

- 25-Jul-2021

- Technical Committee

- TC 91 - Electronics assembly technology

- Current Stage

- PPUB - Publication issued

- Start Date

- 26-Jul-2021

- Completion Date

- 04-Jun-2021

Relations

- Revises

IEC 62530:2011 - SystemVerilog - Unified Hardware Design, Specification, and Verification Language - Effective Date

- 05-Sep-2023

Overview

IEC 62530:2021 (IEEE Std 1800-2017) defines the syntax and semantics of SystemVerilog, the unified hardware design, specification, and verification language. This international, double‑logo IEEE/IEC standard covers language constructs for behavioral, RTL, and gate‑level modeling and clarifies and corrects prior language definitions (IEEE Std 1800‑2012.1). The 2021 edition includes enhanced features to ease design, improve verification, and strengthen cross‑language interactions via APIs.

Key topics

The standard provides normative definitions and technical detail for:

- Language syntax and semantics - lexical conventions, tokens, and parsing rules.

- Design descriptions - constructs for behavioral, register‑transfer level (RTL), and gate‑level modeling (modules, interfaces, primitives).

- Verification constructs - testbench components, assertions, functional coverage, and constrained‑random features.

- Object‑oriented features - classes, inheritance, methods, constructors, and encapsulation.

- Data and aggregate types - nets, variables, vectors, arrays (packed, unpacked, dynamic, associative, queues), structures, unions, and enumerations.

- Scheduling and simulation semantics - event simulation, stratified scheduling, determinism considerations, and race conditions.

- Interoperability and APIs - provision for application programming interfaces to foreign programming languages to support co‑simulation and tool integration.

- Normative guidance and examples - compilation/elaboration, scoping, time units/precision, and many illustrative examples.

Practical applications

IEC 62530:2021 is the authoritative reference for:

- Creating synthesizable RTL and gate‑level hardware descriptions.

- Writing robust verification environments and testbenches using assertions, coverage, and constrained random stimulus.

- Implementing object‑oriented verification components and modular testbench architectures.

- Integrating SystemVerilog with external C/C++ or other language models through APIs for co‑simulation and DPI-style interfaces.

- Ensuring tool vendors and EDA flows conform to a consistent language definition for simulation, synthesis, linting, and formal verification.

Who should use this standard

- Hardware designers producing RTL and gate-level models.

- Verification engineers building testbenches, assertions, and coverage-driven tests.

- EDA tool developers implementing SystemVerilog parsers, simulators, and language interfaces.

- System architects and integrators needing reliable cross‑language co‑simulation.

- Academic and training organizations teaching contemporary hardware design and verification practices.

Related standards

- IEEE Std 1800 (SystemVerilog) - IEC 62530 is aligned with and publishes the IEEE SystemVerilog language definition (double‑logo standard).

- Conformance and interoperability guidance from IEC/IEEE publications and vendor documentation may complement this standard.

Keywords: IEC 62530, SystemVerilog standard, IEEE 1800, RTL design, hardware verification, testbench, assertions, constrained random, hardware description language, simulation semantics, EDA tools.

Get Certified

Connect with accredited certification bodies for this standard

BSI Group

BSI (British Standards Institution) is the business standards company that helps organizations make excellence a habit.

National Aerospace and Defense Contractors Accreditation Program (NADCAP)

Global cooperative program for special process quality in aerospace.

CARES (UK Certification Authority for Reinforcing Steels)

UK certification for reinforcing steels and construction.

Sponsored listings

Frequently Asked Questions

IEC 62530:2021 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "SystemVerilog - Unified Hardware Design, Specification, and Verification Language". This standard covers: IEC 62530:2021(E) provides the definition of the language syntax and semantics for the IEEE 1800™ SystemVerilog language, which is a unified hardware design, specification, and verification language. The standard includes support for behavioral, register transfer level (RTL), and gate-level hardware descriptions; testbench, coverage, assertion, object-oriented, and constrained random constructs; and also provides application programming interfaces (APIs) to foreign programming languages. This edition corrects errors and clarifies aspects of the language definition in IEEE Std 1800-2012.1 This revision also provides enhanced features that ease design, improve verification, and enhance cross-language interactions. This publication has the status of a double logo IEEE/IEC standard.

IEC 62530:2021(E) provides the definition of the language syntax and semantics for the IEEE 1800™ SystemVerilog language, which is a unified hardware design, specification, and verification language. The standard includes support for behavioral, register transfer level (RTL), and gate-level hardware descriptions; testbench, coverage, assertion, object-oriented, and constrained random constructs; and also provides application programming interfaces (APIs) to foreign programming languages. This edition corrects errors and clarifies aspects of the language definition in IEEE Std 1800-2012.1 This revision also provides enhanced features that ease design, improve verification, and enhance cross-language interactions. This publication has the status of a double logo IEEE/IEC standard.

IEC 62530:2021 is classified under the following ICS (International Classification for Standards) categories: 25.040.01 - Industrial automation systems in general; 35.060 - Languages used in information technology. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 62530:2021 has the following relationships with other standards: It is inter standard links to IEC 62530:2011. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 62530:2021 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 62530 ®

Edition 3.0 2021-07

™

IEEE Std 1800

INTERNATIONAL

STANDARD

SystemVerilog – Unified Hardware Design, Specification, and Verification

Language

All rights reserved. IEEE is a registered trademark in the U.S. Patent & Trademark Office, owned by the Institute of

Electrical and Electronics Engineers, Inc. Unless otherwise specified, no part of this publication may be reproduced

or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without

permission in writing from the IEC Central Office. Any questions about IEEE copyright should be addressed to the

IEEE. Enquiri es about obtaining additional rights to this publication and other information requests should be

addressed to the IEC or your local IEC member National Committee.

IEC Central Office Institute of Electrical and Electronics Engineers, Inc.

3, rue de Varembé 3 Park Avenue

CH-1211 Geneva 20 New York, NY 10016-5997

Switzerland United States of America

Tel.: +41 22 919 02 11 stds.info@ieee.org

info@iec.ch www.ieee.org

www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigendum or an amendment might have been published.

IEC publications search - webstore.iec.ch/advsearchform IEC online collection - oc.iec.ch

The advanced search enables to find IEC publications by a

Discover our powerful search engine and read freely all the

variety of criteria (reference number, text, technical publications previews. With a subscription you will always

committee, …). It also gives information on projects, replaced have access to up to date content tailored to your needs.

and withdrawn publications.

Electropedia - www.electropedia.org

IEC Just Published - webstore.iec.ch/justpublished

The world's leading online dictionary on electrotechnology,

Stay up to date on all new IEC publications. Just Published

containing more than 22 000 terminological entries in English

details all new publications released. Available online and

and French, with equivalent terms in 18 additional languages.

once a month by email.

Also known as the International Electrotechnical Vocabulary

(IEV) online.

IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or

need further assistance, please contact the Customer Service

Centre: sales@iec.ch.

IEC 62530 ®

Edition 3.0 2021-07

IEEE Std 1800™

INTERNATIONAL

STANDARD

SystemVerilog – Unified Hardware Design, Specification, and Verification

Language

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

ICS 25.040.01; 35.060 ISBN 978-2-8322-9977-7

IEEE Std 1800 ™-2017

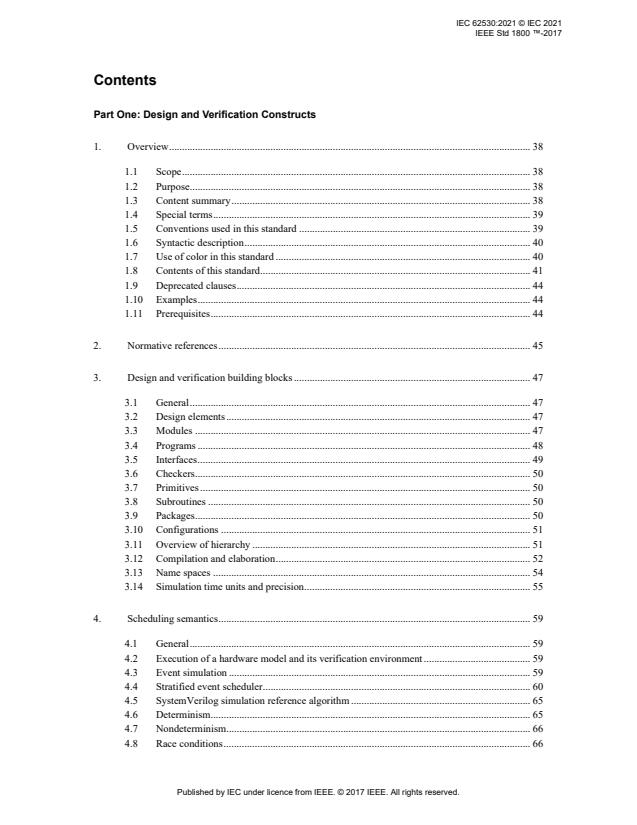

Contents

Part One: Design and Verification Constructs

1. Overview. 38

1.1 Scope. 38

1.2 Purpose. 38

1.3 Content summary. 38

1.4 Special terms. 39

1.5 Conventions used in this standard . 39

1.6 Syntactic description. 40

1.7 Use of color in this standard . 40

1.8 Contents of this standard. 41

1.9 Deprecated clauses. 44

1.10 Examples. 44

1.11 Prerequisites. 44

2. Normative references. 45

3. Design and verification building blocks . 47

3.1 General. 47

3.2 Design elements. 47

3.3 Modules . 47

3.4 Programs . 48

3.5 Interfaces. 49

3.6 Checkers. 50

3.7 Primitives . 50

3.8 Subroutines . 50

3.9 Packages. 50

3.10 Configurations . 51

3.11 Overview of hierarchy . 51

3.12 Compilation and elaboration. 52

3.13 Name spaces . 54

3.14 Simulation time units and precision. 55

4. Scheduling semantics. 59

4.1 General. 59

4.2 Execution of a hardware model and its verification environment . 59

4.3 Event simulation . 59

4.4 Stratified event scheduler. 60

4.5 SystemVerilog simulation reference algorithm . 65

4.6 Determinism. 65

4.7 Nondeterminism. 66

4.8 Race conditions. 66

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800 ™-2017

4.9 Scheduling implication of assignments . 66

4.10 PLI callback control points . 68

5. Lexical conventions . 69

5.1 General. 69

5.2 Lexical tokens . 69

5.3 White space. 69

5.4 Comments . 69

5.5 Operators. 69

5.6 Identifiers, keywords, and system names . 70

5.7 Numbers. 71

5.8 Time literals . 76

5.9 String literals. 76

5.10 Structure literals. 78

5.11 Array literals . 79

5.12 Attributes . 79

5.13 Built-in methods . 81

6. Data types . 83

6.1 General. 83

6.2 Data types and data objects. 83

6.3 Value set . 83

6.4 Singular and aggregate types . 84

6.5 Nets and variables. 85

6.6 Net types . 86

6.7 Net declarations . 97

6.8 Variable declarations . 100

6.9 Vector declarations . 102

6.10 Implicit declarations . 103

6.11 Integer data types . 104

6.12 Real, shortreal, and realtime data types . 105

6.13 Void data type. 105

6.14 Chandle data type. 105

6.15 Class. 106

6.16 String data type . 106

6.17 Event data type. 112

6.18 User-defined types . 112

6.19 Enumerations . 114

6.20 Constants. 119

6.21 Scope and lifetime . 126

6.22 Type compatibility. 128

6.23 Type operator. 131

6.24 Casting . 132

6.25 Parameterized data types . 137

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800 ™-2017

7. Aggregate data types. 139

7.1 General. 139

7.2 Structures . 139

7.3 Unions. 141

7.4 Packed and unpacked arrays . 145

7.5 Dynamic arrays . 149

7.6 Array assignments. 152

7.7 Arrays as arguments to subroutines . 153

7.8 Associative arrays . 155

7.9 Associative array methods .157

7.10 Queues . 161

7.11 Array querying functions . 165

7.12 Array manipulation methods . 165

8. Classes . 170

8.1 General. 170

8.2 Overview. 170

8.3 Syntax . 171

8.4 Objects (class instance). 172

8.5 Object properties and object parameter data. 173

8.6 Object methods . 174

8.7 Constructors . 174

8.8 Typed constructor calls. 176

8.9 Static class properties. 177

8.10 Static methods. 177

8.11 This . 177

8.12 Assignment, renaming, and copying. 178

8.13 Inheritance and subclasses . 180

8.14 Overridden members. 180

8.15 Super . 181

8.16 Casting . 182

8.17 Chaining constructors . 182

8.18 Data hiding and encapsulation. 183

8.19 Constant class properties . 184

8.20 Virtual methods. 184

8.21 Abstract classes and pure virtual methods. 186

8.22 Polymorphism: dynamic method lookup. 187

8.23 Class scope resolution operator :: . 187

8.24 Out-of-block declarations . 189

8.25 Parameterized classes . 191

8.26 Interface classes . 194

8.27 Typedef class . 203

8.28 Classes and structures . 203

8.29 Memory management .204

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800 ™-2017

9. Processes. 205

9.1 General. 205

9.2 Structured procedures . 205

9.3 Block statements . 209

9.4 Procedural timing controls. 215

9.5 Process execution threads . 224

9.6 Process control. 225

9.7 Fine-grain process control . 229

10. Assignment statements . 232

10.1 General. 232

10.2 Overview. 232

10.3 Continuous assignments . 233

10.4 Procedural assignments. 236

10.5 Variable declaration assignment (variable initialization) . 241

10.6 Procedural continuous assignments . 241

10.7 Assignment extension and truncation . 243

10.8 Assignment-like contexts. 244

10.9 Assignment patterns. 245

10.10 Unpacked array concatenation. 249

10.11 Net aliasing . 252

11. Operators and expressions . 254

11.1 General. 254

11.2 Overview. 254

11.3 Operators. 255

11.4 Operator descriptions. 259

11.5 Operands . 279

11.6 Expression bit lengths. 282

11.7 Signed expressions. 285

11.8 Expression evaluation rules . 286

11.9 Tagged union expressions and member access. 287

11.10 String literal expressions. 288

11.11 Minimum, typical, and maximum delay expressions . 290

11.12 Let construct . 291

12. Procedural programming statements . 298

12.1 General. 298

12.2 Overview. 298

12.3 Syntax . 298

12.4 Conditional if–else statement. 299

12.5 Case statement . 304

12.6 Pattern matching conditional statements . 309

12.7 Loop statements . 313

12.8 Jump statements. 317

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800 ™-2017

13. Tasks and functions (subroutines) . 319

13.1 General. 319

13.2 Overview. 319

13.3 Tasks . 319

13.4 Functions. 323

13.5 Subroutine calls and argument passing. 329

13.6 Import and export functions. 334

13.7 Task and function names . 334

13.8 Parameterized tasks and functions. 334

14. Clocking blocks . 336

14.1 General. 336

14.2 Overview. 336

14.3 Clocking block declaration . 336

14.4 Input and output skews . 338

14.5 Hierarchical expressions . 339

14.6 Signals in multiple clocking blocks . 340

14.7 Clocking block scope and lifetime. 340

14.8 Multiple clocking blocks example. 340

14.9 Interfaces and clocking blocks.341

14.10 Clocking block events. 342

14.11 Cycle delay: ## . 342

14.12 Default clocking. 343

14.13 Input sampling . 344

14.14 Global clocking. 345

14.15 Synchronous events . 349

14.16 Synchronous drives. 349

15. Interprocess synchronization and communication. 354

15.1 General. 354

15.2 Overview. 354

15.3 Semaphores. 354

15.4 Mailboxes. 356

15.5 Named events. 359

16. Assertions. 364

16.1 General. 364

16.2 Overview. 364

16.3 Immediate assertions. 364

16.4 Deferred assertions . 367

16.5 Concurrent assertions overview. 374

16.6 Boolean expressions . 377

16.7 Sequences. 378

16.8 Declaring sequences . 382

16.9 Sequence operations . 390

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800 ™-2017

16.10 Local variables. 413

16.11 Calling subroutines on match of a sequence. 419

16.12 Declaring properties. 420

16.13 Multiclock support. 446

16.14 Concurrent assertions. 456

16.15 Disable iff resolution . 473

16.16 Clock resolution. 475

16.17 Expect statement . 481

16.18 Clocking blocks and concurrent assertions. 482

17. Checkers. 484

17.1 Overview. 484

17.2 Checker declaration . 484

17.3 Checker instantiation . 487

17.4 Context inference. 490

17.5 Checker procedures. 491

17.6 Covergroups in checkers. 493

17.7 Checker variables. 494

17.8 Functions in checkers. 500

17.9 Complex checker example. 501

18. Constrained random value generation . 503

18.1 General. 503

18.2 Overview. 503

18.3 Concepts and usage. 503

18.4 Random variables . 506

18.5 Constraint blocks . 509

18.6 Randomization methods .528

18.7 In-line constraints—randomize() with. 530

18.8 Disabling random variables with rand_mode() . 532

18.9 Controlling constraints with constraint_mode() . 534

18.10 Dynamic constraint modification. 535

18.11 In-line random variable control .535

18.12 Randomization of scope variables—std::randomize(). 536

18.13 Random number system functions and methods . 538

18.14 Random stability . 540

18.15 Manually seeding randomize . 542

18.16 Random weighted case—randcase . 543

18.17 Random sequence generation—randsequence. 544

19. Functional coverage. 553

19.1 General. 553

19.2 Overview. 553

19.3 Defining the coverage model: covergroup. 554

19.4 Using covergroup in classes .556

19.5 Defining coverage points . 558

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800 ™-2017

19.6 Defining cross coverage. 569

19.7 Specifying coverage options.578

19.8 Predefined coverage methods . 582

19.9 Predefined coverage system tasks and system functions. 585

19.10 Organization of option and type_option members . 585

19.11 Coverage computation . 586

20. Utility system tasks and system functions . 591

20.1 General. 591

20.2 Simulation control system tasks . 592

20.3 Simulation time system functions. 592

20.4 Timescale system tasks. 594

20.5 Conversion functions . 597

20.6 Data query functions. 598

20.7 Array query functions . 600

20.8 Math functions . 603

20.9 Bit vector system functions. 604

20.10 Severity tasks . 605

20.11 Elaboration system tasks. 606

20.12 Assertion control system tasks. 608

20.13 Sampled value system functions. 614

20.14 Coverage system functions . 615

20.15 Probabilistic distribution functions.615

20.16 Stochastic analysis tasks and functions . 617

20.17 Programmable logic array modeling system tasks . 619

20.18 Miscellaneous tasks and functions. 623

21. Input/output system tasks and system functions.624

21.1 General. 624

21.2 Display system tasks. 624

21.3 File input/output system tasks and system functions. 635

21.4 Loading memory array data from a file . 645

21.5 Writing memory array data to a file. 649

21.6 Command line input. 650

21.7 Value change dump (VCD) files . 653

22. Compiler directives. 674

22.1 General. 674

22.2 Overview . 67

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...