IEC 62433-2:2008

(Main)EMC IC modelling - Part 2: Models of integrated circuits for EMI behavioural simulation - Conducted emissions modelling (ICEM-CE)

EMC IC modelling - Part 2: Models of integrated circuits for EMI behavioural simulation - Conducted emissions modelling (ICEM-CE)

IEC 62433-2:2008 specifies macro-models for ICs to simulate conducted electromagnetic emissions on a printed circuit board. The model is commonly called Integrated Circuit Emission Model - Conducted Emission (ICEM-CE). The ICEM-CE model can also be used for modelling an IC-die, a functional block and an Intellectual Property block (IP). The ICEM-CE model can be used to model both digital and analogue ICs. Basically, conducted emissions have two origins:

- conducted emissions through power supply terminals and ground reference structures;

- conducted emissions through input/output (I/O) terminals. The ICEM-CE model addresses those two types of origins in a single approach. This standard defines structures and components of the macro-model for EMI simulation taking into account the IC's internal activities. This standard gives general data, which can be implemented in different formats or languages such as IBIS, IMIC, SPICE, VHDL-AMS and Verilog. SPICE is however chosen as default simulation environment to cover all the conducted emissions. This standard also specifies requirements for information that shall be incorporated in each ICEM-CE model or component part of the model for model circulation, but description syntax is not within the scope of this standard.

Modèles de circuits intégrés pour la CEM - Partie 2: Modèles de circuits intégrés pour la simulation du comportement lors de perturbations électromagnétiques - Modélisation des émissions conduites (ICEM-CE)

La CEI 62433-2:2008 définit des macromodèles pour circuits intégrés, destinés à simuler les émissions électromagnétiques conduites sur une carte de circuit imprimé. On appelle habituellement ce modèle: Modèle des émissions de circuits intégrés - Émission conduite (ICEM-CE). Le modèle ICEM-CE peut également être utilisé pour modéliser une puce de circuit intégré, un bloc fonctionnel et un bloc à propriété intellectuelle (IP). Le modèle ICEM-CE peut être utilisé pour modéliser à la fois des circuits intégrés numériques et analogiques. Les émissions conduites ont fondamentalement deux origines:

- les émissions conduites par l'intermédiaire des bornes d'alimentation et des structures de référence de masse;

- les émissions conduites par l'intermédiaire des bornes d'entrée/sortie (E/S). Le modèle ICEM-CE traite ces deux types d'origine en une approche unique. La présente norme définit les structures et les composants du macromodèle pour la simulation des perturbations électromagnétiques en tenant compte des activités internes du circuit intégré. La présente norme fournit des données générales, pouvant être mises en oeuvre dans des formats ou des langages différents tels que: IBIS, IMIC, SPICE, VHDL-AMS et Verilog. On choisit toutefois SPICE comme environnement de simulation par défaut pour couvrir la totalité des émissions conduites. La présente norme spécifie également les exigences relatives aux informations qui doivent être incorporées dans chaque modèle ICEM-CE ou élément constituant du modèle pour la circulation du modèle. La syntaxe de la description ne fait toutefois pas partie du domaine d'application de la présente norme.

General Information

- Status

- Published

- Publication Date

- 07-Oct-2008

- Technical Committee

- SC 47A - Integrated circuits

- Drafting Committee

- WG 2 - TC 47/SC 47A/WG 2

- Current Stage

- DELPUB - Deleted Publication

- Start Date

- 27-Jan-2017

- Completion Date

- 14-Feb-2026

Relations

- Effective Date

- 05-Sep-2023

Overview

IEC 62433-2:2008 defines macro-models for electromagnetic compatibility (EMC) of integrated circuits - specifically conducted emissions modelling using the Integrated Circuit Emission Model – Conducted Emission (ICEM-CE). The standard describes model structures and components to simulate conducted electromagnetic interference (EMI) generated by an IC on a printed circuit board (PCB). ICEM-CE supports modelling of IC dies, functional blocks and intellectual property (IP) blocks, for both digital and analogue devices, and can be implemented in formats such as SPICE, IBIS, IMIC, VHDL-AMS and Verilog (SPICE is the default environment).

Key topics and requirements

- Two emission origins: conducted emissions via power-supply/ground reference structures and via input/output (I/O) terminals - both are treated in a unified modelling approach.

- Macro-model building blocks: Internal Activity (IA), Passive Distribution Network (PDN) and Inter-Block Coupling (IBC). These represent the IC’s internal switching activity, the package/board distribution network, and coupling between blocks respectively.

- Model types: block-based and sub-model-based IC macro-model structures to represent different levels of detail and modularity.

- Parameter extraction: requirements for extracting IA, PDN and IBC parameters from measurement or design data so models accurately reflect real-device behaviour.

- Simulation environment: provides general model data adaptable to multiple languages and file formats; SPICE is specified as the default to cover conducted emission simulations.

- Model circulation info: the standard specifies what information must accompany each ICEM-CE model for reuse and validation, though it does not define the exact syntax for model descriptions.

- Normative references: aligns with conducted-emission measurement standards (IEC 61967 series, including IEC 61967-4 for 150 kHz–1 GHz measurements and the 1 Ω/150 Ω direct coupling method).

Applications and practical value

- Predicting and mitigating conducted emissions from ICs during PCB-level EMI behavioural simulation.

- Supporting IC and PCB co‑design by enabling early simulation of power‑supply noise, I/O emissions and the impact of decoupling strategies.

- Enabling correlation between simulation and laboratory measurements (per IEC 61967) to accelerate compliance testing.

- Useful for IC designers, EMC engineers, PCB designers, system integrators, EDA tool vendors and test laboratories who need reproducible macro-models for EMI analysis.

- Applicable to modelling digital switching noise, analogue block interactions, IP reuse scenarios, and optimization of PDN/decoupling components.

Related standards

- IEC 61967 (all parts) - Integrated Circuits: measurement of electromagnetic emissions, 150 kHz to 1 GHz.

- IEC 61967-4 - Measurement of conducted emissions: 1 Ω/150 Ω direct coupling method.

Keywords: IEC 62433-2, ICEM-CE, EMC IC modelling, conducted emissions modelling, EMI behavioural simulation, SPICE macro-model, PDN, Internal Activity, I/O emissions.

Buy Documents

IEC 62433-2:2008 - EMC IC modelling - Part 2: Models of integrated circuits for EMI behavioural simulation - Conducted emissions modelling (ICEM-CE) Released:10/8/2008

IEC 62433-2:2008 - EMC IC modelling - Part 2: Models of integrated circuits for EMI behavioural simulation - Conducted emissions modelling (ICEM-CE) Released:10/8/2008

Frequently Asked Questions

IEC 62433-2:2008 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "EMC IC modelling - Part 2: Models of integrated circuits for EMI behavioural simulation - Conducted emissions modelling (ICEM-CE)". This standard covers: IEC 62433-2:2008 specifies macro-models for ICs to simulate conducted electromagnetic emissions on a printed circuit board. The model is commonly called Integrated Circuit Emission Model - Conducted Emission (ICEM-CE). The ICEM-CE model can also be used for modelling an IC-die, a functional block and an Intellectual Property block (IP). The ICEM-CE model can be used to model both digital and analogue ICs. Basically, conducted emissions have two origins: - conducted emissions through power supply terminals and ground reference structures; - conducted emissions through input/output (I/O) terminals. The ICEM-CE model addresses those two types of origins in a single approach. This standard defines structures and components of the macro-model for EMI simulation taking into account the IC's internal activities. This standard gives general data, which can be implemented in different formats or languages such as IBIS, IMIC, SPICE, VHDL-AMS and Verilog. SPICE is however chosen as default simulation environment to cover all the conducted emissions. This standard also specifies requirements for information that shall be incorporated in each ICEM-CE model or component part of the model for model circulation, but description syntax is not within the scope of this standard.

IEC 62433-2:2008 specifies macro-models for ICs to simulate conducted electromagnetic emissions on a printed circuit board. The model is commonly called Integrated Circuit Emission Model - Conducted Emission (ICEM-CE). The ICEM-CE model can also be used for modelling an IC-die, a functional block and an Intellectual Property block (IP). The ICEM-CE model can be used to model both digital and analogue ICs. Basically, conducted emissions have two origins: - conducted emissions through power supply terminals and ground reference structures; - conducted emissions through input/output (I/O) terminals. The ICEM-CE model addresses those two types of origins in a single approach. This standard defines structures and components of the macro-model for EMI simulation taking into account the IC's internal activities. This standard gives general data, which can be implemented in different formats or languages such as IBIS, IMIC, SPICE, VHDL-AMS and Verilog. SPICE is however chosen as default simulation environment to cover all the conducted emissions. This standard also specifies requirements for information that shall be incorporated in each ICEM-CE model or component part of the model for model circulation, but description syntax is not within the scope of this standard.

IEC 62433-2:2008 is classified under the following ICS (International Classification for Standards) categories: 31.200 - Integrated circuits. Microelectronics. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 62433-2:2008 has the following relationships with other standards: It is inter standard links to IEC 62433-2:2017. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 62433-2:2008 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 62433-2

Edition 1.0 2008-10

INTERNATIONAL

STANDARD

EMC IC modelling –

Part 2: Models of integrated circuits for EMI behavioural simulation – Conducted

emissions modelling (ICEM-CE)

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form

or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from

either IEC or IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication,

please contact the address below or your local IEC member National Committee for further information.

IEC Central Office

3, rue de Varembé

CH-1211 Geneva 20

Switzerland

Email: inmail@iec.ch

Web: www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

ƒ Catalogue of IEC publications: www.iec.ch/searchpub

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,…).

It also gives information on projects, withdrawn and replaced publications.

ƒ IEC Just Published: www.iec.ch/online_news/justpub

Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available

on-line and also by email.

ƒ Electropedia: www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions

in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical

Vocabulary online.

ƒ Customer Service Centre: www.iec.ch/webstore/custserv

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service

Centre FAQ or contact us:

Email: csc@iec.ch

Tel.: +41 22 919 02 11

Fax: +41 22 919 03 00

IEC 62433-2

Edition 1.0 2008-10

INTERNATIONAL

STANDARD

EMC IC modelling –

Part 2: Models of integrated circuits for EMI behavioural simulation – Conducted

emissions modelling (ICEM-CE)

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

PRICE CODE

X

ICS 31.200 ISBN 978-2-88910-702-5

– 2 – 62433-2 © IEC:2008(E)

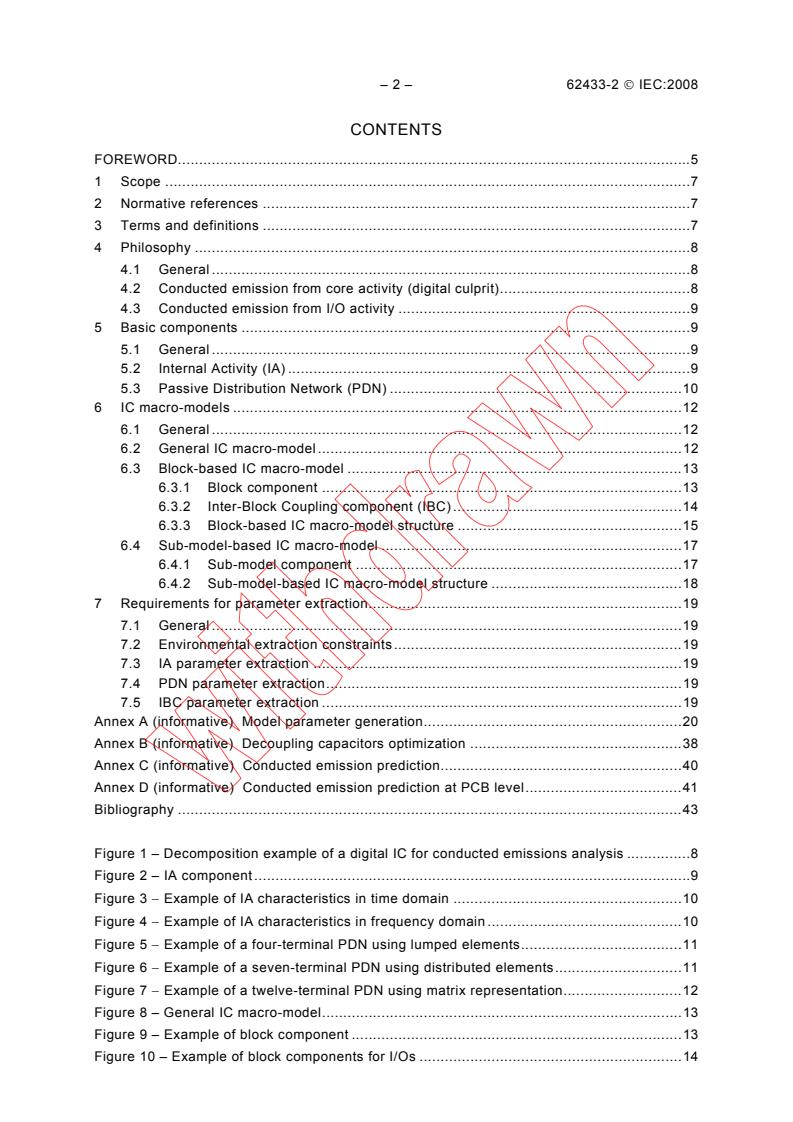

CONTENTS

FOREWORD.5

1 Scope.7

2 Normative references .7

3 Terms and definitions .7

4 Philosophy .8

4.1 General .8

4.2 Conducted emission from core activity (digital culprit) .8

4.3 Conducted emission from I/O activity.9

5 Basic components .9

5.1 General .9

5.2 Internal Activity (IA).9

5.3 Passive Distribution Network (PDN) .10

6 IC macro-models .12

6.1 General .12

6.2 General IC macro-model .12

6.3 Block-based IC macro-model.13

6.3.1 Block component .13

6.3.2 Inter-Block Coupling component (IBC) .14

6.3.3 Block-based IC macro-model structure .15

6.4 Sub-model-based IC macro-model .17

6.4.1 Sub-model component.17

6.4.2 Sub-model-based IC macro-model structure .18

7 Requirements for parameter extraction.19

7.1 General .19

7.2 Environmental extraction constraints .19

7.3 IA parameter extraction .19

7.4 PDN parameter extraction .19

7.5 IBC parameter extraction.19

Annex A (informative) Model parameter generation.20

Annex B (informative) Decoupling capacitors optimization .38

Annex C (informative) Conducted emission prediction.40

Annex D (informative) Conducted emission prediction at PCB level .41

Bibliography.43

Figure 1 – Decomposition example of a digital IC for conducted emissions analysis .8

Figure 2 – IA component.9

Figure 3 − Example of IA characteristics in time domain .10

Figure 4 − Example of IA characteristics in frequency domain.10

Figure 5 − Example of a four-terminal PDN using lumped elements .11

Figure 6 − Example of a seven-terminal PDN using distributed elements .11

Figure 7 − Example of a twelve-terminal PDN using matrix representation .12

Figure 8 – General IC macro-model .13

Figure 9 – Example of block component.13

Figure 10 – Example of block components for I/Os .14

62433-2 © IEC:2008(E) – 3 –

Figure 11 – Example of IBC with two internal terminals.15

Figure 12 – Relationship between blocks and IBC.15

Figure 13 – Block-based IC macro-model.16

Figure 14 – Example of block-based IC macro-model.17

Figure 15 – Example of simple sub-model.18

Figure 16 – Sub-model-based IC macro-model .18

Figure A.1 – Typical characterization current gate schematic.22

Figure A.2 – Current peak during switching transition .22

Figure A.3 – Example of IA extraction procedure from design .23

Figure A.4 – Technology Influence.23

Figure A.5 – Final current waveform for a program period.24

Figure A.6 – Comparison between measurement and simulation.24

Figure A.7 – Lumped element model of a package.25

Figure A.8 – Circuit structure of the netlist .26

Figure A.9 – Principle of the IA computation .27

Figure A.10 – Process involved to model i (t) .27

A

Figure A.11 – i (t) measured using IEC 61967-4.28

Ext

Figure A.12 – i (t)and i (t) profiles .28

A Ext

Figure A.13 – Example of a hardware set-up used to extract the PDN parameters .30

Figure A.14 – Miniature 50 Ω coaxial connectors .30

Figure A.15 – Impedance probe using two miniature coaxial connectors .31

Figure A.16 – Open and short terminations .31

Figure A.17 – Measurement probe model.31

Figure A.18 – De-embedding principle .32

Figure A.19 – Example of a predefined PDN structure .33

Figure A.20 – RL configuration .34

Figure A.21 – RLC configuration .34

Figure A.22 – RLC with magnetic coupling configuration.35

Figure A.23 – Impedance seen from Vcc and Gnd .35

Figure A.24 – Complete PDN component .36

Figure A.25 – Set-up for correlation (left), measurement and prediction (right).37

Figure A.26 – Set-up used to measure the internal decoupling capacitor .37

Figure B.1 – Equivalent schematic of the complete electronic system .38

Figure B.2 – Impedance prediction and measurements .39

Figure C.1 – IEC 61967-4 test set-up standard .40

Figure C.2 – Comparison between prediction and measurement .40

Figure D.1 – Prediction of the Vdcc noise level at PCB level.41

Figure D.2 – Good agreements on the noise envelope .42

– 4 – 62433-2 © IEC:2008(E)

Table A.1 – Typical parameters for CMOS logic technologies .20

Table A.2 – Typical number of logic gates vs. CPU technology .21

Table A.3 – R, L and C parameters for various package types .21

Table A.4 – Measurement configurations and extracted RLC parameters.33

62433-2 © IEC:2008(E) – 5 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

EMC IC MODELLING –

Part 2: Models of integrated circuits for EMI behavioural simulation –

Conducted emissions modelling (ICEM-CE)

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any

equipment declared to be in conformity with an IEC Publication.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 62433-2 has been prepared by subcommittee 47A: Integrated

circuits, of IEC technical committee 47: Semiconductor devices.

The text of this standard is based on the following documents:

FDIS Report on voting

47A/794/FDIS 47A/799/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all the parts in the IEC 62433 series, under the general title EMC IC modelling, can

be found on the IEC website.

– 6 – 62433-2 © IEC:2008(E)

The committee has decided that the contents of this publication will remain unchanged until

the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in

the data related to the specific publication. At this date, the publication will be

• reconfirmed,

• withdrawn,

• replaced by a revised edition, or

• amended.

A bilingual version of this publication may be issued at a later date.

62433-2 © IEC:2008(E) – 7 –

EMC IC MODELLING –

Part 2: Models of integrated circuits for EMI behavioural simulation –

Conducted emissions modelling (ICEM-CE)

1 Scope

This part of IEC 62433 specifies macro-models for ICs to simulate conducted electromagnetic

emissions on a printed circuit board. The model is commonly called Integrated Circuit

Emission Model - Conducted Emission (ICEM-CE).

The ICEM-CE model can also be used for modelling an IC-die, a functional block and an

Intellectual Property block (IP).

The ICEM-CE model can be used to model both digital and analogue ICs.

Basically, conducted emissions have two origins:

• conducted emissions through power supply terminals and ground reference structures;

• conducted emissions through input/output (I/O) terminals.

The ICEM-CE model addresses those two types of origins in a single approach.

This standard defines structures and components of the macro-model for EMI simulation

taking into account the IC’s internal activities.

This standard gives general data, which can be implemented in different formats or languages

such as IBIS, IMIC, SPICE, VHDL-AMS and Verilog. SPICE is however chosen as default

simulation environment to cover all the conducted emissions.

This standard also specifies requirements for information that shall be incorporated in each

ICEM-CE model or component part of the model for model circulation, but description syntax

is not within the scope of this standard.

2 Normative references

The following referenced documents are indispensable for the application of this document.

For dated references, only the edition cited applies. For undated references, the latest edition

of the referenced document (including any amendments) applies.

IEC 61967 (all parts), Integrated Circuits – Measurement of electromagnetic emissions, 150

KHz to 1 GHz

IEC 61967-4, Integrated circuits – Measurement of electromagnetic emissions, 150 kHz to 1

GHz – Part 4: Measurement of conducted emissions – 1 Ω/150 Ω direct coupling method

3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

– 8 – 62433-2 © IEC:2008(E)

3.1

external terminal

terminal of an IC macro-model, which interfaces the model to the external environment of the

IC, such as power supply pins and I/O pins

NOTE In this document, the name of each external terminal starts with "ET".

3.2

internal terminal

terminal of an IC macro-model's component, which interfaces the component to other

components of the IC macro-model

NOTE In this document, the name of each internal terminal starts with "IT".

4 Philosophy

4.1 General

Integrated circuits will have more and more gates on silicon and technical progress will

develop faster. To predict the electromagnetic behaviour of equipment, it is required to model

the switching of the input and output interface and the internal activities of an integrated

circuit effectively.

Figure 1 depicts an example of decomposition of an IC to enable conducted emissions

analysis. The internal digital activity (culprit) is a source of electromagnetic noise that

originates in switching of active devices. The coupling path propagates the emissions to the

IC’s external terminals: pins/pads. The coupling path is the power distribution network or I/O

lines inside the IC.

Power Distribution

Network

Vdd Vss Vdd Vss

Digital Culprit

Digital Coupling I/Os' Coupling I/Os' Culprit

(Emission

path path (Emission Source)

Source)

IC

Inter Block Coupling Path

I/O

IEC 1644/08

Figure 1 – Decomposition example of a digital IC for conducted emissions analysis

4.2 Conducted emission from core activity (digital culprit)

The current transients are created in the core area on the IC-die. Due to the characteristics of

the digital coupling paths, the passive distribution network on printed circuit board (PCB) and

the availability of on-chip decoupling, a portion of these current transients will occur at the

power supply pins of the IC.

62433-2 © IEC:2008(E) – 9 –

NOTE These off-chip power supply currents can be measured according to the IEC 61967 series.

4.3 Conducted emission from I/O activity

I/Os activities may create voltage fluctuations of power and ground levels, and conducted

emissions appear at power and ground pins through the I/Os' coupling path. And the output

signals at output pins themselves are sources of conducted emissions to the printed circuit

boards.

NOTE The measurement set-up is done according to the IEC 61967 series.

5 Basic components

5.1 General

The basic components are component parts of the IC macro-model or block component or

sub-model component. The following subclauses define the basic components.

NOTE The block component and the sub-model component are defined in Subclause 6.3.1 and 6.4.1 respectively.

5.2 Internal Activity (IA)

The Internal Activity (IA) component is the electromagnetic noise source that originates in

switching of active devices in the IC or in a portion of the IC. This component is applicable for

both analogue and digital circuitry.

The IA is described using an independent current source or an independent voltage source

with two internal terminals as shown in Figure 2.

ITITAA--[[00]]

ITITAA++[[00]]

IEC 1645/08

Figure 2 – IA component

The characteristics of IA component are typically described in the time domain, and the

characteristics can also be described in the frequency domain.

The description of an IA component shall contain the following information.

• Name of the IA component

• Names of its internal terminals

• Operational mode or test vector

• Domain (time or frequency)

• Definition of origin of time, and cycle-time for the operational mode (for time domain)

• Definition of origin of phase (for frequency domain)

• Operational conditions and applicable ranges

a) Power supply voltage ranges

b) Temperature range

– 10 – 62433-2 © IEC:2008(E)

c) Frequency range

• Characteristics of the IA

a) Current or voltage waveform over the whole cycle-time (for time domain)

b) Current or voltage amplitude and phase, versus frequency over the whole frequency

range (for frequency domain)

EXAMPLE 1

Figure 3 shows an example of characteristics of IA in the time domain. The waveform

depends on the specific operational mode of function. A simple waveform such as a triangular

waveform can be used for the component description.

i (A)

time (s)

IEC 1646/08

Figure 3 − Example of IA characteristics in the time domain

EXAMPLE 2

Figure 4 shows an example of characteristics of IA in the frequency domain.

I (dBµA)

f (Hz)

IEC 1647/08

Figure 4 − Example of IA characteristics in the frequency domain

5.3 Passive Distribution Network (PDN)

The Passive Distribution Network component (PDN) presents the characteristics of

propagation path of electromagnetic noises such as power distribution network (part of the

PDN). The PDN can be linear or non-linear.

62433-2 © IEC:2008(E) – 11 –

The PDN consists of passive elements, and is equipped with internal terminals. And the PDN

can have external terminals.

The PDN can be described using a netlist. In the case the PDN can be assumed to be linear,

some matrix formats such as the S-parameter can also present the PDN characteristics.

The description of a PDN component shall contain the following information.

• Name of the PDN component

• Names of its internal terminals and external terminals

• Applicable ranges

a) Power supply voltage range

b) Temperature range

c) Applicable load conditions if the PDN is for output

d) Applicable frequency range

• Characteristics of the PDN

EXAMPLE 1

Figure 5 shows an example of a four-terminal PDN using lumped elements. The ETVdd and

ETVss are two external terminals of the PDN. The IT[1] and the IT[0] are two internal

terminals.

ITIT[[11]] ITIT[[00]]

PDPDNN

ETETVVdddd ETETVVssss

IEC 1648/08

Figure 5 − Example of a four-terminal PDN using lumped elements

EXAMPLE 2

Figure 6 depicts the seven-terminal PDN structure using distributed elements such as

transmission lines. The ETVxx are the four external terminals, the ITVxx are two internal

terminals and the ETGnd is the common ground of the four transmission lines, connected to

the PCB ground.

PDPDNN

EETTVVdd[dd[00]] IITTVVdd[dd[0]0]

IITTVVss[ss[00]]

EETTVVss[ss[00]]

EETTVVdd[dd[11]]

EETTVVss[ss[11]]

ETETGGnndd

IEC 1649/08

Figure 6 − Example of a seven-terminal PDN using distributed elements

– 12 – 62433-2 © IEC:2008(E)

EXAMPLE 3

Figure 7 shows an example of a twelve-terminal PDN using scattering parameters in a matrix

format (black box). The ET[x] are external terminals. The IT[1] to IT[6] are internal terminals.

A ground plane below the modelled IC is taken as an ideal reference ground for these

terminals.

ETET[[11]]

IT[IT[11]]

S1S111 -- -- -- -- SS1 121 12

ETET[[22]]

IT[IT[22]]

---- --------

---- --------

ETET[[33]]

IT[IT[33]]

ETET[[44]] ---- --------

IT[IT[44]]

---- --------

ETET[[55]]

IT[IT[55]]

SS12 112 1 -- -- -- -- SS12 1212 12

ETET[[66]]

IT[IT[66]]

IEC 1650/08

Figure 7 − Example of a twelve-terminal PDN using matrix representation

6 IC macro-models

6.1 General

An IC is modelled as an IC macro-model. Three types of IC macro-models, general model,

block-based model and sub-model-based model, are possible. These IC macro-models are

defined in this subclause.

The description of an IC macro-model shall contain the following information for model

circulation.

• Name of the IC macro-model

• Type of the model, general model or block-based model or sub-model-based model

• Names of components that are included in the IC macro-model

• Names of its external terminals

• Connections of the internal terminals of its components

6.2 General IC macro-model

The general model consists of a single PDN and one or more IAs as shown in Figure 8. The

PDN shall include both the whole PDN on the IC die(s) and the whole PDN of the package. An

on-chip decoupling capacitor shall also be included in the PDN if it exists.

NOTE This structure is suitable for the model circulation to IC users because of the least disclosure of proprietary

information of the IC vendor.

62433-2 © IEC:2008(E) – 13 –

IICC m modelodel

IAIA

IAIA IAIA

IT[6IT[6]] IITT[[77]] IT[8IT[8]] IIT[T[99]] IITT[1[100]] IT[1IT[111]]

IT[0IT[0]] IITT[[11]] IT[2IT[2]] IIT[T[33]] ITIT[4[4]] IIT[5T[5]]

PDPDNN

ET[ET[00]] ETET[1][1]

ET[4]ET[4] EET[T[5]5] ETET[[88]] ETET[[99]]

ET[ET[22]] EETT[[3]3]

ETET[[66]] EETT[[77]]

ETET[[110]0] ETET[[11]11] ETET[14][14] ET[ET[115]5]

ET[ET[118]8] EETT[[119]9]

ETET[12][12] ETET[13][13]

ET[ET[116]6] ET[ET[117]7]

PPDN ofDN of P PCCB B ((outout of of t thhe e scope)scope)

IEC 1651/08

Figure 8 – General IC macro-model

6.3 Block-based IC macro-model

6.3.1 Block component

The block component represents EMC properties of a specific functional block of IC such as

embedded memory.

The block component consists of a single PDN and one or more IAs. The PDN includes PDN

of the specific functional block, a portion of global power/ground network and a portion of

package PDN, which are directly involved into the block's functionality. The on-chip

decoupling capacitor is a part of the PDN. The component is equipped with external terminals

and internal terminals.

The description of a block component shall include the following information.

• Name of the block component

• Names of the basic components that make up the block component

• Connections of the internal terminals of its basic components

EXAMPLE 1

Figure 9 shows an example of block component. The block consists of an IA and a PDN. The

internal terminals of the IA are connected to the internal terminals of the PDN.

PDPDPDPDNNNN E E E Exxxxamamamampppplllleeee

ITITITIT[[[[1111]]]] ITITITIT[[[[3333]]]]

IAIAIAIA E E E Exxxxaaaammmmpppplelelele

ETETETET[[[[1111]]]] ITITITIT[[[[1111]]]]

ITITITIT[3[3[3[3]]]]

RVRVRVRVdddddddd

LVLVLVLVdddddddd

PDPDPDPDNNNN IAIAIAIA

CoCoCoCommmmppppoooonnnneeeennnntttt

CCCComomomomponponponponeeeentntntnt

ETETETET[[[[0000]]]] ITITITIT[0[0[0[0]]]]

RRRRVVVVssssssss LLLLVVVVssssssss CCCCVVVVdddddddd

ITITITIT[[[[0000]]]] ITITITIT[[[[2222]]]]

ITITITIT[[[[2222]]]]

ETETETET[[[[1111]]]]

ETETETET[[[[0000]]]]

PPPPDDDDNNNN & & & & I I I IAAAA IC IC IC ICEEEEMMMM C C C Coooommmmppppoooonnnneeeennnnttttssss

IEC 1652/08

Figure 9 – Example of block component

– 14 – 62433-2 © IEC:2008(E)

EXAMPLE 2

Figure 10 depicts a three I/Os model. The I/OPDN component describes how I/Os are

powered and the I/OPDNA describes noise transfer characteristics among terminals. The

I/OIA components describe the current activity. They are built up using two IA components;

one to specify the high state behaviour and the other one to specify the low state. Figure 10

shows the two types of I/O PDN components of the complete I/O model. The IBIS model could

be an implementation example.

I/OPDN I/OIA

I/OPDNA

Component Component Internal Ports Component

Inter nal Ports

IA[2]

ITVdd[n]

ETP[2]

IA[1]

I/Os PDN Access

ETP[1]

ITVss[]n

IA[0]

Passive Distribution ETP[0]

Internal

Network of I/Os

ITOut0 0

[]

Activity

ITVdd 0 ITVdd 0

[] [ ]

ITVss 0

ITVss[0] []

I/O ICEM-CE Model

ETP_Vdd

ETP_Vss

ITVdd 0

[ ]

IAHigh

ITOut0 0

[ ]

ITVss 0

[]

IALow

IEC 1653/08

Figure 10 – Example of block components for I/Os

6.3.2 Inter-Block Coupling component (IBC)

The Inter-Block Coupling (IBC) is a network of passive elements that presents a coupling

effect between blocks. The IBC is equipped with two or more internal terminals.

The description of an IBC component shall contain the following information.

• Name of the IBC

• Names of its internal terminals

• Applicable ranges

a) Power supply voltage ranges

b) Temperature range

c) Applicable frequency range

• Characteristics of the IBC

62433-2 © IEC:2008(E) – 15 –

EXAMPLE

Figure 11 shows an example of IBC. The relationship between the block and the IBC is shown

in Figure 12.

IBIBCC

IEC 1654/08

Figure 11 – Example of IBC with two internal terminals

IC macro-model

ITIBC[1] ITIBC[0]

Inter-Block

ITIBC[2]

Coupling ITIBC[3]

Analogue Block

I/O Digital Block I/O

IEC 1655/08

Figure 12 – Relationship between blocks and IBC

6.3.3 Block-based IC macro-model structure

The block-based structure is shown in Figure 13. The model consists of block components

and IBC components. The PDN of global wiring on die and the PDN on package are

incorporated into the PDNs of blocks.

NOTE 1 This structure is suitable for modelling from measurements.

NOTE 2 By combining PDNs of block and IBCs, this structure can be converted into general structure.

ETVdd

ETVss

ETVcc

ETVee

– 16 – 62433-2 © IEC:2008(E)

ICIC m moodedell

ICICEMEM-C-CE BE Blloock Ack A IICCEEM-CM-CE E BlBloock Bck B IICCEMEM--CCE BE Blloock Cck C

IAIA IAIA

IAIA

ITIT[6][6] IIT[7T[7]] ITIT[8[8]] IITT[[99]] ITIT[1[100]] ITIT[1[111]]

ITIT[0][0] IIT[1T[1]] ITIT[2[2]] IITT[[33]] ITIT[4][4] IITT[[55]]

ITIT[[12]12] IIT[T[15]15] ITIT[1[166]] ITIT[1[199]]

PDPDNN PDPDNN PDPDNN

IBCIBC IBCIBC

((iincnclluuddiingng P PKKGG)) ((iincludincluding PKGng PKG)) ((iincludincluding PKng PKGG))

ITIT[[13]13] IIT[T[14]14] ITIT[1[177]] ITIT[1[188]]

ETET[0[0]] ETET[[11]] ET[ET[44]] EET[T[5]5]

ETET[8[8]]

ETET[[22]] ETET[[33]] ET[ET[66]] EET[T[7]7]

ETET[9[9]] EETT[[10]10]

EETT[[13]13] EETT[[14]14]

ET[ET[117]7]

ET[ET[1111]] ETET[1[12]2]

EETT[[15]15] ET[ET[16]16]

PPDN ofDN of PC PCBB (o(outut of of th the e ssccopope)e)

IEC 1656/08

Figure 13 – Block-based IC macro-model

EXAMPLE

Figure 14 depicts an example of block-based IC macro-model. Each block has two external

terminals and three internal terminals. Three IBC blocks interconnect the internal terminals,

IT2, IT3, IT4, IT5 and IT6. In this example, IBCs are used to model the substrate coupling

caused by the sheet resistance between the three internal ground terminals.

62433-2 © IEC:2008(E) – 17 –

AVCC AVSS

ICEM Model ET4 ET5

Digital ICEM Block Analogue ICEM Block

IT0 Analogue

IT7

Digital IA Analogue PDN

IA

Component Component

Component

IT1

IT8

IT3 IT4

IBC1

Digital PDN

IT2 IBC2

Component

IBC0

IT6

IT5

I/Os' ICEM Block

IT9

I/Os' IA

IOs PDN

Component

IOs ICEM

Component

Model

IT10

ET0 ET1 ET2 ET3

VCC1

VSS1

VCC2 VSS2

IEC 1657/08

Figure 14 – Example of block-based IC macro-model

6.4 Sub-model-based IC macro-model

6.4.1 Sub-model component

The sub-model in Figure 16 represents the electromagnetic behaviour of specific functional

circuits of IC. An intellectual property (IP) shall be modelled as a sub-model, and some

specific functional circuits such as embedded memory and CPU core can be modelled using

the sub-model. The sub-model can be repeatedly used in the IC and/or other ICs.

The sub-model consists of a single PDN and one or more IAs. This PDN is a PDN of the

specific functional circuits. The sub-model is equipped with internal terminals but does not

have any external terminals.

The sub-model description shall contain the following information.

• Name of the sub-model

• Names of its internal terminals

• Names of the basic components that are included in the sub-model

• Connections of the internal terminals of basic components

– 18 – 62433-2 © IEC:2008(E)

EXAMPLE

Figure 15 shows a simple sub-model example.

ITIT[1[1]] ITIT[3][3]

IAIA

PDPDNN

CoCommppoonneenntt

CoCommppoonneenntt

ITIT[0][0] ITIT[2][2]

ITIT[4][4]

ITIT[[55]]

Figure 15 – Example of simple sub-model

6.4.2 Sub-model-based IC macro-model structure

The sub-model-based structure is shown in Figure 16. It consists of one or more sub-models,

a PDN of die, and a PDN of package. The PDN of die includes the global power/ground

network of IC die and the on-chip decoupling capacitor if it exists, but does not include PDNs

that belong to sub-models. Some IAs such as IAs for standard cell circuits can be directly

connected to the PDN of die (not shown in the figure).

NOTE 1 This structure is suitable for modelling using IC design information.

NOTE 2 By combining PDNs of the whole IC macro-model, a sub-model-based IC macro-model can be converted

into a general IC macro-model.

IC model

Sub-model A Sub-model B Sub-model C

IA

IA IA

IT[6] IT[7] IT[8] IT[9] IT[10] IT[11]

IT[0] IT[1] IT[2] IT[3] IT[4] IT[5]

PDN PDN PDN

IT[20] IT[21] IT[22] IT[23] IT[24] IT[25] IT[26] IT[27]

IT[12] IT[13] IT[14] IT[15] IT[16] IT[17] IT[18] IT[19]

PDN of die excluding sub-models

IT[36] IT[37] IT[38] IT[39] IT[40] IT[41] IT[42] IT[43]

IT[28] IT[29] IT[30] IT[31] IT[32] IT[33] IT[34] IT[35]

PDN of die package

ET[0] ET[1]

ET[4] ET[5] ET[8] ET[9]

ET[2] ET[3]

ET[6] ET[7]

ET[10] ET[11]

ET[14] ET[15]

ET[18] ET[19]

ET[12] ET[13]

ET[16] ET[17]

PDN of PCB (out of the scope)

IEC 1659/08

Figure 16 – Sub-model-based IC macro-model

62433-2 © IEC:2008(E) – 19 –

7 Requirements for parameter extraction

7.1 General

ICEM-CE model parameters can be extracted from either design information or measurements.

Detailed methodology for model parameter extractions are not the purpose of this standard.

This clause gives basic requirements for model parameter extractions from measurements.

NOTE Annex A gives examples of parameter extractions from design information and from measurements.

7.2 Environmental extraction constraints

The ICEM macro-model parameter extractions have to be performed under normal room

temperature conditions: 23 °C ± 5 °C. There are no additional requirements on air pressure

and humidity.

When open silicon is used, the lights shall be dimmed or switched off in order not to generate

photonic effects.

NOTE Some substrate materials are hydroscopic which might affect the permittivity of the material and its loss

tangent.

7.3 IA parameter extraction

IA can be derived by design data or by calculating by measurements under the following

conditions:

• Nominal power supply voltages and typical loadings shall be applied to the device under

test.

• Input signals such as specific test vector which correspond to the specific operational

mode shall be applied.

7.4 PDN parameter extraction

The PDN parameters shall be derived by analyzing impedances between the terminals under

the nominal power supplies.

The derived parameters are only suited and re-useable for conducted emission simulations

when the PVT (process, voltage and temperature) conditions are the same.

NOTE 1 PDN is static, but due to the N-well and gate-oxide capacitances that are involved, the power supply

voltage will affect it.

NOTE 2 Most of the impedance parameters can be derived from measurements using an impedance analyzer of

S-parameter VNA (Vector Network Analyser)

7.5 IBC parameter extraction

The IBC impedance can be derived from the Vdd to Vss impedance by subtracting the

impedance part that belongs to the PDN. A detailed method should be elaborated in future.

– 20 – 62433-2 © IEC:2008(E)

Annex A

(informative)

Model parameter generation

A.1 Introduction

The purpose of this annex is to explain the methodologies used to extract the components.

Three different ways are possible:

• Default parameters can be used when no other data is available.

• Parameters derived from parasitic element extractor tools, which can be used at the

design phase of the IC and/or 3D electromagnetic field simulator.

• Parameters derived from measurements when the IC is already available.

A.2 Default structure and values

A.2.1 General

The PDN and IA components can be obtained using technological data coming from the IC

and the packaging suppliers. The accuracy of default values is relatively low compared to

values obtained by measurements or design information.

A.2.2 IA parameters

The IA structure is shown in Figure 2. It is possible to quickly determine the IA component

using the technological data, which can be obtained from IC suppliers. Table A.1 shows

typical values of the parameters.

As an example, for 0,5 μm ASIC technology, cell density is around 7000. The probable

number of cells in 3×3 mm area is approximately 7,000 × 9 = 63 k gates. Considering that in

average 10 % of cells are switching simultaneously, the probable CPU current at each clock

edge is 63 k gates × 10 % × 0,75 mA = 4725 mA.

Table A.1 – Typical parameters for CMOS logic technologies

Technology Year Power Cell density Clock frequency Peak gate current Rise/Fall

CMOS supply time

V /mm MHz mA/gate ns

1985 5 1500 4 to 50 1,1 0,7

1,2μm

1990 5 4000 4 to 90 0,9 0,5

0,8μm

1993 5 7000 8 to 120 0,75 0,3

0,5μm

1995 5 to 3,3 13000 16 to 300 0,6 0,2

0,35μm

1997 5 to 2,5 18000 40 to 450 0,4 0,12

0,25μm

1999 3,3 to 2,0 22000 100 to 900 0,3 0,1

0,18μm

0,12μm 2001 2,5 to 1,2 28500 150 to 1200 0,2 0,07

Table A.2 gives the default number of logic gates for typical microcontrollers.

As an example, a 16-bit RISC microcontroller is fabricated in 0,25μm technology. The

microcontroller has approximately 15000 gates. The probable CPU current at each clock edge

is 15000 × 10 % × 0,4 mA = 600 mA. The rise and fall time of the peak current is 0,12 ns.

62433-2 © IEC:2008(E) – 21 –

Table A.2 – Typical number of logic gates vs. CPU technology

CPU technology Total number of logic cells Synchronous switching

on clock edge

8 bits CISC 3000 to 5000 300 to 500

8 bits RISC 3000 to 5000 300 to 500

16 bits CISC 15000 to 20000 1500 to 2000

16 bits RISC 12000 to 18000 1200 to 1800

32 bits CISC 40000 to 60000 4000 to 6000

32 bits RISC 40000 to 60000 4000 to 6000

A.2.3 PDN parameters

The default structure of PDN is given in Figure 5.

The technological data given by the package suppliers enable to build quickly a PDN

component. The typical values of the R, L and C are summarized in Table A.3. These values

are used for the frequency range from DC to approximately 1 GHz.

Table A.3 – R, L and C parameters for various package types

Package Pin count R L C

Dual in Line 64 pins 0,025 Ω to 0,075 Ω 2 nH to 1 pF to

(DIL) 15 nH 10 pF

Shrink dual in line 64 pins 0,025 Ω to 0,1 Ω 1 nH to 1 pF to

(SDIL) 10 nH 10 pF

Small Outline 64 pins 0,025 Ω to 0,05 Ω 1 nH to 1 pF to

Package 7 nH 7 pF

(SOP)

Quad Flat Pack 400 pins 0,035 Ω to 0,55 Ω 3 nH to 2 pF to

(QFP) 7 nH 5 pF

Ball Grid Array 800 pins 0,05 Ω to 0,15 Ω 0,5 nH to 1 pF to

(BGA) 10 nH 10 pF

Fine Pitch Ball Grid 1500 pins 0,05 Ω to 0,2 Ω 0,5 nH to 1 pF to

Array 10 nH 20 pF

(FBGA)

Mould Chip Scale 1500 pins 0,025 Ω to 0,1 Ω 0,5 nH to 1 pF to

Package 5 nH 15 pF

(MCSP)

A.3 Model parameter generation from design information

A.3.1 General

ICs suppliers can extract parameters from their design information using IC design tools.

– 22 – 62433-2 © IEC:2008(E)

A.3.2 IA parameters

The current source is the main component in the ICEM-CE model: it summarizes the

contribution of all the logic gates on the current flowing through the power supply pins of the

component. The behavioural simulation is a statistical approach that could be done at the

early stage of the design flow (no need of the layout for example), and could take into account

a very important numbers of gates. The way to build the current source is based on a

statistical evaluation of the core elements: choice of the more representative gate (the most

frequently-used gate in the design), choice of the typical load of the gate. From this

information, a simulation can be done at the circuit level to extract the consumption current of

the typical gate. For example, in a particular 16-bit micro-controller, the most popular gate is

an inverter. Figure A.1 illustrates the test schematic to define the typical current waveform.

RRRR

TTyyppiical gatcal gatee

R1R1R1R1ohohohoh

RR

RR On-chip

RR

RR

decoupling

mmmm

C C load /5

ClocClockk 1

CurCurrreenn

CCLLKKBBUUFFXX chain chain ((

to VDto VDD)D)

PowPoweerr

tt

QuQuickick clo clocckk

CCtytypp

TyTypipiccaall

load

C C

R1R1R1R1ohohohoh

RR RR

RR RR

mmmm

LocLocaall R & CR & Cdec dec RR

GlobaGloball R R & C& Cdecdec RR

IAIA

LocLocaall R & CR & Cdec dec

IEC 1660/08

Figure A.1 – Typical characterization current gate schematic

This example shows the description of the PDN, local and distributed on-chip decoupling

networks, and the description of the IA. As the inverter has a non-symmetric structure, the

current peak is not the same for the switching-on and the switching-off: the average between

these two current waveforms is therefore required i

...

IEC 62433-2 ®

Edition 1.0 2008-10

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

EMC IC modelling –

Part 2: Models of integrated circuits for EMI behavioural simulation – Conducted

emissions modelling (ICEM-CE)

Modèles de circuits intégrés pour la CEM –

Partie 2: Modèles de circuits intégrés pour la simulation du comportement lors

de perturbations électromagnétiques – Modélisation des émissions conduites

(ICEM-CE)

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form

or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from

either IEC or IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication,

please contact the address below or your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite ni

utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et les

microfilms, sans l'accord écrit de la CEI ou du Comité national de la CEI du pays du demandeur.

Si vous avez des questions sur le copyright de la CEI ou si vous désirez obtenir des droits supplémentaires sur cette

publication, utilisez les coordonnées ci-après ou contactez le Comité national de la CEI de votre pays de résidence.

IEC Central Office Tel.: +41 22 919 02 11

3, rue de Varembé Fax: +41 22 919 03 00

CH-1211 Geneva 20 info@iec.ch

Switzerland www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

Useful links:

IEC publications search - www.iec.ch/searchpub Electropedia - www.electropedia.org

The advanced search enables you to find IEC publications The world's leading online dictionary of electronic and

by a variety of criteria (reference number, text, technical electrical terms containing more than 30 000 terms and

committee,…). definitions in English and French, with equivalent terms in

It also gives information on projects, replaced and additional languages. Also known as the International

withdrawn publications. Electrotechnical Vocabulary (IEV) on-line.

IEC Just Published - webstore.iec.ch/justpublished Customer Service Centre - webstore.iec.ch/csc

Stay up to date on all new IEC publications. Just Published If you wish to give us your feedback on this publication

details all new publications released. Available on-line and or need further assistance, please contact the

also once a month by email. Customer Service Centre: csc@iec.ch.

A propos de la CEI

La Commission Electrotechnique Internationale (CEI) est la première organisation mondiale qui élabore et publie des

Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications CEI

Le contenu technique des publications de la CEI est constamment revu. Veuillez vous assurer que vous possédez

l’édition la plus récente, un corrigendum ou amendement peut avoir été publié.

Liens utiles:

Recherche de publications CEI - www.iec.ch/searchpub Electropedia - www.electropedia.org

La recherche avancée vous permet de trouver des Le premier dictionnaire en ligne au monde de termes

publications CEI en utilisant différents critères (numéro de électroniques et électriques. Il contient plus de 30 000

référence, texte, comité d’études,…). termes et définitions en anglais et en français, ainsi que

Elle donne aussi des informations sur les projets et les les termes équivalents dans les langues additionnelles.

publications remplacées ou retirées. Egalement appelé Vocabulaire Electrotechnique

International (VEI) en ligne.

Just Published CEI - webstore.iec.ch/justpublished

Service Clients - webstore.iec.ch/csc

Restez informé sur les nouvelles publications de la CEI.

Just Published détaille les nouvelles publications parues. Si vous désirez nous donner des commentaires sur

Disponible en ligne et aussi une fois par mois par email. cette publication ou si vous avez des questions

contactez-nous: csc@iec.ch.

IEC 62433-2 ®

Edition 1.0 2008-10

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

EMC IC modelling –

Part 2: Models of integrated circuits for EMI behavioural simulation – Conducted

emissions modelling (ICEM-CE)

Modèles de circuits intégrés pour la CEM –

Partie 2: Modèles de circuits intégrés pour la simulation du comportement lors

de perturbations électromagnétiques – Modélisation des émissions conduites

(ICEM-CE)

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION

ELECTROTECHNIQUE

PRICE CODE

INTERNATIONALE

CODE PRIX X

ICS 31.200 ISBN 978-2-83220-593-8

– 2 – 62433-2 IEC:2008

CONTENTS

FOREWORD. 5

1 Scope . 7

2 Normative references . 7

3 Terms and definitions . 7

4 Philosophy . 8

4.1 General . 8

4.2 Conducted emission from core activity (digital culprit) . 8

4.3 Conducted emission from I/O activity . 9

5 Basic components . 9

5.1 General . 9

5.2 Internal Activity (IA) . 9

5.3 Passive Distribution Network (PDN) . 10

6 IC macro-models . 12

6.1 General . 12

6.2 General IC macro-model . 12

6.3 Block-based IC macro-model . 13

6.3.1 Block component . 13

6.3.2 Inter-Block Coupling component (IBC) . 14

6.3.3 Block-based IC macro-model structure . 15

6.4 Sub-model-based IC macro-model . 17

6.4.1 Sub-model component . 17

6.4.2 Sub-model-based IC macro-model structure . 18

7 Requirements for parameter extraction . 19

7.1 General . 19

7.2 Environmental extraction constraints . 19

7.3 IA parameter extraction . 19

7.4 PDN parameter extraction . 19

7.5 IBC parameter extraction . 19

Annex A (informative) Model parameter generation . 20

Annex B (informative) Decoupling capacitors optimization . 38

Annex C (informative) Conducted emission prediction . 40

Annex D (informative) Conducted emission prediction at PCB level . 41

Bibliography . . 43

Figure 1 – Decomposition example of a digital IC for conducted emissions analysis . 8

Figure 2 – IA component . 9

Figure 3 Example of IA characteristics in time domain . 10

Figure 4 Example of IA characteristics in frequency domain . 10

Figure 5 Example of a four-terminal PDN using lumped elements . 11

Figure 6 Example of a seven-terminal PDN using distributed elements . 11

Figure 7 Example of a twelve-terminal PDN using matrix representation . 12

Figure 8 – General IC macro-model . 13

Figure 9 – Example of block component . 13

Figure 10 – Example of block components for I/Os . 14

62433-2 IEC:2008 – 3 –

Figure 11 – Example of IBC with two internal terminals . 15

Figure 12 – Relationship between blocks and IBC . 15

Figure 13 – Block-based IC macro-model . 16

Figure 14 – Example of block-based IC macro-model . 17

Figure 15 – Example of simple sub-model . 18

Figure 16 – Sub-model-based IC macro-model . 18

Figure A.1 – Typical characterization current gate schematic . 22

Figure A.2 – Current peak during switching transition . 22

Figure A.3 – Example of IA extraction procedure from design . 23

Figure A.4 – Technology Influence . 23

Figure A.5 – Final current waveform for a program period . 24

Figure A.6 – Comparison between measurement and simulation . 24

Figure A.7 – Lumped element model of a package . 25

Figure A.8 – Circuit structure of the netlist . 26

Figure A.9 – Principle of the IA computation . 27

Figure A.10 – Process involved to model i (t) . 27

A

Figure A.11 – i (t) measured using IEC 61967-4 . 28

Ext

Figure A.12 – i (t)and i (t) profiles . 28

A Ext

Figure A.13 – Example of a hardware set-up used to extract the PDN parameters . 30

Figure A.14 – Miniature 50 Ω coaxial connectors . 30

Figure A.15 – Impedance probe using two miniature coaxial connectors . 31

Figure A.16 – Open and short terminations . 31

Figure A.17 – Measurement probe model . 31

Figure A.18 – De-embedding principle . 32

Figure A.19 – Example of a predefined PDN structure . 33

Figure A.20 – RL configuration . 34

Figure A.21 – RLC configuration . 34

Figure A.22 – RLC with magnetic coupling configuration . 35

Figure A.23 – Impedance seen from Vcc and Gnd . 35

Figure A.24 – Complete PDN component . 36

Figure A.25 – Set-up for correlation (left), measurement and prediction (right) . 37

Figure A.26 – Set-up used to measure the internal decoupling capacitor . 37

Figure B.1 – Equivalent schematic of the complete electronic system . 38

Figure B.2 – Impedance prediction and measurements . 39

Figure C.1 – IEC 61967-4 test set-up standard . 40

Figure C.2 – Comparison between prediction and measurement . 40

Figure D.1 – Prediction of the Vdcc noise level at PCB level . 41

Figure D.2 – Good agreements on the noise envelope . 42

– 4 – 62433-2 IEC:2008

Table A.1 – Typical parameters for CMOS logic technologies . 20

Table A.2 – Typical number of logic gates vs. CPU technology . 21

Table A.3 – R, L and C parameters for various package types . 21

Table A.4 – Measurement configurations and extracted RLC parameters . 33

62433-2 IEC:2008 – 5 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

EMC IC MODELLING –

Part 2: Models of integrated circuits for EMI behavioural simulation –

Conducted emissions modelling (ICEM-CE)

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any

equipment declared to be in conformity with an IEC Publication.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 62433-2 has been prepared by subcommittee 47A: Integrated

circuits, of IEC technical committee 47: Semiconductor devices.

This bilingual version (2013-01) corresponds to the monolingual English version, published in

2008-10.

The text of this standard is based on the following documents:

FDIS Report on voting

47A/794/FDIS 47A/799/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

The French version of this standard has not been voted upon.

– 6 – 62433-2 IEC:2008

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all the parts in the IEC 62433 series, under the general title EMC IC modelling, can

be found on the IEC website.

The committee has decided that the contents of this publication will remain unchanged until

the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in

the data related to the specific publication. At this date, the publication will be

• reconfirmed,

• withdrawn,

• replaced by a revised edition, or

• amended.

IMPORTANT – The “colour inside” logo on the cover page of this publication indicates

that it contains colours which are considered to be useful for the correct understanding

of its contents. Users should therefore print this publication using a colour printer.

62433-2 IEC:2008 – 7 –

EMC IC MODELLING –

Part 2: Models of integrated circuits for EMI behavioural simulation –

Conducted emissions modelling (ICEM-CE)

1 Scope

This part of IEC 62433 specifies macro-models for ICs to simulate conducted electromagnetic

emissions on a printed circuit board. The model is commonly called Integrated Circuit

Emission Model - Conducted Emission (ICEM-CE).

The ICEM-CE model can also be used for modelling an IC-die, a functional block and an

Intellectual Property block (IP).

The ICEM-CE model can be used to model both digital and analogue ICs.

Basically, conducted emissions have two origins:

conducted emissions through power supply terminals and ground reference structures;

conducted emissions through input/output (I/O) terminals.

The ICEM-CE model addresses those two types of origins in a single approach.

This standard defines structures and components of the macro-model for EMI simulation

taking into account the IC’s internal activities.

This standard gives general data, which can be implemented in different formats or languages

such as IBIS, IMIC, SPICE, VHDL-AMS and Verilog. SPICE is however chosen as default

simulation environment to cover all the conducted emissions.

This standard also specifies requirements for information that shall be incorporated in each

ICEM-CE model or component part of the model for model circulation, but description syntax

is not within the scope of this standard.

2 Normative references

The following referenced documents are indispensable for the application of this document.

For dated references, only the edition cited applies. For undated references, the latest edition

of the referenced document (including any amendments) applies.

IEC 61967 (all parts), Integrated Circuits – Measurement of electromagnetic emissions, 150

KHz to 1 GHz

IEC 61967-4, Integrated circuits – Measurement of electromagnetic emissions, 150 kHz to 1

GHz – Part 4: Measurement of conducted emissions – 1 Ω/150 Ω direct coupling method

3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

– 8 – 62433-2 IEC:2008

3.1

external terminal

terminal of an IC macro-model, which interfaces the model to the external environment of the

IC, such as power supply pins and I/O pins

NOTE In this document, the name of each external terminal starts with "ET".

3.2

internal terminal

terminal of an IC macro-model's component, which interfaces the component to other

components of the IC macro-model

NOTE In this document, the name of each internal terminal starts with "IT".

4 Philosophy

4.1 General

Integrated circuits will have more and more gates on silicon and technical progress will

develop faster. To predict the electromagnetic behaviour of equipment, it is required to model

the switching of the input and output interface and the internal activities of an integrated

circuit effectively.

Figure 1 depicts an example of decomposition of an IC to enable conducted emissions

analysis. The internal digital activity (culprit) is a source of electromagnetic noise that

originates in switching of active devices. The coupling path propagates the emissions to the

IC’s external terminals: pins/pads. The coupling path is the power distribution network or I/O

lines inside the IC.

Power Distribution

Network

Vss

Vdd Vss Vdd

Digital Culprit

Digital Coupling I/Os' Coupling I/Os' Culprit

(Emission

path path (Emission Source)

Source)

IC

Inter Block Coupling Path

I/O

IEC 1644/08

Figure 1 – Decomposition example of a digital IC for conducted emissions analysis

4.2 Conducted emission from core activity (digital culprit)

The current transients are created in the core area on the IC-die. Due to the characteristics of

the digital coupling paths, the passive distribution network on printed circuit board (PCB) and

the availability of on-chip decoupling, a portion of these current transients will occur at the

power supply pins of the IC.

62433-2 IEC:2008 – 9 –

NOTE These off-chip power supply currents can be measured according to the IEC 61967 series.

4.3 Conducted emission from I/O activity

I/Os activities may create voltage fluctuations of power and ground levels, and conducted

emissions appear at power and ground pins through the I/Os' coupling path. And the output

signals at output pins themselves are sources of conducted emissions to the printed circuit

boards.

NOTE The measurement set-up is done according to the IEC 61967 series.

5 Basic components

5.1 General

The basic components are component parts of the IC macro-model or block component or

sub-model component. The following subclauses define the basic components.

NOTE The block component and the sub-model component are defined in 6.3.1 and 6.4.1 respectively.

5.2 Internal Activity (IA)

The Internal Activity (IA) component is the electromagnetic noise source that originates in

switching of active devices in the IC or in a portion of the IC. This component is applicable for

both analogue and digital circuitry.

The IA is described using an independent current source or an independent voltage source

with two internal terminals as shown in Figure 2.

ITITAA--[[00]]

ITITAA++[[00]]

IEC 1645/08

Figure 2 – IA component

The characteristics of IA component are typically described in the time domain, and the

characteristics can also be described in the frequency domain.

The description of an IA component shall contain the following information.

Name of the IA component

Names of its internal terminals

Operational mode or test vector

Domain (time or frequency)

Definition of origin of time, and cycle-time for the operational mode (for time domain)

Definition of origin of phase (for frequency domain)

Operational conditions and applicable ranges

a) Power supply voltage ranges

b) Temperature range

– 10 – 62433-2 IEC:2008

c) Frequency range

Characteristics of the IA

a) Current or voltage waveform over the whole cycle-time (for time domain)

b) Current or voltage amplitude and phase, versus frequency over the whole frequency

range (for frequency domain)

EXAMPLE 1

Figure 3 shows an example of characteristics of IA in the time domain. The waveform

depends on the specific operational mode of function. A simple waveform such as a triangular

waveform can be used for the component description.

i (A)

time (s)

IEC 1646/08

Figure 3 Example of IA characteristics in the time domain

EXAMPLE 2

Figure 4 shows an example of characteristics of IA in the frequency domain.

I (dBµA)

f (Hz)

IEC 1647/08

Figure 4 Example of IA characteristics in the frequency domain

5.3 Passive Distribution Network (PDN)

The Passive Distribution Network component (PDN) presents the characteristics of

propagation path of electromagnetic noises such as power distribution network (part of the

PDN). The PDN can be linear or non-linear.

62433-2 IEC:2008 – 11 –

The PDN consists of passive elements, and is equipped with internal terminals. And the PDN

can have external terminals.

The PDN can be described using a netlist. In the case the PDN can be assumed to be linear,

some matrix formats such as the S-parameter can also present the PDN characteristics.

The description of a PDN component shall contain the following information.

Name of the PDN component

Names of its internal terminals and external terminals

Applicable ranges

a) Power supply voltage range

b) Temperature range

c) Applicable load conditions if the PDN is for output

d) Applicable frequency range

Characteristics of the PDN

EXAMPLE 1

Figure 5 shows an example of a four-terminal PDN using lumped elements. The ETVdd and

ETVss are two external terminals of the PDN. The IT[1] and the IT[0] are two internal

terminals.

ITIT[[11]] ITIT[[00]]

PDPDNN

ETETVVdddd EETTVVssss

IEC 1648/08

Figure 5 Example of a four-terminal PDN using lumped elements

EXAMPLE 2

Figure 6 depicts the seven-terminal PDN structure using distributed elements such as

transmission lines. The ETVxx are the four external terminals, the ITVxx are two internal

terminals and the ETGnd is the common ground of the four transmission lines, connected to

the PCB ground.

PDPDNN

EETTVVdd[dd[0]0] IITTVVddd[d[0]0]

ITITVVssss[[00]]

EETTVVss[ss[00]]

EETTVVdd[dd[1]1]

EETTVVss[ss[11]]

ETETGGnndd

IEC 1649/08

Figure 6 Example of a seven-terminal PDN using distributed elements

– 12 – 62433-2 IEC:2008

EXAMPLE 3

Figure 7 shows an example of a twelve-terminal PDN using scattering parameters in a matrix

format (black box). The ET[x] are external terminals. The IT[1] to IT[6] are internal terminals.

A ground plane below the modelled IC is taken as an ideal reference ground for these

terminals.

ETET[[11]]

ITIT[1[1]]

S11S11 -- -- -- -- SS1 121 12

ETET[[22]]

ITIT[2[2]]

---- --------

---- --------

ETET[[33]]

ITIT[3[3]]

ETET[[44]] ---- --------

ITIT[4[4]]

---- --------

ETET[[55]]

ITIT[5[5]]

S12 1S12 1 -- -- -S-S-- 1122 1 122

ETET[[66]]

ITIT[6[6]]

IEC 1650/08

Figure 7 Example of a twelve-terminal PDN using matrix representation

6 IC macro-models

6.1 General

An IC is modelled as an IC macro-model. Three types of IC macro-models, general model,

block-based model and sub-model-based model, are possible. These IC macro-models are

defined in this subclause.

The description of an IC macro-model shall contain the following information for model

circulation.

Name of the IC macro-model

Type of the model, general model or block-based model or sub-model-based model

Names of components that are included in the IC macro-model

Names of its external terminals

Connections of the internal terminals of its components

6.2 General IC macro-model

The general model consists of a single PDN and one or more IAs as shown in Figure 8. The

PDN shall include both the whole PDN on the IC die(s) and the whole PDN of the package. An

on-chip decoupling capacitor shall also be included in the PDN if it exists.

NOTE This structure is suitable for the model circulation to IC users because of the least disclosure of proprietary

information of the IC vendor.

62433-2 IEC:2008 – 13 –

ICIC m modelodel

IAIA