IEC 61691-6:2021

(Main)Behavioural languages - Part 6: VHDL Analog and Mixed-Signal Extensions

Behavioural languages - Part 6: VHDL Analog and Mixed-Signal Extensions

IEC 61691-6:2021(E) defines IEC 61691-6/IEEE Std 1076.1 language, a hardware description language for the description and the simulation of analog, digital, and mixed-signal systems. The language, also informally known as VHDL-AMS, is built on the IEC 61691-1-1/IEEE 1076 (VHDL) language and extends it to provide capabilities of writing and simulating analog and mixed-signal models. This standard is published as a double logo IEC-IEEE standard.

General Information

- Status

- Published

- Publication Date

- 07-Jun-2021

- Technical Committee

- TC 91 - Electronics assembly technology

- Current Stage

- PPUB - Publication issued

- Start Date

- 08-Jun-2021

- Completion Date

- 04-Jun-2021

Relations

- Effective Date

- 05-Sep-2023

Overview

IEC 61691-6:2021 (IEC/IEEE Std 1076.1) defines the VHDL Analog and Mixed-Signal Extensions - commonly known as VHDL‑AMS. This double‑logo IEC‑IEEE standard extends the base VHDL language (IEC 61691‑1‑1 / IEEE 1076) to provide a harmonized hardware description language for the description, modeling and simulation of analog, digital and mixed‑signal systems. IEC 61691‑6:2021 covers language syntax, semantics and simulation semantics required for accurate behavioral and structural AMS modeling.

Key Topics and Technical Scope

The standard systematically specifies the language constructs and simulation behavior needed for AMS design. Key topics include:

- Design entities and configurations - entity declarations, architectures and configuration mechanisms for hierarchical AMS designs.

- Subprograms and packages - procedures, functions, overloading, packages and instantiation for reusable analog/digital models.

- Types and natures - scalar/composite types, access and protected types, plus natures for analog quantity semantics.

- Declarations and interfaces - port and signal declarations, interface modes and connectivity for mixed‑signal blocks.

- Expressions and statements - sequential and concurrent statements, signal and variable assignment, procedural constructs tailored to AMS behavior.

- Architecture statements and elaboration - processes, component instantiation, generate statements and elaboration/execution semantics for simulation.

- Simulation control and specifications - attributes, configuration, disconnection and step limit specifications to govern mixed‑signal simulation.

These topics (detailed in the standard’s table of contents) define both the language features and conformance rules necessary for interoperable tool support.

Practical Applications and Who Uses It

IEC 61691‑6:2021 is essential for professionals and organizations that need standardized AMS modeling and simulation:

- Analog and mixed‑signal IC designers - behavioral modeling of amplifiers, ADC/DAC, PLLs, RF front‑ends.

- SoC and system engineers - integration and co‑simulation of digital logic with analog blocks and sensors.

- EDA tool vendors - implementing VHDL‑AMS parsers, simulators and co‑simulation frameworks.

- Verification and validation teams - system‑level verification, regression testing and analog/digital interaction checks.

- Academia and research - teaching analog/digital co‑design and developing reusable AMS models.

Using VHDL‑AMS enables consistent description of continuous‑time analog behavior alongside event‑driven digital logic, improving model reuse and simulation fidelity.

Related Standards

- IEC 61691‑1‑1 / IEEE Std 1076 - Base VHDL language on which VHDL‑AMS is built.

- IEEE Std 1076.1‑2017 - the IEEE counterpart incorporated into IEC 61691‑6:2021.

IEC 61691‑6:2021 is available from IEC and IEEE publication channels for organizations requiring the official standard text.

Get Certified

Connect with accredited certification bodies for this standard

BSI Group

BSI (British Standards Institution) is the business standards company that helps organizations make excellence a habit.

National Aerospace and Defense Contractors Accreditation Program (NADCAP)

Global cooperative program for special process quality in aerospace.

CARES (UK Certification Authority for Reinforcing Steels)

UK certification for reinforcing steels and construction.

Sponsored listings

Frequently Asked Questions

IEC 61691-6:2021 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Behavioural languages - Part 6: VHDL Analog and Mixed-Signal Extensions". This standard covers: IEC 61691-6:2021(E) defines IEC 61691-6/IEEE Std 1076.1 language, a hardware description language for the description and the simulation of analog, digital, and mixed-signal systems. The language, also informally known as VHDL-AMS, is built on the IEC 61691-1-1/IEEE 1076 (VHDL) language and extends it to provide capabilities of writing and simulating analog and mixed-signal models. This standard is published as a double logo IEC-IEEE standard.

IEC 61691-6:2021(E) defines IEC 61691-6/IEEE Std 1076.1 language, a hardware description language for the description and the simulation of analog, digital, and mixed-signal systems. The language, also informally known as VHDL-AMS, is built on the IEC 61691-1-1/IEEE 1076 (VHDL) language and extends it to provide capabilities of writing and simulating analog and mixed-signal models. This standard is published as a double logo IEC-IEEE standard.

IEC 61691-6:2021 is classified under the following ICS (International Classification for Standards) categories: 25.040.01 - Industrial automation systems in general; 35.060 - Languages used in information technology. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 61691-6:2021 has the following relationships with other standards: It is inter standard links to IEC 61691-6:2009. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 61691-6:2021 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 61691-6 ®

Edition 2.0 2021-06

™

IEEE Std 1076.1

INTERNATIONAL

STANDARD

Behavioural languages –

Part 6: VHDL Analog and Mixed-Signal Extensions

All rights reserved. IEEE is a registered trademark in the U.S. Patent & Trademark Office, owned by the Institute of

Electrical and Electronics Engineers, Inc. Unless otherwise specified, no part of this publication may be reproduced

or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without

permission in writing from the IEC Central Office. Any questions about IEEE copyright should be addressed to the

IEEE. Enquiries about obtaining additional rights to this publication and other information requests should be

addressed to the IEC or your local IEC member National Committee.

IEC Central Office Institute of Electrical and Electronics Engineers, Inc.

3, rue de Varembé 3 Park Avenue

CH-1211 Geneva 20 New York, NY 10016-5997

Switzerland United States of America

Tel.: +41 22 919 02 11 stds.info@ieee.org

info@iec.ch www.ieee.org

www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigendum or an amendment might have been published.

IEC publications search - webstore.iec.ch/advsearchform IEC online collection - oc.iec.ch

The advanced search enables to find IEC publications by a Discover our powerful search engine and read freely all the

variety of criteria (reference number, text, technical publications previews. With a subscription you will always

committee, …). It also gives information on projects, replaced have access to up to date content tailored to your needs.

and withdrawn publications.

Electropedia - www.electropedia.org

IEC Just Published - webstore.iec.ch/justpublished

The world's leading online dictionary on electrotechnology,

Stay up to date on all new IEC publications. Just Published

containing more than 22 000 terminological entries in English

details all new publications released. Available online and

and French, with equivalent terms in 18 additional languages.

once a month by email.

Also known as the International Electrotechnical Vocabulary

(IEV) online.

IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or

need further assistance, please contact the Customer Service

Centre: sales@iec.ch.

IEC 61691-6 ®

Edition 2.0 2021-06

IEEE Std 1076.1™

INTERNATIONAL

STANDARD

Behavioural languages –

Part 6: VHDL Analog and Mixed-Signal Extensions

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

ICS 25.040.01; 35.060 ISBN 978-2-8322-9830-5

i

IEEE Std 1076.1™-2017

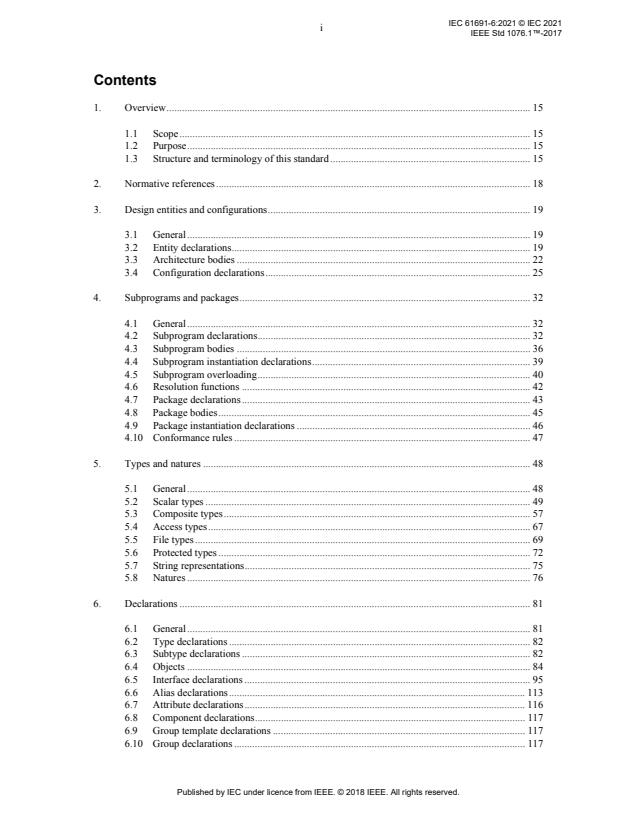

Contents

1. Overview. 15

1.1 Scope. 15

1.2 Purpose. 15

1.3 Structure and terminology of this standard . 15

2. Normative references. 18

3. Design entities and configurations. 19

3.1 General. 19

3.2 Entity declarations. 19

3.3 Architecture bodies . 22

3.4 Configuration declarations. 25

4. Subprograms and packages. 32

4.1 General. 32

4.2 Subprogram declarations. 32

4.3 Subprogram bodies . 36

4.4 Subprogram instantiation declarations. 39

4.5 Subprogram overloading. 40

4.6 Resolution functions . 42

4.7 Package declarations . 43

4.8 Package bodies. 45

4.9 Package instantiation declarations . 46

4.10 Conformance rules . 47

5. Types and natures . 48

5.1 General. 48

5.2 Scalar types . 49

5.3 Composite types. 57

5.4 Access types. 67

5.5 File types. 69

5.6 Protected types . 72

5.7 String representations. 75

5.8 Natures . 76

6. Declarations . 81

6.1 General. 81

6.2 Type declarations . 82

6.3 Subtype declarations . 82

6.4 Objects . 84

6.5 Interface declarations . 95

6.6 Alias declarations. 113

6.7 Attribute declarations. 116

6.8 Component declarations. 117

6.9 Group template declarations . 117

6.10 Group declarations . 117

Published by IEC under licence from IEEE. © 2018 IEEE. All rights reserved.

ii

IEEE Std 1076.1™-2017

6.11 Nature and subnature declarations . 118

6.12 PSL clock declarations. 119

7. Specifications. 120

7.1 General. 120

7.2 Attribute specification. 120

7.3 Configuration specification. 123

7.4 Disconnection specification .129

7.5 Step limit specification. 131

8. Names . 134

8.1 General. 134

8.2 Simple names . 135

8.3 Selected names. 136

8.4 Indexed names. 138

8.5 Slice names . 139

8.6 Attribute names . 139

8.7 External names. 140

9. Expressions . 144

9.1 General. 144

9.2 Operators. 145

9.3 Operands . 158

9.4 Static expressions. 166

9.5 Universal expressions . 170

9.6 Linear forms. 170

10 Sequential statements. 173

10.1 General. 173

10.2 Wait statement. 173

10.3 Assertion statement . 175

10.4 Report statement . 176

10.5 Signal assignment statement .177

10.6 Variable assignment statement. 188

10.7 Procedure call statement . 192

10.8 If statement. 192

10.9 Case statement. 193

10.10 Loop statement. 195

10.11 Next statement. 195

10.12 Exit statement. 196

10.13 Return statement . 196

10.14 Null statement . 197

10.15 Break statement. 197

11. Architecture statements. 198

11.1 General. 198

11.2 Block statement. 199

11.3 Process statement . 200

11.4 Concurrent procedure call statements . 202

Published by IEC under licence from IEEE. © 2018 IEEE. All rights reserved.

iii

IEEE Std 1076.1™-2017

11.5 Concurrent assertion statements. 203

11.6 Concurrent signal assignment statements . 204

11.7 Component instantiation statements . 206

11.8 Generate statements . 212

11.9 Concurrent break statement .214

11.10 Simple simultaneous statement. 215

11.11 Simultaneous if statement . 216

11.12 Simultaneous case statement. 216

11.13 Simultaneous procedural statement . 217

11.14 Simultaneous null statement . 220

12. Scope and visibility. 221

12.1 Declarative region . 221

12.2 Scope of declarations . 221

12.3 Visibility. 223

12.4 Use clauses. 227

12.5 The context of overload resolution . 228

13. Design units and their analysis . 230

13.1 Design units. 230

13.2 Design libraries . 230

13.3 Context declarations. 232

13.4 Context clauses . 232

13.5 Order of analysis . 233

14. Elaboration and execution . 234

14.1 General. 234

14.2 Elaboration of a design hierarchy . 234

14.3 Elaboration of a block, package, or subprogram header. 238

14.4 Elaboration of a declarative part .241

14.5 Elaboration of a statement part .246

14.6 Dynamic elaboration . 250

14.7 Execution of a model . 251

14.8 Time and the analog solver . 266

14.9 Frequency and noise calculation . 267

15. Lexical elements . 269

15.1 General. 269

15.2 Character set. 269

15.3 Lexical elements, separators, and delimiters . 271

15.4 Identifiers . 273

15.5 Abstract literals . 274

15.6 Character literals . 275

15.7 String literals . 275

15.8 Bit string literals. 276

15.9 Comments . 278

15.10 Reserved words . 279

15.11 Tool directives. 281

Published by IEC under licence from IEEE. © 2018 IEEE. All rights reserved.

iv

IEEE Std 1076.1™-2017

16. Predefined language environment . 282

16.1 General. 282

16.2 Predefined attributes . 282

16.3 Package STANDARD. 304

16.4 Package TEXTIO. 319

16.5 Standard environment package . 325

16.6 Standard mathematical packages . 326

16.7 Standard multivalue logic package . 327

16.8 Standard synthesis packages .327

16.9 Standard synthesis context declarations. 333

16.10 Fixed-point package. 334

16.11 Floating-point package. 334

16.12 Standard packages for multiple energy domain support. 335

17. VHDL Procedural Interface overview. 336

17.1 General. 336

17.2 Organization of the interface. 336

17.3 Capability sets. 337

17.4 Handles. 339

18. VHPI access functions . 341

18.1 General. 341

18.2 Information access functions .341

18.3 Property access functions. 343

18.4 Access by name function . 344

19. VHPI information model . 345

19.1 General. 345

19.2 Formal notation . 345

19.3 Class inheritance hierarchy . 346

19.4 Name properties . 347

19.5 The stdUninstantiated package . 360

19.6 The stdHierarchy package. 363

19.7 The stdTypes package. 370

19.8 The stdExpr package. 372

19.9 The stdSpec package. 375

19.10 The stdSubprograms package . 377

19.11 The stdStmts package. 379

19.12 The stdConnectivity package .385

19.13 The stdCallbacks package. 390

19.14 The stdEngine package . 391

19.15 The stdForeign package . 391

19.16 The stdMeta package . 391

19.17 The stdTool package . 393

19.18 Application contexts . 394

20. VHPI tool execution . 395

20.1 General. 395

20.2 Registration phase . 395

Published by IEC under licence from IEEE. © 2018 IEEE. All rights reserved.

v

IEEE Std 1076.1™-2017

20.3 Analysis phase. 401

20.4 Elaboration phase. 401

20.5 Initialization phase . 403

20.6 Simulation phase . 403

20.7 Save phase. 403

20.8 Restart phase . 404

20.9 Reset phase. 404

20.10 Termination phase. 405

21. VHPI callbacks . 406

21.1 General. 406

21.2 Callback functions. 406

21.3 Callback reasons . 408

22. VHPI value access and update. 420

22.1 General. 420

22.2 Value structures and types . 420

22.3 Reading object values . 423

22.4 Formatting values. 424

22.5 Updating object values. 426

22.6 Scheduling transactions on drivers . 430

23. VHPI function reference. 433

23.1 General. 433

23.2 vhpi_assert . 433

23.3 vhpi_check_error . 434

23.4 vhpi_compare_handles. 436

23.5 vhpi_control . 437

23.6 vhpi_create . 439

23.7 vhpi_disable_cb . 441

23.8 vhpi_enable_cb . 441

23.9 vhpi_format_value . 442

23.10 vhpi_get. 444

23.11 vhpi_get_cb_info . 444

23.12 vhpi_get_data . 445

23.13 vhpi_get_foreignf_info . 447

23.14 vhpi_get_next_time. 448

23.15 vhpi_get_phys . 449

23.16 vhpi_get_real. 450

23.17 vhpi_get_str. 451

23.18 vhpi_get_time. 451

23.19 vhpi_get_value . 452

23.20 vhpi_handle. 453

23.21 vhpi_handle_by_index . 454

23.22 vhpi_handle_by_name . 457

23.23 vhpi_is_printable. 459

23.24 vhpi_iterator. 459

23.25 vhpi_printf. 460

23.26 vhpi_protected_call. 461

23.27 vhpi_put_data. 463

23.28 vhpi_put_value. 465

Published by IEC under licence from IEEE. © 2018 IEEE. All rights reserved.

vi

IEEE Std 1076.1™-2017

23.29 vhpi_register_cb. 466

23.30 vhpi_register_foreignf. 468

23.31 vhpi_release_handle. 470

23.32 vhpi_remove_cb. 470

23.33 vhpi_scan . 471

23.34 vhpi_schedule_transaction . 472

23.35 vhpi_vprintf. 475

24. Standard tool directives . 476

24.1 Protect tool directives. 476

Annex A (informative) Description of accompanying files . 493

Annex B (informative) VHPI header file . 497

Annex C (informative) Syntax summary. 523

Annex D (informative) Potentially nonportable constructs. 551

Annex E (informative) Changes from IEEE Std 1076.1-2007 . 552

Annex F (informative) Features under consideration for removal . 555

Annex G (informative) Guide to use of standard packages.556

Annex H (informative) Guide to use of protect directives . 594

Annex I (informative) Glossary. 600

Annex J (informative) Bibliography. 629

Annex K (informative) IEEE List of participants . 631

Index . 632

Published by IEC under licence from IEEE. © 2018 IEEE. All rights reserved.

vii

IEEE Std 1076.1™-2017

BEHAVIOURAL LANGUAGES –

Part 6: VHDL Analog and Mixed-Signal Extensions

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international

co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and

in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports,

Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC document(s)"). Their

preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with

may participate in this preparatory work. International, governmental and non-governmental organizations liaising

with the IEC also participate in this preparation.

IEEE Standards documents are developed within IEEE Societies and Standards Coordinating Committees of the

IEEE Standards Association (IEEE SA) Standards Board. IEEE develops its standards through a consensus

development process, approved by the American National Standards Institute, which brings together volunteers

representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members

of IEEE and serve without compensation. While IEEE administers the process and establishes rules to promote

fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the

accuracy of any of the information contained in its standards. Use of IEEE Standards documents is wholly

voluntary. IEEE documents are made available for use subject to important notices and legal disclaimers (see

http://standards.ieee.org/ipr/disclaimers.html for more information).

IEC collaborates closely with IEEE in accordance with conditions determined by agreement between the two

organizations. This Dual Logo International Standard was jointly developed by the IEC and IEEE under the terms

of that agreement.

2) The formal decisions of IEC on technical matters express, as nearly as possible, an international consensus of

opinion on the relevant subjects since each technical committee has representation from all interested IEC

National Committees. The formal decisions of IEEE on technical matters, once consensus within IEEE Societies

and Standards Coordinating Committees has been reached, is determined by a balanced ballot of materially

interested parties who indicate interest in reviewing the proposed standard. Final approval of the IEEE standards

document is given by the IEEE Standards Association (IEEE SA) Standards Board.

3) IEC/IEEE Publications have the form of recommendations for international use and are accepted by IEC National

Committees/IEEE Societies in that sense. While all reasonable efforts are made to ensure that the technical

content of IEC/IEEE Publications is accurate, IEC or IEEE cannot be held responsible for the way in which they

are used or for any misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

(including IEC/IEEE Publications) transparently to the maximum extent possible in their national and regional

publications. Any divergence between any IEC/IEEE Publication and the corresponding national or regional

publication shall be clearly indicated in the latter.

5) IEC and IEEE do not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC and IEEE are not responsible

for any services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or IEEE or their directors, employees, servants or agents including individual

experts and members of technical committees and IEC National Committees, or volunteers of IEEE Societies and

the Standards Coordinating Committees of the IEEE Standards Association (IEEE SA) Standards Board, for any

personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for

costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC/IEEE

Publication or any other IEC or IEEE Publications.

8) Attention is drawn to the normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that implementation of this IEC/IEEE Publication may require use of material

covered by patent rights. By publication of this standard, no position is taken with respect to the existence or

validity of any patent rights in connection therewith. IEC or IEEE shall not be held responsible for identifying

Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or

scope of Patent Claims or determining whether any licensing terms or conditions provided in connection with

submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory.

Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk

of infringement of such rights, is entirely their own responsibility.

IEC 61691-6/IEEE Std 1076.1 was processed through IEC technical committee 91: Electronics

assembly technology, under the IEC/IEEE Dual Logo Agreement. It is an International Stand

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...