IEC 63215-2:2023

(Main)Endurance test methods for die attach materials - Part 2: Temperature cycling test method for die attach materials applied to discrete type power electronic devices

Endurance test methods for die attach materials - Part 2: Temperature cycling test method for die attach materials applied to discrete type power electronic devices

IEC 63215-2:2023 applies to the die attach materials and joining system applied to discrete type power electronic devices.

This document specifies the temperature cycling test method which takes into account the actual usage conditions of discrete type power electronic devices to evaluate reliability of the die attach joint materials and joining system, and establishes a classification level for joining reliability (reliability performance index).

The test method specified in this document is not intended to evaluate power semiconductor devices themselves.

The test method specified in this document is not regarded as the one for use to guarantee the reliability of the power semiconductor device packages.

NOTE The test result obtained using this document will not be used as absolute quantitative data, but for intercomparison with the other die attach materials results using the same setup.

Méthodes d’essai d’endurance pour les matériaux de fixation de puce - Partie 2: Méthode d’essai de cycle thermique pour les matériaux de fixation de puce, appliquée aux dispositifs électroniques de puissance de type discret

L’IEC 63215-2:2023 concerne les matériaux de fixation de puce et le système d’assemblage appliqués aux dispositifs électroniques de puissance de type discret.

Le présent document spécifie le procédé d’essai de cycle thermique qui prend en compte les conditions d’usage réelles des dispositifs électroniques de puissance de type discret pour apprécier la fiabilité des matériaux de joint de fixation de puce et du système d’assemblage, et elle établit le niveau de classification concernant la fiabilité des assemblages (indice de performance de fiabilité).

La méthode d’essai spécifiée dans le présent document n’a pas pour objectif d’évaluer les dispositifs à semiconducteurs de puissance eux-mêmes.

La méthode d’essai spécifiée dans le présent document n’est pas considérée comme étant celle à utiliser pour garantir la fiabilité des boîtiers de dispositifs à semiconducteurs de puissance.

NOTE Le résultat d’essai obtenu à l’aide du présent document ne sera pas utilisé comme des données quantitatives absolues, mais comme comparaison entre les résultats des autres matériaux de fixation de puces utilisant le même montage.

General Information

- Status

- Published

- Publication Date

- 23-Oct-2023

- Technical Committee

- TC 91 - Electronics assembly technology

- Drafting Committee

- WG 3 - TC 91/WG 3

- Current Stage

Overview

IEC 63215-2:2023 is an international standard published by the International Electrotechnical Commission (IEC) that specifies a temperature cycling test method for evaluating the endurance and reliability of die attach materials used in discrete type power electronic devices. The standard focuses on assessing the performance of die attach joints and joining systems under thermal stress that simulates actual operating conditions. This document forms Part 2 of the IEC 63215 series which addresses endurance test methods for die attach materials.

IEC 63215-2:2023 establishes a systematic procedure to test temperature cycling durability and introduces a reliability performance index to classify the joining reliability of die attach materials. It is important to note that this test method assesses the die attach materials themselves and the joining process, rather than the power semiconductor devices or their packages directly.

Key Topics

Scope and Purpose

The standard applies specifically to die attach materials and joining systems used for discrete power electronic devices. It is designed to evaluate the reliability of the die attach joint under cyclic thermal stress, ensuring that materials can withstand real-world temperature fluctuations.Temperature Cycling Test Conditions

The document specifies test temperature ranges, dwell times, and cycling procedures that replicate typical thermal stresses experienced during the operation of power electronic devices. These conditions are established to provide meaningful endurance data on die attach materials.Test Apparatus and Setup

Includes detailed requirements for required equipment such as die bonding tools, temperature cycling chambers, thermal resistance measuring equipment, and ultrasonic flaw inspection devices to monitor die attach joint integrity during and after testing.Specimen Preparation and Handling

Guidelines for preparing test specimens, including the use of representative chips such as Thermoelectric Generator (TEG) chips, substrate preparation, and packaging treatments in line with reproducible, standardized test conditions.Evaluation and Inspection Methods

Procedures for thermal resistance measurement and ultrasonic flaw detection are prescribed to assess mechanical and thermal degradation of the die attach joint throughout the test process.Reliability Performance Index

A classification metric is introduced to rank joining reliability based on test results, enabling comparison between die attach materials and joining processes.Limitations

The test method is not intended for device qualification or absolute quantification of reliability but serves for comparative evaluation of die attach materials.

Applications

IEC 63215-2:2023 is critical for organizations involved in the design, manufacture, and testing of discrete type power electronic devices, including:

Semiconductor manufacturers developing new die attach materials and joining techniques aiming to enhance device longevity under thermal cycling conditions.

Power electronics designers to select appropriate die attach materials that sustain reliable performance under thermal stress.

Quality assurance and testing labs to implement standardized test protocols for endurance assessment of die attach joints.

Research and development units focusing on improving thermal management and structural integrity of power semiconductor packages.

By adopting this standard, stakeholders can ensure more reliable power electronics devices, reducing failures caused by thermal fatigue in die attach regions and improving overall device robustness.

Related Standards

- IEC 63215-1: Endurance test methods for die attach materials - Part 1: [Basic test methods for die attach materials]

- IEC 60747 series: Semiconductor device standards covering testing and reliability aspects.

- JEDEC Standards: Various test methods for semiconductor material and assembly reliability applicable alongside IEC methods.

- ISO/IEC Directives: Guidelines for standard development followed by IEC to maintain international consistency.

Keywords

- Die attach materials

- Power electronic devices

- Temperature cycling test

- Thermal cycling endurance

- Reliability performance index

- Discrete semiconductor devices

- Thermal resistance measurement

- Ultrasonic flaw inspection

- Electronic assembly technology

- IEC standards for electronics testing

Adhering to IEC 63215-2:2023 helps ensure that die attach materials used in discrete power electronics are rigorously tested for thermal cycling endurance, enabling manufacturers to deliver products with high reliability and long-lasting performance under challenging operating environments.

Frequently Asked Questions

IEC 63215-2:2023 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Endurance test methods for die attach materials - Part 2: Temperature cycling test method for die attach materials applied to discrete type power electronic devices". This standard covers: IEC 63215-2:2023 applies to the die attach materials and joining system applied to discrete type power electronic devices. This document specifies the temperature cycling test method which takes into account the actual usage conditions of discrete type power electronic devices to evaluate reliability of the die attach joint materials and joining system, and establishes a classification level for joining reliability (reliability performance index). The test method specified in this document is not intended to evaluate power semiconductor devices themselves. The test method specified in this document is not regarded as the one for use to guarantee the reliability of the power semiconductor device packages. NOTE The test result obtained using this document will not be used as absolute quantitative data, but for intercomparison with the other die attach materials results using the same setup.

IEC 63215-2:2023 applies to the die attach materials and joining system applied to discrete type power electronic devices. This document specifies the temperature cycling test method which takes into account the actual usage conditions of discrete type power electronic devices to evaluate reliability of the die attach joint materials and joining system, and establishes a classification level for joining reliability (reliability performance index). The test method specified in this document is not intended to evaluate power semiconductor devices themselves. The test method specified in this document is not regarded as the one for use to guarantee the reliability of the power semiconductor device packages. NOTE The test result obtained using this document will not be used as absolute quantitative data, but for intercomparison with the other die attach materials results using the same setup.

IEC 63215-2:2023 is classified under the following ICS (International Classification for Standards) categories: 31.190 - Electronic component assemblies. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 63215-2:2023 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 63215-2 ®

Edition 1.0 2023-10

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

Endurance test methods for die attach materials –

Part 2: Temperature cycling test method for die attach materials applied to

discrete type power electronic devices

Méthodes d’essai d’endurance pour les matériaux de fixation de puce –

Partie 2: Méthode d’essai de cycle thermique pour les matériaux de fixation de

puce, appliquée aux dispositifs électroniques de puissance de type discret

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form

or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from

either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC

copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or

your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite ni

utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie et

les microfilms, sans l'accord écrit de l'IEC ou du Comité national de l'IEC du pays du demandeur. Si vous avez des

questions sur le copyright de l'IEC ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez

les coordonnées ci-après ou contactez le Comité national de l'IEC de votre pays de résidence.

IEC Secretariat Tel.: +41 22 919 02 11

3, rue de Varembé info@iec.ch

CH-1211 Geneva 20 www.iec.ch

Switzerland

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigendum or an amendment might have been published.

IEC publications search - webstore.iec.ch/advsearchform IEC Products & Services Portal - products.iec.ch

The advanced search enables to find IEC publications by a Discover our powerful search engine and read freely all the

variety of criteria (reference number, text, technical publications previews. With a subscription you will always have

committee, …). It also gives information on projects, replaced access to up to date content tailored to your needs.

and withdrawn publications.

Electropedia - www.electropedia.org

IEC Just Published - webstore.iec.ch/justpublished

The world's leading online dictionary on electrotechnology,

Stay up to date on all new IEC publications. Just Published

containing more than 22 300 terminological entries in English

details all new publications released. Available online and once

and French, with equivalent terms in 19 additional languages.

a month by email.

Also known as the International Electrotechnical Vocabulary

(IEV) online.

IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or need

further assistance, please contact the Customer Service

Centre: sales@iec.ch.

A propos de l'IEC

La Commission Electrotechnique Internationale (IEC) est la première organisation mondiale qui élabore et publie des

Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications IEC

Le contenu technique des publications IEC est constamment revu. Veuillez vous assurer que vous possédez l’édition la

plus récente, un corrigendum ou amendement peut avoir été publié.

Recherche de publications IEC - IEC Products & Services Portal - products.iec.ch

webstore.iec.ch/advsearchform Découvrez notre puissant moteur de recherche et consultez

La recherche avancée permet de trouver des publications IEC gratuitement tous les aperçus des publications. Avec un

en utilisant différents critères (numéro de référence, texte, abonnement, vous aurez toujours accès à un contenu à jour

comité d’études, …). Elle donne aussi des informations sur les adapté à vos besoins.

projets et les publications remplacées ou retirées.

Electropedia - www.electropedia.org

IEC Just Published - webstore.iec.ch/justpublished

Le premier dictionnaire d'électrotechnologie en ligne au monde,

Restez informé sur les nouvelles publications IEC. Just

avec plus de 22 300 articles terminologiques en anglais et en

Published détaille les nouvelles publications parues.

français, ainsi que les termes équivalents dans 19 langues

Disponible en ligne et une fois par mois par email.

additionnelles. Egalement appelé Vocabulaire

Electrotechnique International (IEV) en ligne.

Service Clients - webstore.iec.ch/csc

Si vous désirez nous donner des commentaires sur cette

publication ou si vous avez des questions contactez-nous:

sales@iec.ch.

IEC 63215-2 ®

Edition 1.0 2023-10

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

Endurance test methods for die attach materials –

Part 2: Temperature cycling test method for die attach materials applied to

discrete type power electronic devices

Méthodes d’essai d’endurance pour les matériaux de fixation de puce –

Partie 2: Méthode d’essai de cycle thermique pour les matériaux de fixation de

puce, appliquée aux dispositifs électroniques de puissance de type discret

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION

ELECTROTECHNIQUE

INTERNATIONALE

ICS 31.190 ISBN 978-2-8322-7677-8

– 2 – IEC 63215-2:2023 © IEC 2023

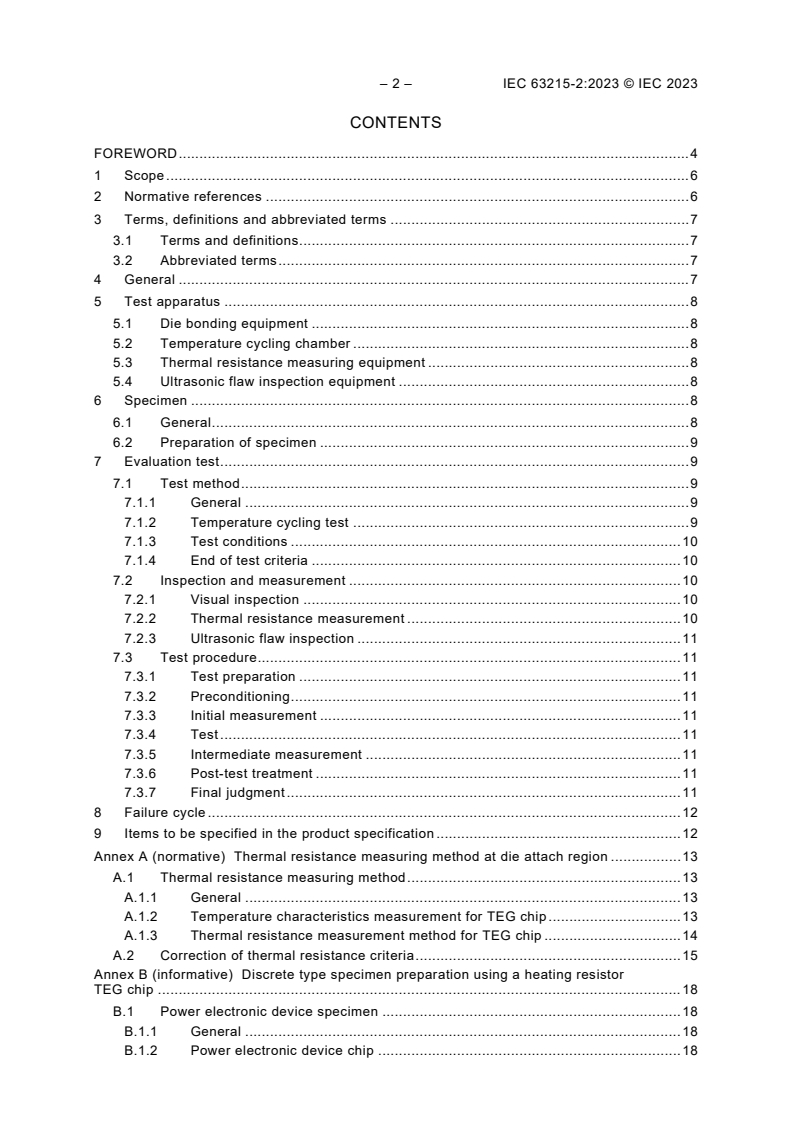

CONTENTS

FOREWORD . 4

1 Scope . 6

2 Normative references . 6

3 Terms, definitions and abbreviated terms . 7

3.1 Terms and definitions . 7

3.2 Abbreviated terms . 7

4 General . 7

5 Test apparatus . 8

5.1 Die bonding equipment . 8

5.2 Temperature cycling chamber . 8

5.3 Thermal resistance measuring equipment . 8

5.4 Ultrasonic flaw inspection equipment . 8

6 Specimen . 8

6.1 General . 8

6.2 Preparation of specimen . 9

7 Evaluation test . 9

7.1 Test method . 9

7.1.1 General . 9

7.1.2 Temperature cycling test . 9

7.1.3 Test conditions . 10

7.1.4 End of test criteria . 10

7.2 Inspection and measurement . 10

7.2.1 Visual inspection . 10

7.2.2 Thermal resistance measurement . 10

7.2.3 Ultrasonic flaw inspection . 11

7.3 Test procedure . 11

7.3.1 Test preparation . 11

7.3.2 Preconditioning . 11

7.3.3 Initial measurement . 11

7.3.4 Test . 11

7.3.5 Intermediate measurement . 11

7.3.6 Post-test treatment . 11

7.3.7 Final judgment . 11

8 Failure cycle . 12

9 Items to be specified in the product specification . 12

Annex A (normative) Thermal resistance measuring method at die attach region . 13

A.1 Thermal resistance measuring method . 13

A.1.1 General . 13

A.1.2 Temperature characteristics measurement for TEG chip . 13

A.1.3 Thermal resistance measurement method for TEG chip . 14

A.2 Correction of thermal resistance criteria . 15

Annex B (informative) Discrete type specimen preparation using a heating resistor

TEG chip . 18

B.1 Power electronic device specimen . 18

B.1.1 General . 18

B.1.2 Power electronic device chip . 18

B.1.3 Base substrate . 18

B.1.4 Package mould . 19

B.1.5 Surface treatment . 19

B.2 Die attach materials . 19

B.3 Specimen preparation . 19

Annex C (informative) Reliability performance index for die attach joint – Discrete type

power electronic device . 22

Bibliography . 23

Figure 1 – Regions for evaluation for discrete type power electronic device . 8

Figure 2 – Temperature cycling test . 9

Figure A.1 – Example of the structure of the specimen using a TEG chip . 13

Figure A.2 – Example of temperature characteristics – TEG chip . 14

Figure A.3 – Example of structure for thermal resistance measurement for a power

electronic device . 15

Figure A.4 – Example of relationship between thermal resistance and die attach

damage . 16

Figure A.5 – Example of ultrasonic flaw inspection result . 17

Figure B.1 – Example of TEG chip . 18

Figure B.2 – Typical reflow soldering profile for Sn96,5Ag3Cu,5 solder alloy . 20

Figure B.3 – Example of specimen – TEG chip . 21

Table 1 – Temperature cycling test conditions . 10

Table A.1 – Example of thermal resistance value (R ) result . 16

th

Table C.1 – Reliability performance index for die attach joint – Discrete type power

electronic device . 22

– 4 – IEC 63215-2:2023 © IEC 2023

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

ENDURANCE TEST METHODS FOR DIE ATTACH MATERIALS –

Part 2: Temperature cycling test method for die attach materials applied

to discrete type power electronic devices

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international

co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and

in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports,

Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC Publication(s)”). Their

preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with

may participate in this preparatory work. International, governmental and non-governmental organizations liaising

with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for

Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence between

any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) IEC draws attention to the possibility that the implementation of this document may involve the use of (a)

patent(s). IEC takes no position concerning the evidence, validity or applicability of any claimed patent rights in

respect thereof. As of the date of publication of this document, IEC had not received notice of (a) patent(s), which

may be required to implement this document. However, implementers are cautioned that this may not represent

the latest information, which may be obtained from the patent database available at https://patents.iec.ch. IEC

shall not be held responsible for identifying any or all such patent rights.

IEC 63215-2 has been prepared by IEC technical committee 91: Electronics assembly

technology. It is an International Standard.

The text of this International Standard is based on the following documents:

Draft Report on voting

91/1895/FDIS 91/1912/RVD

Full information on the voting for its approval can be found in the report on voting indicated in

the above table.

The language used for the development of this International Standard is English.

This document was drafted in accordance with ISO/IEC Directives, Part 2, and developed in

accordance with ISO/IEC Directives, Part 1 and ISO/IEC Directives, IEC Supplement, available

at www.iec.ch/members_experts/refdocs. The main document types developed by IEC are

described in greater detail at www.iec.ch/publications.

A list of all parts in the IEC 63215 series, published under the general title Endurance test

methods for die attach materials, can be found on the IEC website.

The committee has decided that the contents of this document will remain unchanged until the

stability date indicated on the IEC website under webstore.iec.ch in the data related to the

specific document. At this date, the document will be

• reconfirmed,

• withdrawn, or

• revised.

IMPORTANT – The "colour inside" logo on the cover page of this document indicates

that it contains colours which are considered to be useful for the correct understanding

of its contents. Users should therefore print this document using a colour printer.

– 6 – IEC 63215-2:2023 © IEC 2023

ENDURANCE TEST METHODS FOR DIE ATTACH MATERIALS –

Part 2: Temperature cycling test method for die attach materials applied

to discrete type power electronic devices

1 Scope

This part of IEC 63215 applies to the die attach materials and joining system applied to discrete

type power electronic devices.

This document specifies the temperature cycling test method which takes into account the

actual usage conditions of discrete type power electronic devices to evaluate reliability of the

die attach joint materials and joining system, and establishes a classification level for joining

reliability (reliability performance index).

The test method specified in this document is not intended to evaluate power semiconductor

devices themselves.

The test method specified in this document is not regarded as the one for use to guarantee the

reliability of the power semiconductor device packages.

NOTE The test result obtained using this document will not be used as absolute quantitative data, but for

intercomparison with the other die attach materials results using the same setup.

2 Normative references

The following documents are referred to in the text in such a way that some or all of their content

constitutes requirements of this document. For dated references, only the edition cited applies.

For undated references, the latest edition of the referenced document (including any

amendments) applies.

IEC 60068-2-14, Environmental testing – Part 2-14: Tests – Test N: Change of temperature

IEC 60194-1, Printed boards design, manufacture and assembly – Vocabulary – Part 1:

Common usage in printed board and electronic assembly technologies

IEC 60194-2, Printed boards design, manufacture and assembly – Vocabulary – Part 2:

Common usage in electronic technologies as well as printed board and electronic assembly

technologies

IEC 60747-15, Semiconductor devices – Discrete devices – Part 15: Isolated power

semiconductor devices

3 Terms, definitions and abbreviated terms

3.1 Terms and definitions

For the purposes of this document, terms and definitions given in IEC 60194-1,

IEC 60194-2, and the following apply.

ISO and IEC maintain terminology databases for use in standardization at the following

addresses:

• IEC Electropedia: available at https://www.electropedia.org/

• ISO Online browsing platform: available at https://www.iso.org/obp

3.1.1

TEG chip

chip with test patterns for process and device evaluation and control

Note 1 to entry: In this document, the heating resistor chip is as in 6.1.

3.2 Abbreviated terms

C-SAM constant-depth mode scanning acoustic microscope

SAT scanning acoustic tomography

TCT temperature cycling test

TEG test element group

4 General

The regions of the die attach materials and joining systems to be evaluated are shown in

Figure 1. The test method in this document is applicable to evaluate the durability of the die

attach materials against thermal stress to the power electronic devices but not to test the

mechanical strength of the power electronic devices themselves.

Therefore, the conditions for accelerated stress conditioning by a cycling test can exceed the

maximum allowable temperature range for the power electronic devices.

– 8 – IEC 63215-2:2023 © IEC 2023

Key

1 power electronic device chip

2 die attach material

3 base substrate

4 device termination

5 plating layers

6 inter-metallic compound layers

7 regions for evaluation

8 crack

Figure 1 – Regions for evaluation for discrete type power electronic device

5 Test apparatus

5.1 Die bonding equipment

The die bonding equipment shall be able to realize the die bonding conditions.

5.2 Temperature cycling chamber

The temperature cycling chamber shall be able to realize the temperature cycling profile

specified in Figure 2 and Table 1. The general requirements for the temperature cycling

chamber shall be in accordance with test Na of IEC 60068-2-14.

5.3 Thermal resistance measuring equipment

The thermal resistance measuring equipment shall be able to measure thermal conductivity in

accordance with IEC 60747-15, and also be able to calculate the thermal resistance value of

the specimen as in Annex A.

5.4 Ultrasonic flaw inspection equipment

Ultrasonic flaw inspection equipment such as scanning acoustic tomography (SAT) or constant-

depth mode scanning acoustic microscope (C-SAM) shall be able to detect cracks and voids in

the die attach joint by non-destructive inspection of the ultrasonic scanning, and be able to

calculate the crack propagation area ratio in die attach joint as in Annex A.

6 Specimen

6.1 General

The specimen shall be a heating element chip which is bonded using die attach material under

evaluation on the base substrate. The heating element chip which is able to realize the test

conditions specified in Clause 7, can be either a heating resistor chip (heater TEG chip,

hereafter referred to as "TEG chip") or a power semiconductor device chip.

An example of the specimen structure is described in Annex B.

6.2 Preparation of specimen

The die attach joint is made by the reflow soldering method or sintering method, for example.

Depending on the die attach material, a press joint system, or reduced pressure reflow or formic

acid atmosphere reflow for oxidation/reduction operation, may be used to secure the joint.

The preparation process for an example structure of the power electronic device specimen is

described in Annex B.

7 Evaluation test

7.1 Test method

7.1.1 General

The test method for evaluation shall be done by the temperature cycling test.

7.1.2 Temperature cycling test

The test shall be made in accordance with test Na of IEC 60068-2-14 and the following details.

Place the specimen in the temperature cycling chamber specified in 5.2 where the best airflow

is obtained and where there is sufficient airflow around the specimen.

The temperature cycle shall be started from the low temperature side as shown in Figure 2. The

test cycles shall be as specified in the product specification.

Key

maximum storage temperature t hold time at T

T

1 min

max

normal ambient temperature t hold time at T

T

2 max

n

minimum storage temperature t one temperature cycle

T

cyc

min

Figure 2 – Temperature cycling test

– 10 – IEC 63215-2:2023 © IEC 2023

7.1.3 Test conditions

The product specification shall specify the temperature cycling test conditions selected from

Table 1.

Table 1 – Temperature cycling test conditions

Step Test conditions

TA TB TC

T °C

–40 ± 5 –40 ± 5 –40 ± 5

min

T °C

150 ± 5 175 ± 5 200 ± 5

max

t , t 20 min or more

1 2

Unless otherwise specified in the product specification, the specified measurements

Intermediate

shall be made at the following cycles:

measurement

0 (initial), 500, 1 000, 1 500

Number of specimens 5 or more for each test condition

Key

T : minimum storage temperature,

min

T : minimum storage temperature,

max

t and t start when the temperature of the specimen reaches the specified temperature.

1 2

The transition time from T to T and reverse transfer shall be within 3 min and include a cycle time with the

min max

duration to reach the thermal stabilizing time of the specimen (refer to IEC 60068-2-14).

7.1.4 End of test criteria

Each evaluation test shall be terminated if the thermal resistance value (R ) of the specimen

th

increases by 20 % from the initial measurement, unless otherwise specified in the product

specification.

Each evaluation test shall continue up to the test cycles specified in the product specification,

except if the end of the test criteria specified above is reached.

7.2 Inspection and measurement

7.2.1 Visual inspection

The specimen shall be subjected to visual inspection. There shall be no defect which would

impair validity of the test result.

7.2.2 Thermal resistance measurement

Thermal resistance of the specimen shall be measured using thermal resistance measuring

equipment specified in 5.3 and the adopted measuring method referred to as the static heating

method specified in Annex A, to determine the degree of deterioration.

The thermal resistance measurement method such as the static heating method (heating

method or cooling method) or dynamic heating method (thermal transient characterization

method) which are used in the marketplace, may be used based upon the agreement between

trading partners.

The thermal resistance shall be recorded so that the change in the thermal resistance value of

one of the specimens can be traced.

7.2.3 Ultrasonic flaw inspection

The image of die attach conditions of the same specimen crack and the other defects shall be

taken using ultrasonic flaw inspection equipment specified in 5.4, to determine the degree of

deterioration.

The image of ultrasonic flaw inspection and crack propagation area ratio shall be recorded for

the die attach damage data recognized by two-valued image processing.

7.3 Test procedure

7.3.1 Test preparation

If the residue flux on the specimen has to be cleaned, the cleaning method should be specified

in the product specification.

The mounting for the evaluation test shall be ensured.

7.3.2 Preconditioning

If required, the preconditioning conditions shall be specified in the product specification.

7.3.3 Initial measurement

All specimens shall be subjected to initial measurement in accordance with 7.2.

The measuring condition for the initial measurement should be specified in the product

specification.

7.3.4 Test

All specimens shall be subjected to the test in accordance with 7.1.

7.3.5 Intermediate measurement

The specimen shall be taken from the temperature cycling chamber at the intermediate

measuring cycle specified in Table 1.

All specimens shall be subjected to the thermal resistance measurement for intermediate

measurement in accordance with 7.2.2.

All specimens shall be subjected to the ultrasonic flaw inspection for intermediate measurement

in accordance with 7.2.3.

7.3.6 Post-test treatment

After the evaluation test, if it is necessary to align the measurement condition, the specimen

shall be subjected to post-test conditioning specified in the product specification under the final

measurement conditions. The product specification may specify the recovery period to cool

down and the stabilizing temperature for the specimen.

7.3.7 Final judgment

The specimen shall be taken from the temperature cycling chamber at the end of the test.

At least one specimen shall be observed in the cross section to check the damage conditions

of the die attach region. The specimen for the cross section should be selected by the result of

ultrasonic inspection in accordance with 7.2.3.

– 12 – IEC 63215-2:2023 © IEC 2023

The test results should be evaluated in conjunction with the intermediate measurement results.

The recorded thermal resistance data and the crack propagation area ratio (die attach damage

data) should be analysed in correlation with each specimen individually.

If the thermal resistance value (R ) increased up to 20 %, then the failure cycles shall be

th

determined.

Once the test is completed, if the thermal resistance value (R ) is not reached to 20 %, the

th

specimen shall be evaluated by ultrasonic flaw inspection. If the horizontal crack propagation

area ratio reaches up to 30 %, then it is necessary to determine the failure cycles.

Once the test has finished up to 1 500 cycles, if the thermal resistance value (R ) is not reached

th

to 20 % and the crack propagation area ratio is not reached up to 30 %, the specimen is judged

to have performance index "Level 1" as shown in Annex C.

If the crack propagation area ratio at the end of the test criteria is significantly too small, the

increased rate of thermal resistance value (R ) of 20 % should be re-defined to a decreased

th

value (e.g. 30 %) to determine the failure cycles.

The measuring condition for the final measurement should be specified in the product

specification.

8 Failure cycle

The failure cycle of the specimen shall be the test cycles for which the end of the test criteria

specified in 7.1.4 or failure criteria specified in the product specification are reached, due to

crack propagation area at the die attach joint (interface).

The failure cycles for the temperature cycling test should be extrapolated from the thermal

resistance change during the test to reach the end of the test criteria in 7.1.4.

The representative failure cycles of the specimens under the same test conditions shall be

decided based on the statistical failure rate specified in the product specification. If the product

specification does not specify the details, then the shortest failure cycle number shall be taken.

As a reference of the reliability performance for the specimen, the reliability performance index

corresponding to the failure cycles in the temperature cycling test is as shown in Annex C.

9 Items to be specified in the product specification

The product specification shall specify the following items if applicable:

a) specification of the discrete type power electronic device (Clause 6)

b) evaluation test conditions, if other than specified in Table 1 (7.1.3);

c) end of test criteria (increasing ratio limit for thermal resistance) (7.1.4)

d) test preparation, if required (7.3.1)

e) preconditioning, if required (7.3.2)

f) initial measurement items and conditions (7.3.3)

g) post-test treatment (7.3.6)

h) final judgment items and conditions (7.3.7)

i) failure cycle and reliability performance level (Clause 8)

Annex A

(normative)

Thermal resistance measuring method at die attach region

A.1 Thermal resistance measuring method

A.1.1 General

For the temperature cycling test, the specimen specified in 6.1 is used. If the specimen which

is made of a TEG chip (refer to Figure B.1) is used, the top surface temperature of the TEG

chip can be estimated from the temperature characteristics of the heating resistor.

Figure A.1 shows an example of the structure of the specimen using a TEG chip.

Key

1 base substrate 2 TEG chip

3 terminal 4 bonding wires

5 adhesive

Figure A.1 – Example of the structure of the specimen using a TEG chip

A.1.2 Temperature characteristics measurement for TEG chip

The thermal characteristics of the heat resistance of the TEG chip specimen are obtained by

the following procedure:

a) put the specimen into the constant temperature chamber;

b) apply measuring current, for example 1 mA;

c) measure the temperature (T ) and voltage drop between terminals (U);

c

d) repeat b) and c) for at least three (3) different temperatures.

Figure A.2 shows an example of the measurement.

– 14 – IEC 63215-2:2023 © IEC 2023

Measuring current: 1mA

Set

temperature

T

V

c

°C °C mV

25 25,7 90,263 9

50 50,7 95,680 0

75 75,4 101,430 1

Figure A.2 – Example of temperature characteristics – TEG chip

A.1.3 Thermal resistance measurement method for TEG chip

If the specimen is made of a TEG chip, using the thermal resistance along with the thickness

measurement method as described in IEC TR 61189-3-914:2017, 6.3 and 6.4.6, and the

thermal resistance measuring equipment using a cold plate, the thermal resistance of the power

electronic device chip along with the thickness which represents the die attach region can be

obtained from the temperature of the TEG chip (T ) and the base plate temperature (T ).

j b

The thermal resistance along the whole thickness of the TEG chip (R ) is calculated by

th

Formula (A.1).

TT−

jb

R = (A.1)

th

W

where

R is the thermal resistance along the thickness between T and T (K /W)

th j s

T is the surface temperature of the TEG chip (°C)

j

T is the bottom surface temperature of the base plate (°C)

b

W is the TEG chip power (W)

Figure A.3 shows an example of the structure for the thermal resistance measurement for power

electronic device.

Key

1 base substrate 2 TEG chip

3 terminal 4 bonding wires

5 adhesive 6 die attach material

Thermal interface material (TIM)

7 8 base plate

(thermal conductivity: ≥ 1 W/m·K)

9 wind shield box

Figure A.3 – Example of structure for thermal resistance measurement

for a power electronic device

A.2 Correction of thermal resistance criteria

The relationship between the thermal resistance value and the crack propagation area ratio (die

attach damage) can depend on the die attach material. The characteristics of the thermal

resistance and the crack propagation area ratio are roughly compared with the die attach

materials.

– 16 – IEC 63215-2:2023 © IEC 2023

An example of the relationship between the thermal resistance value and the crack propagation

area ratio (die attach damage) which is dependent on the die attach materials is shown in

Figure A.4.

Figure A.4 – Example of relationship between thermal resistance and die attach damage

An example of the thermal resistance value and of the crack propagation area ratio (die attach

damage) examination result is shown in Table A.1 and Figure A.5, respectively.

Table A.1 – Example of thermal resistance value (R ) result

th

Unit in ºC/W

Test 0 cycle 500 cycles 1 000 cycles 1 500 cycles

R R ΔR R ΔR R ΔR

th th th th th th th

a 0,937 1,046 12 % 1,168 25 % 1,311 40 %

b 0,950 1,065 12 % 1,246 31 % 1,575 66 %

c 0,972 1,026 6 % 1,079 11 % 1,376 42 %

TCT condition:-40 °C to 175 °C, 1 cycle/h, air

Vase substrate: 60Cu-40Mo

Die attach material: Sn-95Pb

ΔR is the increased ratio from 0 cycle.

th

Figures are the crack propagation area ratio.

Figure A.5 – Example of ultrasonic flaw inspection result

The crack propagation area ratio of each TEG chip should be calculated by Formula (A.2).

A

B ×100

(A.2)

A

where

B is the crack propagation area ratio, expressed in percent (%);

A is the original die attach joint area;

A is the crack propagation area.

The crack propagation area shall be measured using ultrasonic flaw inspection equipment. In

addition, the image data should be processed by a two-value image recognition.

=

– 18 – IEC 63215-2:2023 © IEC 2023

Annex B

(informative)

Discrete type specimen preparation using a heating resistor TEG chip

B.1 Power electronic device specimen

B.1.1 General

Unless otherwise specified in the product specification, the power electronic device specimen

is as follows.

B.1.2 Power electronic device chip

The power electronic device chip is made of Si (silicon) and has the following characteristics:

– dimensions: 5 mm × 5 mm, 400 μm thickness;

– surface treatment: metallization of Ti-Ni-Au (titanium-nickel-gold) or Ag (silver) on the die

attach (bottom) side.

An example of a TEG chip simulating power electronic device chip is shown in Figure B.1.

(Bottom view) (Top view)

Key

Red colour pattern: bonding pad (0,3 mm thick Au)

Blue colour pattern: resistor circuit 1 (heater and thermal sensor)

Green colour pattern: resistor circuit 2 (heater and thermal sensor)

Figure B.1 – Example of TEG chip

B.1.3 Base substrate

The details of the base substrate are as follows:

– material: Cu (copper), Cu-W (copper-tungsten) or Cu-Mo (copper-molybdenum) used as

lead frame;

– dimensions:30 mm × 30 mm, 2 mm thickness;

– surface treatment: Ni/Ag (nickel/silver) or Ni/Au (nickel / gold) on die attach side, unless

otherwise specified by the product specification.

B.1.4 Package mould

The evaluation test can affect the resin mould used for package sealing of the power electronic

device and can cause damage or deterioration to the wire bonding other than the die attach

joint. Therefore, the specimen should not have any mould or the resin mould should be removed.

B.1.5 Surface treatment

If required by the product specification, the specified surface treatment is applied to the power

electronic device chip as in B.1.2 and to the base substrate as in B.1.3.

B.2 Die attach materials

Solder paste, sintered material made of Ag (silver) or Cu (copper) or conductive adhesive are

used as a die attach material.

NOTE Solder paste is made of flux, finely divided particles of solder and additives to promote wetting and to control

viscosity, tackiness, slumping, drying rate, etc.

Unless otherwise specified in the product specification, one of the solder alloys listed below (as

specified in IEC 61190-1-3) is used:

– 5 % mass fraction of Sn (tin) and 95 % mass fraction of Pb (lead);

– from 3,0 % to 4,0 % mass fraction of Ag (silver), from 0,5 % to 1,0 % mass fraction of Cu

(copper) and the remainder of Sn (tin).

EXAMPLE Sn-Ag-Cu ternary alloy such as Sn96,5Ag3Cu,5 alloy is used.

The product specification specifies the details of the solder paste.

B.3 Specimen preparation

For example, the die attach joint is made by reflow soldering. Depending on the die attach

material, a press joint system, or reduced pressure reflow or formic acid atmosphere reflow for

oxidation/reduction operation may be used to secure the joint.

An example of the specimen preparation procedure is as follows:

a) Unless otherwise specified in the product specification, the die attach material described in

Clause B.2 is printed on the test substrate described in B.1.3, with 50 μm to 100 μm

thickness for soldering or 20 μm to 50 μm thickness for sintering, and is of the same

dimensions, shape and arrangement as the power electronic device chip.

b) The power electronic device chip is placed onto the printed die attach material.

c) The die bonding equipment specified in 5.1 is used to melt and join the die attach material

with the temperature profile shown in Figure B.2, for example. The measuring point of the

temperature is the die attach region.

Figure B.2 shows an example of a typical reflow soldering profile for Sn96,5Ag3Cu,5 solder

alloy, as in IEC 61760-1:2020, Figure 14.

d) Wire bonding to make the connection for the power supply to the power electronic device

chip, if necessary.

– 20 – IEC 63215-2:2023 © IEC 2023

Continuous line: typical process (terminal temperature)

Dotted line: process limits. Bottom process limit (terminal temperature). Upper process limit (top surface temperature)

Figure B.2 – Typical reflow soldering profile for Sn96,5Ag3Cu,5 solder alloy

Figure B.3 shows an example of the TEG chip specimen for the evaluation test.

Key

1 TEG chip 2 base substrate

3 die bonding material 4 bonding wire

5 terminal 6 resistor element

Figure B.3 – Example of specimen – TEG chip

– 22 – IEC 63215-2:2023 © IEC 2023

Annex C

(informative)

Reliability performance index for die attach joint –

Discrete type power electronic device

The reliability performance index corresponding to the failure cycles in the temperature cycling

test is shown in Table C.1. For die attach materials applied to discrete type power electronic

device, this classification gives an index of applicability.

Table C.1 – Reliability performance index for die attach joint –

Discrete type power electronic device

TCT reliability

Temperature

T / T

performance Failure cycles

min max

range

index

°C °C

190-Level1 1 500≤

–40/150 190 190-Level2 1 000≥, <1 500

190-Lev

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...