IEC 60821:1991/Amd 1:1999

(Amendment)VMEbus — Microprocessor system bus for 1 byte to 4 byte data — Amendment 1

VMEbus — Microprocessor system bus for 1 byte to 4 byte data — Amendment 1

Bus VMEbus — Bus système à microprocesseurs pour données à 1 octet à 4 octets — Amendement 1

General Information

- Status

- Published

- Publication Date

- 14-Jan-1999

- Technical Committee

- ISO/IEC JTC 1/SC 25 - Interconnection of information technology equipment

- Current Stage

- 6060 - International Standard published

- Start Date

- 15-Jan-1999

- Due Date

- 16-Jul-2000

- Completion Date

- 15-Jan-1999

Relations

- Effective Date

- 22-May-2021

Overview

IEC 60821:1991/Amd 1:1999 is Amendment 1 to the IEC VMEbus specification for microprocessor system buses handling 1‑byte to 4‑byte data. Prepared by ISO/IEC JTC1/SC26 and published by the IEC, this amendment updates signal definitions, data‑transfer rules, arbitration and interrupt naming/behavior, mechanical board requirements, and several normative and informative appendices to improve interoperability and implementation clarity for VMEbus systems.

Key topics

- Signal and timing clarifications

- WRITE* is defined as a level‑significant signal strobed by the falling edge of the first data strobe (DSA*) and remains valid while any data strobe (DSA* or DSB*) is low.

- Data transfer capability rules

- D08(O) slave behavior clarified: D08(O) slaves MUST NOT drive DTACK* low for certain byte-location requests (e.g., BYTE(0), BYTE(2), BYTE(1-2), etc.).

- Tables and mnemonics updated so entries read “must accept” / “must monitor” rather than “can …”.

- Unaligned transfers (UAT)

- Revised UAT mnemonic table specifying which masters and slaves must accept or generate particular multi‑byte read/write cycles (quad, triple, double).

- Arbitration and requester behavior

- Naming corrections: BRO* → BR0*, BGOIN* → BG0IN*.

- FAIR ARBITER/requester rule: after grant, a requester must monitor its request line and must not re‑issue a new bus request until its request line has been high.

- Priority interrupt bus

- Interrupt lines renamed to IRQ1–IRQ7**; interrupt acknowledge line title standardized to IACK (asterisk removed in usages).

- Rules and permissions for interrupt drivers clarified.

- Mechanical specifications

- Board thickness requirement: boards MUST be 1.6 mm ± 0.2 mm (0.063 in ± 0.008 in) in the guide area.

- Appendices and metastability

- Appendix titles updated to indicate normative/informative status.

- Metastability/resynchronisation guidance updated; delay “F” should cover metastability resolution at the selected MTBF plus grant logic propagation.

Applications

- Hardware and embedded systems engineers implementing or verifying VMEbus motherboards, backplanes and modules.

- System integrators and test labs performing compliance, interoperability and conformance testing.

- Firmware and low‑level software teams coordinating timing, interrupt handling and bus arbitration behavior.

- Standards managers and procurement teams referencing mechanical and signaling requirements for VMEbus hardware.

Related standards

- This amendment is part of the broader VMEbus family and was prepared under ISO/IEC JTC 1/SC 26. Implementers should review the base IEC 60821:1991 document and other VMEbus specifications for complete compliance context.

Keywords: IEC 60821, VMEbus, amendment 1, microprocessor system bus, data transfer, unaligned transfers, arbitration, priority interrupt bus, board thickness, interoperability, compliance.

Get Certified

Connect with accredited certification bodies for this standard

BSI Group

BSI (British Standards Institution) is the business standards company that helps organizations make excellence a habit.

NYCE

Mexican standards and certification body.

Sponsored listings

Frequently Asked Questions

IEC 60821:1991/Amd 1:1999 is a standard published by the International Organization for Standardization (ISO). Its full title is "VMEbus — Microprocessor system bus for 1 byte to 4 byte data — Amendment 1". This standard covers: VMEbus — Microprocessor system bus for 1 byte to 4 byte data — Amendment 1

VMEbus — Microprocessor system bus for 1 byte to 4 byte data — Amendment 1

IEC 60821:1991/Amd 1:1999 is classified under the following ICS (International Classification for Standards) categories: 31.080.01 - Semiconductor devices in general; 35.160 - Microprocessor systems; 35.200 - Interface and interconnection equipment. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 60821:1991/Amd 1:1999 has the following relationships with other standards: It is inter standard links to IEC 60821:1991. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 60821:1991/Amd 1:1999 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

NORME CEI

INTERNATIONALE

IEC

INTERNATIONAL

STANDARD

AMENDEMENT 1

AMENDMENT 1

1999-01

Amendment 1

VMEbus –

Microprocessor system bus

for 1 byte to 4 byte data

Amendement 1

Bus VMEbus –

Bus système à microprocesseurs

pour données de 1 octet à 4 octets

IEC 1999 Droits de reproduction réservés Copyright - all rights reserved

International Electrotechnical Commission 3, rue de Varembé Geneva, Switzerland

Telefax: +41 22 919 0300 e-mail: inmail@iec.ch IEC web site http: //www.iec.ch

CODE PRIX

Commission Electrotechnique Internationale

PRICE CODE J

International Electrotechnical Commission

Pour prix, voir catalogue en vigueur

For price, see current catalogue

– 2 – 60821 Amend. 1 © IEC:1999(E)

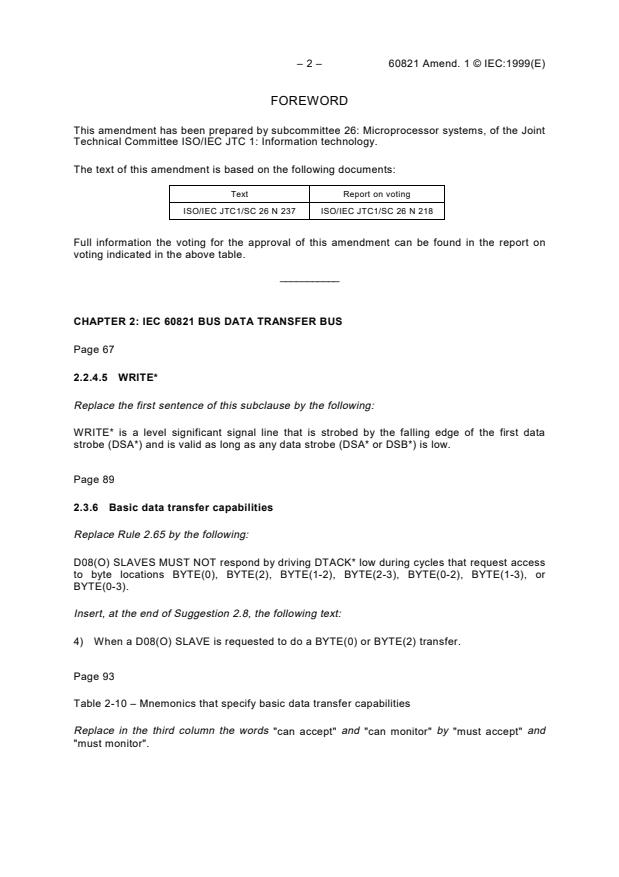

FOREWORD

This amendment has been prepared by subcommittee 26: Microprocessor systems, of the Joint

Technical Committee ISO/IEC JTC 1: Information technology.

The text of this amendment is based on the following documents:

Text Report on voting

ISO/IEC JTC1/SC 26 N 237 ISO/IEC JTC1/SC 26 N 218

Full information the voting for the approval of this amendment can be found in the report on

voting indicated in the above table.

___________

CHAPTER 2: IEC 60821 BUS DATA TRANSFER BUS

Page 67

2.2.4.5 WRITE*

Replace the first sentence of this subclause by the following:

WRITE* is a level significant signal line that is strobed by the falling edge of the first data

strobe (DSA*) and is valid as long as any data strobe (DSA* or DSB*) is low.

Page 89

2.3.6 Basic data transfer capabilities

Replace Rule 2.65 by the following:

D08(O) SLAVES MUST NOT respond by driving DTACK* low during cycles that request access

to byte locations BYTE(0), BYTE(2), BYTE(1-2), BYTE(2-3), BYTE(0-2), BYTE(1-3), or

BYTE(0-3).

Insert, at the end of Suggestion 2.8, the following text:

4) When a D08(O) SLAVE is requested to do a BYTE(0) or BYTE(2) transfer.

Page 93

Table 2-10 – Mnemonics that specify basic data transfer capabilities

Replace in the third column the words "can accept" and "can monitor" by "must accept" and

"must monitor".

60821 Amend. 1 © IEC:1999(E) – 3 –

2.3.7 Block transfer capabilities

Add, on page 95, at the end of Rule 2.12, the words "in the address space."

Replace, on page 97, at the end of the first sentence of Observation 2.87, "D08-D15" by

"D00-D15".

Page 99

Table 2-11 – Mnemonic that specifies block transfer capabilities

Replace, in the third column, the words "Can accept" and "Can monitor" by "Must accept" and

"Must monitor".

Page 101

Table 2-12 – Mnemonic that specifies read-modify-write capabilities

Replace, in the third column, the words "Can accept" and "Can monitor" by "Must accept" and

"Must monitor".

Page 103

2.3.9 Unaligned transfer capabilities

Page 105

Table 2-13 – Transferring 32 bits of data using multiple byte transfer cycles

Replace, in row B, line 3, and line 6, "Group 1, BYTE(0)" by "GROUP 2, BYTE(0)".

Replace, in row D, line 6, "D00-D23" by "D00-D07".

Page 107

Table 2-14 – Transferring 16 bits of data using multiple byte transfer cycles

Replace, in row F, line 1, "D08-D15" by "D00-D07".

Replace, in row F, line 2, "D16-D23" by "D08-D15".

RULE 2.6

Replace, at the beginning of the sentence, "D08(0)" by "D08(O)"

Replace the text before table 2-15 and after RULE 2.6 by:

Table 2-15 lists how the unaligned transfer (UAT) mnemonic is used to describe MASTERS

and SLAVES.

– 4 – 60821 Amend. 1 © IEC:1999(E)

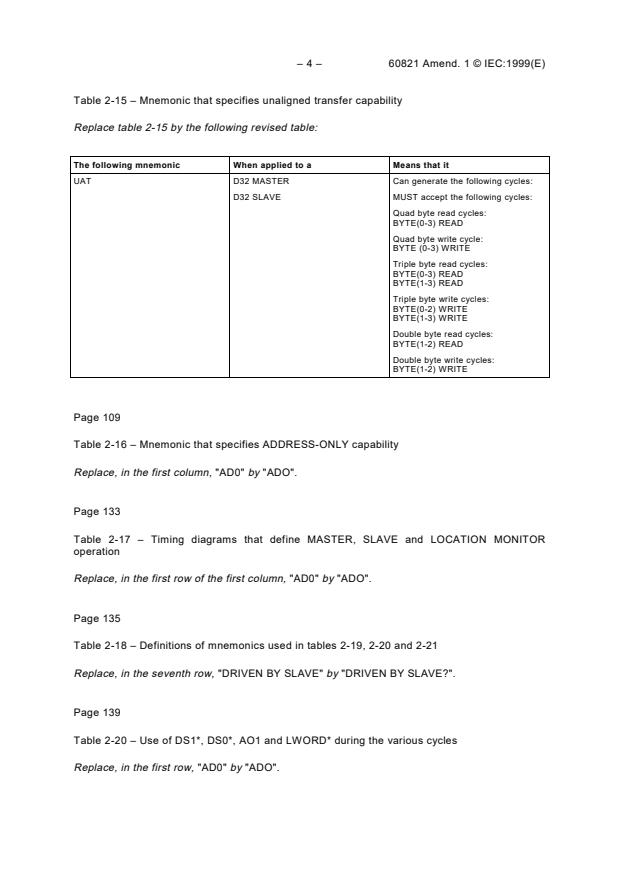

Table 2-15 – Mnemonic that specifies unaligned transfer capability

Replace table 2-15 by the following revised table:

The following mnemonic When applied to a Means that it

UAT D32 MASTER Can generate the following cycles:

D32 SLAVE MUST accept the following cycles:

Quad byte read cycles:

BYTE(0-3) READ

Quad byte write cycle:

BYTE (0-3) WRITE

Triple byte read cycles:

BYTE(0-3) READ

BYTE(1-3) READ

Triple byte write cycles:

BYTE(0-2) WRITE

BYTE(1-3) WRITE

Double byte read cycles:

BYTE(1-2) READ

Double byte write cycles:

BYTE(1-2) WRITE

Page 109

Table 2-16 – Mnemonic that specifies ADDRESS-ONLY capability

Replace, in the first column, "AD0" by "ADO".

Page 133

Table 2-17 – Timing diagrams that define MASTER, SLAVE and LOCATION MONITOR

operation

Replace, in the first row of the first column, "AD0" by "ADO".

Page 135

Table 2-18 – Definitions of mnemonics used in tables 2-19, 2-20 and 2-21

Replace, in the seventh row, "DRIVEN BY SLAVE" by "DRIVEN BY SLAVE?".

Page 139

Table 2-20 – Use of DS1*, DS0*, AO1 and LWORD* during the various cycles

Replace, in the first row, "AD0" by "ADO".

60821 Amend. 1 © IEC:1999(E) – 5 –

Page 141

Table 2-21 – Use of the data lines to transfer data

Replace, in the first row, "AD0" by "ADO".

CHAPTER 3: IEC 60821 BUS DATA TRANSFER BUS

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...