IEC 62530-2:2021

(Main)SystemVerilog - Part 2: Universal Verification Methodology Language Reference Manual

SystemVerilog - Part 2: Universal Verification Methodology Language Reference Manual

IEC 62530-2:2021(E) establishes the Universal Verification Methodology (UVM), a set of application programming

interfaces (APIs) that defines a base class library (BCL) definition used to develop modular, scalable, and reusable components for functional verification environments. The APIs and BCL are based on the IEEE standard for SystemVerilog, IEEE Std 1800™. This publication has the status of a double logo IEC/IEEE standard.

General Information

- Status

- Published

- Publication Date

- 25-Jul-2021

- Technical Committee

- TC 91 - Electronics assembly technology

- Current Stage

- DELPUB - Deleted Publication

- Start Date

- 11-Oct-2023

- Completion Date

- 13-Feb-2026

Relations

- Effective Date

- 05-Sep-2023

Overview

IEC 62530-2:2021 - SystemVerilog Part 2: Universal Verification Methodology Language Reference Manual specifies the Universal Verification Methodology (UVM) as a formal language reference. It establishes the UVM application programming interfaces (APIs) and a Base Class Library (BCL) definition used to develop modular, scalable, and reusable components for functional verification environments. The standard is a double‑logo IEC/IEEE publication and is based on the IEEE SystemVerilog language (IEEE Std 1800™).

Key Topics

This language reference documents the UVM API and class library in detail and organizes content into clear technical areas, including:

- Base classes and fundamental types (e.g., uvm_object, uvm_transaction, uvm_time)

- Reporting and recording mechanisms (uvm_report_message, report server, uvm_tr_database)

- Factory and object/component wrappers to support flexible construction and substitution

- Phasing and synchronization (predefined phases, domain management, objections)

- TLM interfaces for component communication (UVM TLM 1 & 2)

- Sequencing and sequencer classes (uvm_sequence, uvm_sequencer, sequence library)

- Predefined component classes (uvm_component, uvm_agent, uvm_driver, uvm_monitor)

- Policy utilities (printers, comparers, packers, copiers)

- Register layer and register model (uvm_reg_block, uvm_reg_map, uvm_reg_field, uvm_mem)

- Callbacks, barriers, pools and container classes to support modular verification architectures

These topics reflect the document’s table of contents and show the scope of the standardized APIs and class behaviors used in UVM-based verification.

Applications

IEC 62530-2:2021 is aimed at organizations and professionals who build or use SystemVerilog verification environments:

- Verification engineers developing functional verification testbenches for ASICs, SoCs, and FPGAs

- EDA tool vendors implementing or supporting UVM-compatible simulators, utilities, and libraries

- Hardware design teams who need standardized testbench components for reuse and interoperability

- Quality and validation teams establishing verification flows and regression frameworks

Using this standard helps teams create modular, scalable, and reusable verification components, accelerate testbench development, and improve cross‑tool compatibility.

Related Standards

- IEEE Std 1800™ (SystemVerilog) - the foundational language on which the UVM APIs are based

- IEC/IEEE double‑logo relationship - IEC 62530-2:2021 is published in conjunction with the IEEE UVM language standard

Keywords: IEC 62530-2:2021, UVM Language Reference Manual, Universal Verification Methodology, SystemVerilog, UVM, verification environment, TLM, register model, Base Class Library (BCL), APIs.

Get Certified

Connect with accredited certification bodies for this standard

BSI Group

BSI (British Standards Institution) is the business standards company that helps organizations make excellence a habit.

National Aerospace and Defense Contractors Accreditation Program (NADCAP)

Global cooperative program for special process quality in aerospace.

CARES (UK Certification Authority for Reinforcing Steels)

UK certification for reinforcing steels and construction.

Sponsored listings

Frequently Asked Questions

IEC 62530-2:2021 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "SystemVerilog - Part 2: Universal Verification Methodology Language Reference Manual". This standard covers: IEC 62530-2:2021(E) establishes the Universal Verification Methodology (UVM), a set of application programming interfaces (APIs) that defines a base class library (BCL) definition used to develop modular, scalable, and reusable components for functional verification environments. The APIs and BCL are based on the IEEE standard for SystemVerilog, IEEE Std 1800™. This publication has the status of a double logo IEC/IEEE standard.

IEC 62530-2:2021(E) establishes the Universal Verification Methodology (UVM), a set of application programming interfaces (APIs) that defines a base class library (BCL) definition used to develop modular, scalable, and reusable components for functional verification environments. The APIs and BCL are based on the IEEE standard for SystemVerilog, IEEE Std 1800™. This publication has the status of a double logo IEC/IEEE standard.

IEC 62530-2:2021 is classified under the following ICS (International Classification for Standards) categories: 25.040.01 - Industrial automation systems in general; 35.060 - Languages used in information technology. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 62530-2:2021 has the following relationships with other standards: It is inter standard links to IEC 62530-2:2023. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 62530-2:2021 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 62530-2 ®

Edition 1.0 2021-07

™

IEEE Std 1800.2

INTERNATIONAL

STANDARD

SystemVerilog –

Part 2: Universal Verification Methodology Language Reference Manual

All rights reserved. IEEE is a registered trademark in the U.S. Patent & Trademark Office, owned by the Institute of

Electrical and Electronics Engineers, Inc. Unless otherwise specified, no part of this publication may be reproduced

or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without

permission in writing from the IEC Central Office. Any questions about IEEE copyright should be addressed to the

IEEE. Enquiri es about obtaining additional rights to this publication and other information requests should be

addressed to the IEC or your local IEC member National Committee.

IEC Central Office Institute of Electrical and Electronics Engineers, Inc.

3, rue de Varembé 3 Park Avenue

CH-1211 Geneva 20 New York, NY 10016-5997

Switzerland United States of America

Tel.: +41 22 919 02 11 stds.info@ieee.org

info@iec.ch www.ieee.org

www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigendum or an amendment might have been published.

IEC publications search - webstore.iec.ch/advsearchform IEC online collection - oc.iec.ch

The advanced search enables to find IEC publications by a

Discover our powerful search engine and read freely all the

variety of criteria (reference number, text, technical publications previews. With a subscription you will always

committee, …). It also gives information on projects, replaced have access to up to date content tailored to your needs.

and withdrawn publications.

Electropedia - www.electropedia.org

IEC Just Published - webstore.iec.ch/justpublished

The world's leading online dictionary on electrotechnology,

Stay up to date on all new IEC publications. Just Published

containing more than 22 000 terminological entries in English

details all new publications released. Available online and

and French, with equivalent terms in 18 additional languages.

once a month by email.

Also known as the International Electrotechnical Vocabulary

(IEV) online.

IEC Customer Service Centre - webstore.iec.ch/csc

If you wish to give us your feedback on this publication or

need further assistance, please contact the Customer Service

Centre: sales@iec.ch.

IEC 62530-2 ®

Edition 1.0 2021-07

IEEE Std 1800.2™

INTERNATIONAL

STANDARD

SystemVerilog –

Part 2: Universal Verification Methodology Language Reference Manual

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

ICS 25.040.01; 35.060 ISBN 978-2-8322-9974-6

IEEE Std 1800.2 ™-2017

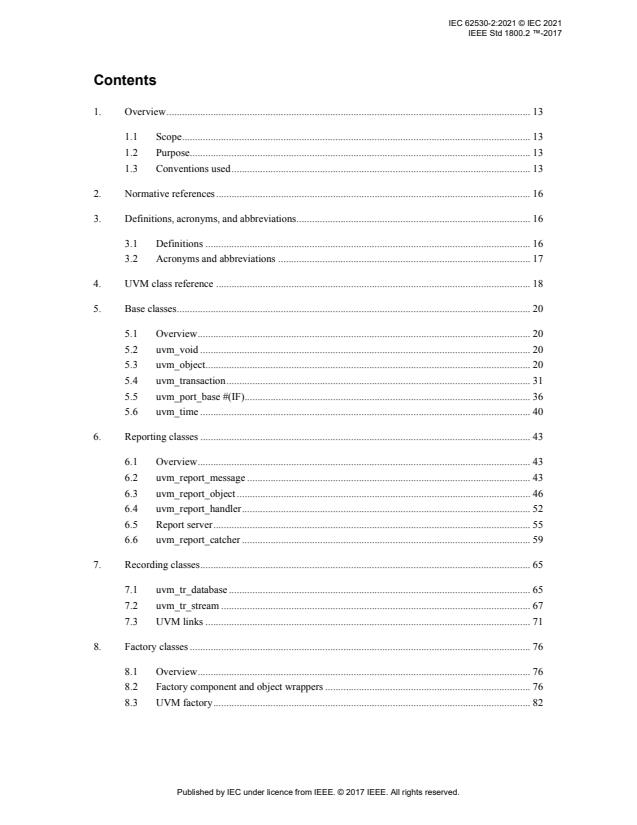

Contents

1. Overview. 13

1.1 Scope. 13

1.2 Purpose. 13

1.3 Conventions used. 13

2. Normative references. 16

3. Definitions, acronyms, and abbreviations. 16

3.1 Definitions . 16

3.2 Acronyms and abbreviations . 17

4. UVM class reference . 18

5. Base classes. 20

5.1 Overview. 20

5.2 uvm_void . 20

5.3 uvm_object. 20

5.4 uvm_transaction. 31

5.5 uvm_port_base #(IF). 36

5.6 uvm_time . 40

6. Reporting classes . 43

6.1 Overview. 43

6.2 uvm_report_message . 43

6.3 uvm_report_object . 46

6.4 uvm_report_handler. 52

6.5 Report server. 55

6.6 uvm_report_catcher . 59

7. Recording classes. 65

7.1 uvm_tr_database . 65

7.2 uvm_tr_stream . 67

7.3 UVM links . 71

8. Factory classes . 76

8.1 Overview. 76

8.2 Factory component and object wrappers . 76

8.3 UVM factory. 82

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800.2 ™-2017

9. Phasing. 89

9.1 Overview. 89

9.2 Implementation . 89

9.3 Phasing definition classes . 89

9.4 uvm_domain . 98

9.5 uvm_bottomup_phase. 99

9.6 uvm_task_phase. 100

9.7 uvm_topdown_phase . 101

9.8 Predefined phases . 102

10. Synchronization classes . 107

10.1 Event classes . 107

10.2 uvm_event_callback . 110

10.3 uvm_barrier. 111

10.4 Pool classes . 113

10.5 Objection mechanism . 114

10.6 uvm_heartbeat. 119

10.7 Callbacks classes. 121

11. Container classes. 126

11.1 Overview. 126

11.2 uvm_pool #(KEY,T). 126

11.3 uvm_queue #(T). 128

12. UVM TLM interfaces . 131

12.1 Overview. 131

12.2 UVM TLM 1. 131

12.3 UVM TLM 2. 148

13. Predefined component classes . 168

13.1 uvm_component. 168

13.2 uvm_test. 181

13.3 uvm_env. 182

13.4 uvm_agent. 182

13.5 uvm_monitor. 183

13.6 uvm_scoreboard. 183

13.7 uvm_driver #(REQ,RSP) . 184

13.8 uvm_push_driver #(REQ,RSP) . 184

13.9 uvm_subscriber. 185

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800.2 ™-2017

14. Sequences classes . 187

14.1 uvm_sequence_item. 187

14.2 uvm_sequence_base. 191

14.3 uvm_sequence #(REQ,RSP). 200

14.4 uvm_sequence_library . 201

15. Sequencer classes. 206

15.1 Overview. 206

15.2 Sequencer interface. 206

15.3 uvm_sequencer_base . 211

15.4 Common sequencer API . 217

15.5 uvm_sequencer #(REQ,RSP). 218

15.6 uvm_push_sequencer #(REQ,RSP) . 219

16. Policy classes . 220

16.1 uvm_policy . 220

16.2 uvm_printer. 222

16.3 uvm_comparer . 237

16.4 uvm_recorder . 243

16.5 uvm_packer. 251

16.6 uvm_copier . 257

17. Register layer . 260

17.1 Overview. 260

17.2 Global declarations . 260

18. Register model . 264

18.1 uvm_reg_block . 264

18.2 uvm_reg_map . 276

18.3 uvm_reg_file. 284

18.4 uvm_reg . 286

18.5 uvm_reg_field. 303

18.6 uvm_mem . 314

18.7 uvm_reg_indirect_data . 328

18.8 uvm_reg_fifo . 329

18.9 uvm_vreg . 332

18.10 uvm_vreg_field. 342

18.11 uvm_reg_cbs. 347

18.12 uvm_mem_mam . 352

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800.2 ™-2017

19. Register layer interaction with RTL design. 361

19.1 Generic register operation descriptors . 361

19.2 Classes for adapting between register and bus operations. 365

19.3 uvm_reg_predictor. 367

19.4 Register sequence classes . 369

19.5 uvm_reg_backdoor . 376

19.6 UVM HDL back-door access support routines. 379

Annex A (informative) Bibliography . 381

Annex B (normative) Macros and defines. 382

Annex C (normative) Configuration and resource classes .407

Annex D (normative) Convenience classes, interface, and methods. 422

Annex E (normative) Test sequences . 431

Annex F (normative) Package scope functionality. 443

Annex G (normative) Command line arguments. 466

Annex H (informative) Participants. 471

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800.2 ™-2017

SystemVerilog –

Part 2: Universal Verification Methodology Language Reference Manual

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international

co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and

in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports,

Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC document(s)"). Their

preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with

may participate in this preparatory work. International, governmental and non-governmental organizations liaising

with the IEC also participate in this preparation.

IEEE Standards documents are developed within IEEE Societies and Standards Coordinating Committees of the

IEEE Standards Association (IEEE SA) Standards Board. IEEE develops its standards through a consensus

development process, approved by the American National Standards Institute, which brings together volunteers

representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members

of IEEE and serve without compensation. While IEEE administers the process and establishes rules to promote

fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the

accuracy of any of the information contained in its standards. Use of IEEE Standards documents is wholly

voluntary. IEEE documents are made available for use subject to important notices and legal disclaimers (see

http://standards.ieee.org/ipr/disclaimers.html for more information).

IEC collaborates closely with IEEE in accordance with conditions determined by agreement between the two

organizations. This Dual Logo International Standard was jointly developed by the IEC and IEEE under the terms

of that agreement.

2) The formal decisions of IEC on technical matters express, as nearly as possible, an international consensus of

opinion on the relevant subjects since each technical committee has representation from all interested IEC

National Committees. The formal decisions of IEEE on technical matters, once consensus within IEEE Societies

and Standards Coordinating Committees has been reached, is determined by a balanced ballot of materially

interested parties who indicate interest in reviewing the proposed standard. Final approval of the IEEE standards

document is given by the IEEE Standards Association (IEEE SA) Standards Board.

3) IEC/IEEE Publications have the form of recommendations for international use and are accepted by IEC National

Committees/IEEE Societies in that sense. While all reasonable efforts are made to ensure that the technical

content of IEC/IEEE Publications is accurate, IEC or IEEE cannot be held responsible for the way in which they

are used or for any misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

(including IEC/IEEE Publications) transparently to the maximum extent possible in their national and regional

publications. Any divergence between any IEC/IEEE Publication and the corresponding national or regional

publication shall be clearly indicated in the latter.

5) IEC and IEEE do not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC and IEEE are not responsible

for any services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or IEEE or their directors, employees, servants or agents including individual

experts and members of technical committees and IEC National Committees, or volunteers of IEEE Societies and

the Standards Coordinating Committees of the IEEE Standards Association (IEEE SA) Standards Board, for any

personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for

costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC/IEEE

Publication or any other IEC or IEEE Publications.

8) Attention is drawn to the normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that implementation of this IEC/IEEE Publication may require use of material

covered by patent rights. By publication of this standard, no position is taken with respect to the existence or

validity of any patent rights in connection therewith. IEC or IEEE shall not be held responsible for identifying

Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or

scope of Patent Claims or determining whether any licensing terms or conditions provided in connection with

submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory.

Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk

of infringement of such rights, is entirely their own responsibility.

IEC 62530-2/IEEE Std 1800.2 was processed through IEC technical committee 91: Electronics

assembly technology, under the IEC/IEEE Dual Logo Agreement. It is an International Standard.

IEEE Std 1800.2 ™-2017

The text of this International Standard is based on the following documents:

IEEE Std FDIS Report on voting

1800.2 (2017) 91/1713/FDIS 91/1725/RVD

Full information on the voting for its approval can be found in the report on voting indicated in

the above table.

The language used for the development of this International Standard is English.

The IEC Technical Committee and IEEE Technical Committee have decided that the contents

of this document will remain unchanged until the stability date indicated on the IEC website

under webstore.iec.ch in the data related to the specific document. At this date, the document

will be

• reconfirmed,

• withdrawn,

• replaced by a revised edition, or

• amended.

IEEE Std 1800.2™-2017

IEEE Standard for Universal

Verification Methodology Language

Reference Manual

Sponsor

Design Automation Standards Committee

of the

IEEE Computer Society

Approved 14 February 2017

IEEE-SA Standards Board

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800.2 ™-2017

Grateful acknowledgment is made for permission to use the following source material:

Accellera Systems Initiative—The Universal Verification Methodology (UVM)

pre-IEEE Class Reference.

Abstract: The Universal Verification Methodology (UVM) that can improve interoperability, reduce

the cost of using intellectual property (IP) for new projects or electronic design automation (EDA)

tools, and make it easier to reuse verification components is provided. Overall, using this standard

will lower verification costs and improve design quality throughout the industry. The primary

audiences for this standard are the implementors of the UVM base class library, the implementors

of tools supporting the UVM base class library, and the users of the UVM base class library.

Keywords: agent, blocking, callback, class, component, consumer, driver, event, export, factory,

function, generator, IEEE 1800.2™, member, method, monitor, non-blocking, phase, port, register,

resource, sequence, sequencer, transaction level modeling, verification methodology

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800.2 ™-2017

Important Notices and Disclaimers Concerning IEEE Standards Documents

IEEE documents are made available for use subject to important notices and legal disclaimers. These notices

and disclaimers, or a reference to this page, appear in all standards and may be found under the heading

“Important Notices and Disclaimers Concerning IEEE Standards Documents.” They can also be obtained on

request from IEEE or viewed at http://standards.ieee.org/IPR/disclaimers.html.

Notice and Disclaimer of Liability Concerning the Use of IEEE Standards

Documents

IEEE Standards documents (standards, recommended practices, and guides), both full-use and trial-use, are

developed within IEEE Societies and the Standards Coordinating Committees of the IEEE Standards

Association (“IEEE-SA”) Standards Board. IEEE (“the Institute”) develops its standards through a

consensus development process, approved by the American National Standards Institute (“ANSI”), which

brings together volunteers representing varied viewpoints and interests to achieve the final product. IEEE

Standards are documents developed through scientific, academic, and industry-based technical working

groups. Volunteers in IEEE working groups are not necessarily members of the Institute and participate

without compensation from IEEE. While IEEE administers the process and establishes rules to promote

fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the

accuracy of any of the information or the soundness of any judgments contained in its standards.

IEEE Standards do not guarantee or ensure safety, security, health, or environmental protection, or ensure

against interference with or from other devices or networks. Implementers and users of IEEE Standards

documents are responsible for determining and complying with all appropriate safety, security,

environmental, health, and interference protection practices and all applicable laws and regulations.

IEEE does not warrant or represent the accuracy or content of the material contained in its standards, and

expressly disclaims all warranties (express, implied and statutory) not included in this or any other

document relating to the standard, including, but not limited to, the warranties of: merchantability; fitness

for a particular purpose; non-infringement; and quality, accuracy, effectiveness, currency, or completeness of

material. In addition, IEEE disclaims any and all conditions relating to: results; and workmanlike effort.

IEEE standards documents are supplied “AS IS” and “WITH ALL FAULTS.”

Use of an IEEE standard is wholly voluntary. The existence of an IEEE standard does not imply that there

are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to

the scope of the IEEE standard. Furthermore, the viewpoint expressed at the time a standard is approved and

issued is subject to change brought about through developments in the state of the art and comments

received from users of the standard.

In publishing and making its standards available, IEEE is not suggesting or rendering professional or other

services for, or on behalf of, any person or entity nor is IEEE undertaking to perform any duty owed by any

other person or entity to another. Any person utilizing any IEEE Standards document, should rely upon his

or her own independent judgment in the exercise of reasonable care in any given circumstances or, as

appropriate, seek the advice of a competent professional in determining the appropriateness of a given IEEE

standard.

IN NO EVENT SHALL IEEE BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL,

EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO:

PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR

BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY,

WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR

OTHERWISE) ARISING IN ANY WAY OUT OF THE PUBLICATION, USE OF, OR RELIANCE UPON

ANY STANDARD, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE AND

REGARDLESS OF WHETHER SUCH DAMAGE WAS FORESEEABLE.

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800.2 ™-2017

Translations

The IEEE consensus development process involves the review of documents in English only. In the event

that an IEEE standard is translated, only the English version published by IEEE should be considered the

approved IEEE standard.

Official statements

A statement, written or oral, that is not processed in accordance with the IEEE-SA Standards Board

Operations Manual shall not be considered or inferred to be the official position of IEEE or any of its

committees and shall not be considered to be, or be relied upon as, a formal position of IEEE. At lectures,

symposia, seminars, or educational courses, an individual presenting information on IEEE standards shall

make it clear that his or her views should be considered the personal views of that individual rather than the

formal position of IEEE.

Comments on standards

Comments for revision of IEEE Standards documents are welcome from any interested party, regardless of

membership affiliation with IEEE. However, IEEE does not provide consulting information or advice

pertaining to IEEE Standards documents. Suggestions for changes in documents should be in the form of a

proposed change of text, together with appropriate supporting comments. Since IEEE standards represent a

consensus of concerned interests, it is important that any responses to comments and questions also receive

the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and

Standards Coordinating Committees are not able to provide an instant response to comments or questions

except in those cases where the matter has previously been addressed. For the same reason, IEEE does not

respond to interpretation requests. Any person who would like to participate in revisions to an IEEE

standard is welcome to join the relevant IEEE working group.

Comments on standards should be submitted to the following address:

Secretary, IEEE-SA Standards Board

445 Hoes Lane

Piscataway, NJ 08854 USA

Laws and regulations

Users of IEEE Standards documents should consult all applicable laws and regulations. Compliance with the

provisions of any IEEE Standards document does not imply compliance to any applicable regulatory

requirements. Implementers of the standard are responsible for observing or referring to the applicable

regulatory requirements. IEEE does not, by the publication of its standards, intend to urge action that is not

in compliance with applicable laws, and these documents may not be construed as doing so.

Copyrights

IEEE draft and approved standards are copyrighted by IEEE under U.S. and international copyright laws.

They are made available by IEEE and are adopted for a wide variety of both public and private uses. These

include both use, by reference, in laws and regulations, and use in private self-regulation, standardization,

and the promotion of engineering practices and methods. By making these documents available for use and

adoption by public authorities and private users, IEEE does not waive any rights in copyright to the

documents.

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800.2 ™-2017IEEE Std 1800.2 ™-2017

Photocopies

Subject to payment of the appropriate fee, IEEE will grant users a limited, non-exclusive license to

photocopy portions of any individual standard for company or organizational internal use or individual, non-

commercial use only. To arrange for payment of licensing fees, please contact Copyright Clearance Center,

Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; +1 978 750 8400. Permission to

photocopy portions of any individual standard for educational classroom use can also be obtained through

the Copyright Clearance Center.

Updating of IEEE Standards documents

Users of IEEE Standards documents should be aware that these documents may be superseded at any time

by the issuance of new editions or may be amended from time to time through the issuance of amendments,

corrigenda, or errata. An official IEEE document at any point in time consists of the current edition of the

document together with any amendments, corrigenda, or errata then in effect.

Every IEEE standard is subjected to review at least every ten years. When a document is more than ten years

old and has not undergone a revision process, it is reasonable to conclude that its contents, although still of

some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that

they have the latest edition of any IEEE standard.

In order to determine whether a given document is the current edition and whether it has been amended

through the issuance of amendments, corrigenda, or errata, visit the IEEE-SA Website at http://

ieeexplore.ieee.org/ or contact IEEE at the address listed previously. For more information about the IEEE-

SA or IEEE’s standards development process, visit the IEEE-SA Website at http://standards.ieee.org.

Errata

Errata, if any, for all IEEE standards can be accessed on the IEEE-SA Website at the following URL: http://

standards.ieee.org/findstds/errata/index.html. Users are encouraged to check this URL for errata

periodically.

Patents

Attention is called to the possibility that implementation of this standard may require use of subject matter

covered by patent rights. By publication of this standard, no position is taken by the IEEE with respect to the

existence or validity of any patent rights in connection therewith. If a patent holder or patent applicant has

filed a statement of assurance via an Accepted Letter of Assurance, then the statement is listed on the IEEE-

SA Website at http://standards.ieee.org/about/sasb/patcom/patents.html. Letters of Assurance may indicate

whether the Submitter is willing or unwilling to grant licenses under patent rights without compensation or

under reasonable rates, with reasonable terms and conditions that are demonstrably free of any unfair

discrimination to applicants desiring to obtain such licenses.

Essential Patent Claims may exist for which a Letter of Assurance has not been received. The IEEE is not

responsible for identifying Essential Patent Claims for which a license may be required, for conducting

inquiries into the legal validity or scope of Patents Claims, or determining whether any licensing terms or

conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing

agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that

determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their

own responsibility. Further information may be obtained from the IEEE Standards Association.

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800.2 ™-2017

Introduction

This introduction is not part of IEEE Std 1800.2-2017, IEEE Standard for Universal Verification Methodology

Language Reference Manual.

Verification has evolved into a complex project that often spans internal and external teams, but the

discontinuity associated with multiple, incompatible methodologies among those teams can limit

productivity. The Universal Verification Methodology (UVM) Language Reference Manual (LRM)

addresses verification complexity and interoperability within companies and throughout the electronics

industry for both novice and advanced teams while also providing consistency. While UVM is revolutionary,

being the first verification methodology to be standardized, it is also evolutionary, as it is built on the Open

Verification Methodology (OVM), which combined the Advanced Verification Methodology (AVM) with

the Universal Reuse Methodology (URM) and concepts from the e Reuse Methodology (eRM).

Furthermore, UVM also infuses concepts and code from the Verification Methodology Manual (VMM),

plus the collective experience and knowledge of the over 300 members of the Accellera UVM Working

Group to help standardize verification methodology. Finally, the transaction level modeling (TLM) facilities

in UVM are based on what was developed by Open SystemC Initiative (OSCI) for SystemC, though they are

not an exact replication or re-implementation of the SystemC TLM library.

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Std 1800.2 ™-2017IEEE Std 1800.2 ™-2017

This is a copyrighted Published by IEC under licence IEEE Standard. For personal from IEEE. © 2017 IEEE. or standards development All rights reserved.use only.

IEEE Standard for Universal

Verification Methodology Language

Reference Manual

1. Overview

1.1 Scope

This standard establishes the Universal Verification Methodology (UVM), a set of application programming

interfaces (APIs) that defines a base class library (BCL) definition used to develop modular, scalable, and

reusable components for functional verification environments. The APIs and BCL are based on the IEEE

standard for SystemVerilog, IEEE Std 1800™.

1.2 Purpose

Verification components and environments are currently created in different forms, making interoperability

among verification tools and/or geographically dispersed design environments both time consuming to

develop and error prone. The results of the UVM standardization effort will improve interoperability and

reduce the cost of repurchasing and rewriting intellectual property (IP) for each new project or electronic

design automation (EDA) tool, as well as make it easier to reuse verification components. Overall, the UVM

standardization effort will lower verification costs and improve design quality throughout the industry.

1.3 Conventions used

The conventions used throughout the document are as follows:

— UVM is case-sensitive.

— Any syntax examples shown in this standard are informative. They are intended to illustrate the

usage of UVM constructs in a simple context and do not define the full syntax.

1.3.1 Visual cues (meta-syntax)

Bold shows required keywords and/or special characters, e.g., uvm_component.

Italics shows variables

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...