ASTM F1388-92(2000)

(Test Method)Standard Test Method for Generation Lifetime and Generation Velocity of Silicon Material by Capacitance-Time Measurements of Metal-Oxide-Silicon (MOS) Capacitors (Withdrawn 2003)

Standard Test Method for Generation Lifetime and Generation Velocity of Silicon Material by Capacitance-Time Measurements of Metal-Oxide-Silicon (MOS) Capacitors (Withdrawn 2003)

SCOPE

This standard was transferred to SEMI (www.semi.org) May 2003

1.1 This test method covers the measurement of generation lifetime and generation velocity of silicon wafers.

1.2 The measurement requires the fabrication of a guard-ring MOS (Metal-Oxide-Silicon) capacitor. This test method is therefore destructive to the silicon wafer.

1.3 This test may also be applied to semiconductor materials other than silicon and to insulators other than silicon dioxide, but the details of capacitor fabrication and the analyses and interpretation of data in such cases are not given in this test method.

1.4 Both p- and n-type silicon in the doping range from 1013 to 10 17 cm-3 can be evaluated by this test method. The approximate range of generation lifetime that can be measured is 1µs to 10 ms.

1.5 The test method is applicable to both bulk and epitaxial silicon. If epitaxial silicon is used, the epitaxial layer must be of the same conductivity type as the substrate and should be at least twice as thick as the maximum depletion width in deep depletion to avoid errors caused by the proximity of the epitaxial interface (see 12.4).

1.6 It is necessary to complete the measurements described in Test Method F 1153 before performing the measurements described in this test method to determine the values of maximum capacitance, equilibrium minimum capacitance, and doping density.

1.7 A digital computer capable of controlling the instruments and recording data is required and significantly simplifies and improves the accuracy of the data acquisition and analysis process.

1.8 This standard does not purport to address all of the safety problems, if any, associated with its use. It is the responsibility of the user of this standard to establish appropriate safety and health practices and determine the applicability of regulatory limitations prior to use. Specific hazard statements are given in 11.5 and 11.8.

General Information

Standards Content (Sample)

NOTICE: This standard has either been superceded and replaced by a new version or discontinued.

Contact ASTM International (www.astm.org) for the latest information.

Designation: F 1388 – 92 (Reapproved 2000)

Standard Test Method for

Generation Lifetime and Generation Velocity of Silicon

Material by Capacitance-Time Measurements of Metal-Oxide-

Silicon (MOS) Capacitors

This standard is issued under the fixed designation F 1388; the number immediately following the designation indicates the year of

original adoption or, in the case of revision, the year of last revision. A number in parentheses indicates the year of last reapproval. A

superscript epsilon (e) indicates an editorial change since the last revision or reapproval.

1. Scope 2. Referenced Documents

1.1 This test method covers the measurement of generation 2.1 ASTM Standards:

lifetime and generation velocity of silicon wafers. F 1153 Test Method for Characterization of Metal-Oxide-

1.2 The measurement requires the fabrication of a guard- Silicon (MOS) Structures by Capacitance-Voltage Mea-

ring MOS (Metal-Oxide-Silicon) capacitor. This test method is surements

therefore destructive to the silicon wafer. F 1241 Terminology of Silicon Technology

1.3 This test may also be applied to semiconductor materials

3. Terminology

other than silicon and to insulators other than silicon dioxide,

3.1 Definitions of Terms Specific to This Standard:

but the details of capacitor fabrication and the analyses and

interpretation of data in such cases are not given in this test 3.1.1 generation lifetime—the average time to create an

electron-hole pair in the space charge region of a reverse-

method.

1.4 Both p- and n-type silicon in the doping range from 10 biased MOS capacitor.

17 −3

3.1.2 generation velocity—the component of the electron-

to 10 cm can be evaluated by this test method. The

approximate range of generation lifetime that can be measured hole pair carrier creation that is independent of the width of the

depletion region. This component is a lumped term composed

is1μsto10ms.

1.5 The test method is applicable to both bulk and epitaxial of electron-hole pair creation from the surface and the quasi-

neutral bulk.

silicon. If epitaxial silicon is used, the epitaxial layer must be

of the same conductivity type as the substrate and should be at 3.1.3 guard ring—a ring of metal surrounding an MOS

capacitor that is spaced less than 10 μm from the periphery of

least twice as thick as the maximum depletion width in deep

depletion to avoid errors caused by the proximity of the the capacitor electrode and that can be biased independently

from the capacitor electrode (see Fig. 1).

epitaxial interface (see 12.4).

1.6 It is necessary to complete the measurements described 3.2 Other terms as defined in Terminology F 1241: Proper

nomenclature for terms such as “equilibrium inversion capaci-

in Test Method F 1153 before performing the measurements

described in this test method to determine the values of tance”, “doping density” and other terms used in this test

method and in Test Method F 1153 are currently under review

maximum capacitance, equilibrium minimum capacitance, and

doping density. and a common set is being developed. Until this set is defined,

1.7 A digital computer capable of controlling the instru- some differences between these test methods, Test Method

F 1153, and Terminology F 1241 will exist.

ments and recording data is required and significantly simpli-

fies and improves the accuracy of the data acquisition and

4. Summary of Test Method

analysis process.

4.1 The small-signal high-frequency capacitance of an MOS

1.8 This standard does not purport to address all of the

capacitor is measured as a function of time, after the capacitor

safety problems, if any, associated with its use. It is the

has been subjected to a voltage step from accumulation to

responsibility of the user of this standard to establish appro-

inversion. The generation lifetime and generation velocity are

priate safety and health practices and determine the applica-

determined from an analysis of the capacitance-time data.

bility of regulatory limitations prior to use. Specific hazard

4.2 The following assumptions are made in the analysis of

statements are given in 11.5 and 11.8.

the capacitance-time data to determine the generation lifetime

and generation velocity:

4.2.1 The majority carrier density is zero within the deple-

This test method is under the jurisdiction of ASTM Committee F01 on

tion region and equal to the doping density outside; the

Electronics and is the direct responsibility of Subcommittee F01.06 on Electrical

and Optical Measurement.

Current edition approved May 15, 1992. Published July 1992.

Annual Book of ASTM Standards, Vol 10.05.

Copyright © ASTM, 100 Barr Harbor Drive, West Conshohocken, PA 19428-2959, United States.

NOTICE: This standard has either been superceded and replaced by a new version or discontinued.

Contact ASTM International (www.astm.org) for the latest information.

F 1388

temperature and destructive nature of the test, such inspection

should be restricted to a small number of wafers. In the absence

of an interlaboratory evaluation of the precision of this test

method, its use for materials acceptance is not recommended

unless the parties to the test mutually agree on the method’s

repeatability and on the correlation they can obtain.

5.2.2 Contamination Monitoring of Processing Equipment,

Materials, or Procedures—Such monitoring will require using

silicon wafers of known generation lifetime and generation

velocity, obtained from lots sampled by previous MOS

capacitance-time characterization, to fabricate the MOS ca-

pacitors. The results can then be compared to the known

material values to determine the effect of the processing. Due

to variations in generation lifetime and generation velocity of

typical groups of silicon wafers, a large number of measure-

ments may be required to produce statistically significant

results.

5.2.3 Research and development purposes for the evaluation

of new materials, processes, and methods involved in the

fabrication of semiconductor devices.

6. Interferences and Sources of Errors

6.1 Instrumentation Errors—Typical errors due to instru-

mentation include the following sources:

6.1.1 Stray Capacitance, Inductance, Conductance, Resis-

tance, and Phase Errors—Errors are caused by excessive

lengths of connecting cable between the capacitance meter and

the measurement fixture. Carefully review and follow the

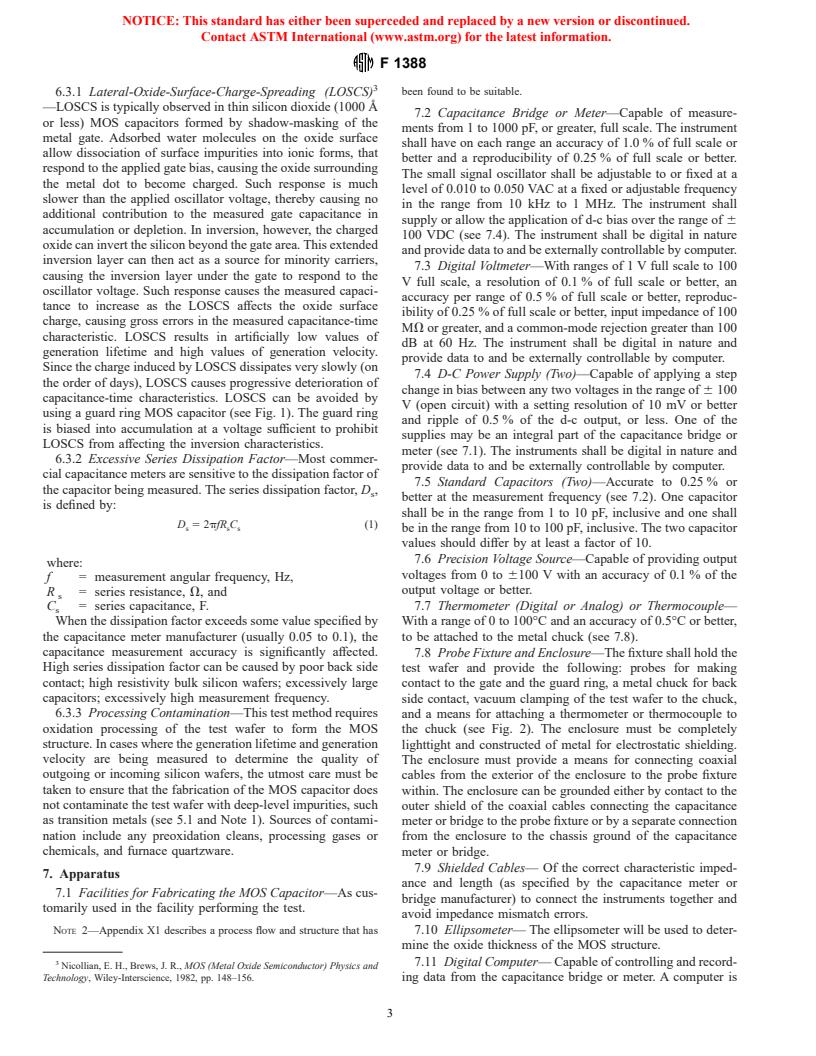

FIG. 1 Guard Ring Capacitor Diagrams

capacitance meter or bridge manufacturer’s recommendations

regarding cable length and necessary correction factors.

transition at the edge of the depletion region is a step function

6.1.2 Improper Compensation of Stray Capacitance, Induc-

(depletion approximation).

tance, Conductance and Resistance Associated with the Mea-

4.2.2 The voltage drop across the inversion layer is zero.

surement Fixture—Such errors can cause the calculated value

4.2.3 The doping density of the silicon wafer (or epitaxial

of the generation lifetime to increase, and in excessive cases,

layer) is known and is constant throughout the wafer (or layer).

cause the calculated lifetime to be negative.

4.2.4 The relative dielectric constants of the silicon and of

6.1.3 Poor Bias Stability—Any disturbance in bias during

the silicon dioxide are known and constant throughout the

the measurement will result in errors. Some commercially

materials.

available capacitance meters and bridges drop their internal

bias supplies to zero volts during autoranging, causing errors in

5. Significance and Use

the capacitance-time characteristic.

5.1 Generation lifetime and generation velocity are strongly

6.2 Measurement Fixture and Enclosure Errors—Typical

influenced by electrically active deep-level impurities and

errors due to the measurement fixture and enclosure include the

physical imperfections in the silicon, and are thus an indication

following sources:

of the quality of the silicon wafer. Such electrically active

6.2.1 Poor Temperature Stability—Such instability is typi-

deep-level impurities and physical imperfections can cause

cally due to stage motors, unbalanced thermal chucks, etc.

excessive p-n junction leakage, poor dynamic random access

Since the capacitance-time characteristic is strongly

memory (RAM) refresh performance, and “dark current”

temperature-dependent, a known and stable capacitor tempera-

degradation in computer-controlled display (CCD) memories,

ture is essential. The temperature should vary by no more than

delay lines, filters, and imagers.

1°C during the measurement.

6.2.2 Light Leaks— High-quality MOS capacitors are ex-

NOTE 1—The lifetime measured by this test method will be that of the

tremely sensitive to low-level light (as their use in CCD

processed material, not necessarily that of the virgin silicon. Extreme care

needs to be taken to ensure that such aspects of MOS capacitor fabrication

imagers attests). Every possible source of light must be

as pre-oxidation clean process gases, chemicals, and furnace quartzware

eliminated. This includes light from hinges, clear plastic

do not introduce lifetime altering contaminants (see also 6.3.3).

vacuum lines, door edges, etc. Light leakage causes the

5.2 This test method is suitable for monitoring the genera- calculated generation velocity to be increased due to electron-

tion lifetime and generation velocity of silicon wafers in the hole pair formation by the action of the light.

following situations: 6.3 MOS Capacitor Structure Related Errors—Typical er-

5.2.1 Incoming and Outgoing Inspection of Silicon rors due to the MOS capacitor structure include the following

Wafers—Due to the length of measurement time at room sources:

NOTICE: This standard has either been superceded and replaced by a new version or discontinued.

Contact ASTM International (www.astm.org) for the latest information.

F 1388

been found to be suitable.

6.3.1 Lateral-Oxide-Surface-Charge-Spreading (LOSCS)

˚

—LOSCS is typically observed in thin silicon dioxide (1000 A

7.2 Capacitance Bridge or Meter—Capable of measure-

or less) MOS capacitors formed by shadow-masking of the

ments from 1 to 1000 pF, or greater, full scale. The instrument

metal gate. Adsorbed water molecules on the oxide surface

shall have on each range an accuracy of 1.0 % of full scale or

allow dissociation of surface impurities into ionic forms, that

better and a reproducibility of 0.25 % of full scale or better.

respond to the applied gate bias, causing the oxide surrounding

The small signal oscillator shall be adjustable to or fixed at a

the metal dot to become charged. Such response is much

level of 0.010 to 0.050 VAC at a fixed or adjustable frequency

slower than the applied oscillator voltage, thereby causing no

in the range from 10 kHz to 1 MHz. The instrument shall

additional contribution to the measured gate capacitance in

supply or allow the application of d-c bias over the range of 6

accumulation or depletion. In inversion, however, the charged

100 VDC (see 7.4). The instrument shall be digital in nature

oxide can invert the silicon beyond the gate area. This extended

and provide data to and be externally controllable by computer.

inversion layer can then act as a source for minority carriers,

7.3 Digital Voltmeter—With ranges of 1 V full scale to 100

causing the inversion layer under the gate to respond to the

V full scale, a resolution of 0.1 % of full scale or better, an

oscillator voltage. Such response causes the measured capaci-

accuracy per range of 0.5 % of full scale or better, reproduc-

tance to increase as the LOSCS affects the oxide surface

ibility of 0.25 % of full scale or better, input impedance of 100

charge, causing gross errors in the measured capacitance-time

MV or greater, and a common-mode rejection greater than 100

characteristic. LOSCS results in artificially low values of

dB at 60 Hz. The instrument shall be digital in nature and

generation lifetime and high values of generation velocity.

provide data to and be externally controllable by computer.

Since the charge induced by LOSCS dissipates very slowly (on

7.4 D-C Power Supply (Two)—Capable of applying a step

the order of days), LOSCS causes progressive deterioration of

change in bias between any two voltages in the range of 6 100

capacitance-time characteristics. LOSCS can be avoided by

V (open circuit) with a setting resolution of 10 mV or better

using a guard ring MOS capacitor (see Fig. 1). The guard ring

and ripple of 0.5 % of the d-c output, or less. One of the

is biased into accumulation at a voltage sufficient to prohibit

supplies may be an integral part of the capacitance bridge or

LOSCS from affecting the inversion characteristics.

meter (see 7.1). The instruments shall be digital in nature and

6.3.2 Excessive Series Dissipation Factor—Most commer-

provide data to and be externally controllable by computer.

cial capacitance meters are sensitive to the dissipation factor of

7.5 Standard Capacitors (Two)—Accurate to 0.25 % or

the capacitor being measured. The series dissipation factor, D ,

s

better at the measurement frequency (see 7.2). One capacitor

is defined by:

shall be in the range from 1 to 10 pF, inclusive and one shall

D 5 2pfR C (1)

s s s

be in the range from 10 to 100 pF, inclusive. The two capacitor

values should differ by at least a factor of 10.

7.6 Precision Voltage Source—Capable of providing output

where:

voltages from 0 to 6100 V with an accuracy of 0.1 % of the

f = measurement angular frequency, Hz,

output voltage or better.

R = series resistance, V, and

s

C = series capacitance, F. 7.7 Thermometer (Digital or Analog) or Thermocouple—

s

When the dissipation factor exceeds some value specified by With a range of 0 to 100°C and an accuracy of 0.5°C or better,

the capacitance meter manufacturer (usually 0.05 to 0.1), the to be attached to the metal chuck (see 7.8).

capacitance measurement accuracy is significantly affected. 7.8 Probe Fixture and Enclosure—The fixture shall hold the

High series dissipation factor can be caused by poor back side

test wafer and provide the following: probes for making

contact; high resistivity bulk silicon wafers; excessively large

contact to the gate and the guard ring, a metal chuck for back

capacitors; excessively high measurement frequency.

side contact, vacuum clamping of the test wafer to the chuck,

6.3.3 Processing Contamination—This test method requires

and a means for attaching a thermometer or thermocouple to

oxidation processing of the test wafer to form the MOS the chuck (see Fig. 2). The enclosure must be completely

structure. In cases where the generation lifetime and generation

lighttight and constructed of metal for electrostatic shielding.

velocity are being measured to determine the quality of The enclosure must provide a means for connecting coaxial

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.