IEC 61280-2-3:2009

(Main)Fibre optic communication subsystem tets procedures - Part 2-3: Digital systems - Jitter and wander measurements

Fibre optic communication subsystem tets procedures - Part 2-3: Digital systems - Jitter and wander measurements

IEC 61280-2-3:2009 specifies methods for the measurement of the jitter and wander parameters associated with the transmission and handling of digital signals.

Procédures d'essai des sous-systèmes de télécommunications à fibres optiques - Partie 2-3: Systèmes numériques - Mesures des gigues et des dérapages

La CEI 61280-2-3:2009 spécifie des méthodes relatives à la mesure des paramètres de la gigue et du dérapage associés à la transmission et au traitement des signaux numériques.

General Information

- Status

- Published

- Publication Date

- 13-Jul-2009

- Technical Committee

- SC 86C - Fibre optic systems, sensing and active devices

- Drafting Committee

- WG 1 - TC 86/SC 86C/WG 1

- Current Stage

- PPUB - Publication issued

- Start Date

- 14-Jul-2009

- Completion Date

- 15-Aug-2009

Relations

- Effective Date

- 05-Sep-2023

Overview

IEC 61280-2-3:2009 is an international standard developed by the International Electrotechnical Commission (IEC). It specifies standardized test procedures for measuring jitter and wander in digital fibre optic communication subsystems. These measurements are essential for ensuring the reliable performance of fibre optic digital transmission systems, which are increasingly integral to modern telecommunications networks.

Jitter refers to the short-term variations in the timing of a digital signal, while wander involves long-term timing fluctuations. Both phenomena can impact data integrity, system synchronization, and overall network quality. This standard establishes repeatable methods to assess, characterize, and quantify these parameters under specified conditions.

Key Topics

IEC 61280-2-3:2009 covers a comprehensive range of parameters and measurement techniques related to the performance of digital fibre optic links:

Jitter Measurements

- Jitter tolerance (sinusoidal and stressed eye methods)

- Jitter transfer function

- Output jitter

- Systematic jitter

- Jitter separation

Wander Measurements

- Non-synchronized wander

- TDEV (Time Deviation) tolerance and transfer

- Synchronized wander

Related Definitions and Concepts

- Jitter amplitude and frequency

- Unit interval (UI)

- Bit error ratio (BER)

- Duty cycle distortion

- Data-dependent jitter and inter-symbol interference

- Timing jitter versus alignment jitter

Testing Procedures and Equipment

- General test configurations for the measurements

- Safety considerations and equipment requirements

Applications

Implementing IEC 61280-2-3:2009 brings practical value to fibre optic system designers, manufacturers, and operators:

Performance Verification

- Ensures digital optical subsystems meet required performance thresholds for jitter and wander, reducing the risk of transmission errors and data loss.

Quality Assurance

- Supports quality control processes in production and system integration by providing consistent, repeatable measurement methods.

Network Reliability

- Identifies sources of signal degradation, supporting preventative maintenance and rapid troubleshooting in deployed networks.

Equipment Design and Specification

- Informs the design and specification of receivers, transmitters, and regenerators to tolerate expected jitter and wander levels, improving interoperability across vendors.

Compliance and Certification

- Helps organizations demonstrate conformity with international standards, supporting global trade and regulatory approvals.

These applications are particularly critical for sectors such as telecommunications, data centers, broadcasting, and any environment relying on high-speed, high-integrity optical communication networks.

Related Standards

Ensuring comprehensive system performance and safety may require referencing additional standards alongside IEC 61280-2-3:2009, including:

- IEC 60825-1: Safety of laser products - Key for ensuring safe operation during subsystem testing.

- ITU-T Recommendation G.813: Timing characteristics of SDH equipment slave clocks.

- IEC 61931: Relevant for terminology and additional definitions in fibre optic components and systems.

- Other IEC 61280 Series Standards: For test procedures covering optical power, loss, and other subsystem characteristics.

For detailed implementation and updates, consult the IEC webstore or your national standards body to ensure the latest editions are referenced.

By following IEC 61280-2-3:2009, fibre optic communications professionals can achieve accurate jitter and wander measurements, supporting robust system performance and interoperable global networks.

Buy Documents

IEC 61280-2-3:2009 - Fibre optic communication subsystem tets procedures - Part 2-3: Digital systems - Jitter and wander measurements Released:7/14/2009

IEC 61280-2-3:2009 - Fibre optic communication subsystem tets procedures - Part 2-3: Digital systems - Jitter and wander measurements Released:7/14/2009

Get Certified

Connect with accredited certification bodies for this standard

ANCE

Mexican certification and testing association.

Intertek Slovenia

Intertek testing, inspection, and certification services in Slovenia.

LNE (Laboratoire National de Métrologie et d'Essais)

French national laboratory for metrology and testing.

Sponsored listings

Frequently Asked Questions

IEC 61280-2-3:2009 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Fibre optic communication subsystem tets procedures - Part 2-3: Digital systems - Jitter and wander measurements". This standard covers: IEC 61280-2-3:2009 specifies methods for the measurement of the jitter and wander parameters associated with the transmission and handling of digital signals.

IEC 61280-2-3:2009 specifies methods for the measurement of the jitter and wander parameters associated with the transmission and handling of digital signals.

IEC 61280-2-3:2009 is classified under the following ICS (International Classification for Standards) categories: 33.180.01 - Fibre optic systems in general. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 61280-2-3:2009 has the following relationships with other standards: It is inter standard links to IEC 61280-2-5:1998. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 61280-2-3:2009 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 61280-2-3 ®

Edition 1.0 2009-07

INTERNATIONAL

STANDARD

Fibre optic communication subsystem test procedures –

Part 2-3: Digital systems – Jitter and wander measurements

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form

or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from

either IEC or IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication,

please contact the address below or your local IEC member National Committee for further information.

IEC Central Office

3, rue de Varembé

CH-1211 Geneva 20

Switzerland

Email: inmail@iec.ch

Web: www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

ƒ Catalogue of IEC publications: www.iec.ch/searchpub

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,…).

It also gives information on projects, withdrawn and replaced publications.

ƒ IEC Just Published: www.iec.ch/online_news/justpub

Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available

on-line and also by email.

ƒ Electropedia: www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions

in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical

Vocabulary online.

ƒ Customer Service Centre: www.iec.ch/webstore/custserv

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service

Centre FAQ or contact us:

Email: csc@iec.ch

Tel.: +41 22 919 02 11

Fax: +41 22 919 03 00

IEC 61280-2-3 ®

Edition 1.0 2009-07

INTERNATIONAL

STANDARD

Fibre optic communication subsystem test procedures –

Part 2-3: Digital systems – Jitter and wander measurements

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

PRICE CODE

W

ICS 33.180.01 ISBN 978-2-88910-475-8

– 2 – 61280-2-3 © IEC:2009(E)

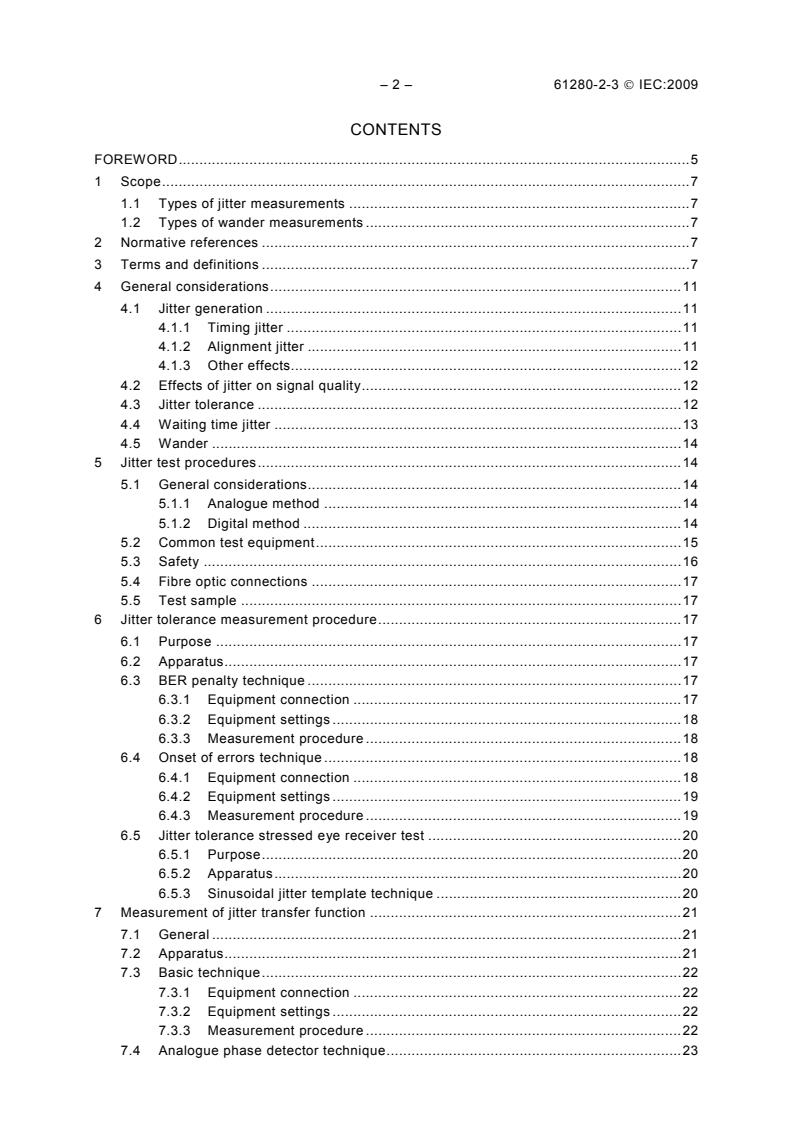

CONTENTS

FOREWORD.5

1 Scope.7

1.1 Types of jitter measurements .7

1.2 Types of wander measurements .7

2 Normative references .7

3 Terms and definitions .7

4 General considerations.11

4.1 Jitter generation .11

4.1.1 Timing jitter .11

4.1.2 Alignment jitter .11

4.1.3 Other effects.12

4.2 Effects of jitter on signal quality.12

4.3 Jitter tolerance .12

4.4 Waiting time jitter .13

4.5 Wander .14

5 Jitter test procedures.14

5.1 General considerations.14

5.1.1 Analogue method .14

5.1.2 Digital method .14

5.2 Common test equipment.15

5.3 Safety .16

5.4 Fibre optic connections .17

5.5 Test sample .17

6 Jitter tolerance measurement procedure.17

6.1 Purpose .17

6.2 Apparatus.17

6.3 BER penalty technique .17

6.3.1 Equipment connection .17

6.3.2 Equipment settings .18

6.3.3 Measurement procedure .18

6.4 Onset of errors technique .18

6.4.1 Equipment connection .18

6.4.2 Equipment settings .19

6.4.3 Measurement procedure .19

6.5 Jitter tolerance stressed eye receiver test .20

6.5.1 Purpose.20

6.5.2 Apparatus.20

6.5.3 Sinusoidal jitter template technique .20

7 Measurement of jitter transfer function .21

7.1 General .21

7.2 Apparatus.21

7.3 Basic technique.22

7.3.1 Equipment connection .22

7.3.2 Equipment settings .22

7.3.3 Measurement procedure .22

7.4 Analogue phase detector technique.23

61280-2-3 © IEC:2009(E) – 3 –

7.4.1 Equipment connections.23

7.4.2 Equipment settings .23

7.4.3 Measurement procedure .24

7.4.4 Measurement calculations .24

8 Measurement of output jitter .24

8.1 General .24

8.2 Equipment connection .24

8.2.1 Equipment settings .24

8.2.2 Measurement procedure .24

8.2.3 Controlled data.25

9 Measurement of systematic jitter .25

9.1 Apparatus.25

9.2 Basic technique.25

9.2.1 Equipment connection .25

9.2.2 Equipment settings .26

9.2.3 Measurement procedure .26

10 BERT scan technique .27

10.1 Apparatus.29

10.2 Basic technique.29

10.2.1 Equipment connection .29

10.2.2 Equipment settings .29

10.2.3 Measurement process .29

11 Jitter separation technique .30

11.1 Apparatus.31

11.2 Equipment connections .31

11.3 Equipment settings.31

11.4 Measurement procedure.32

11.4.1 Sampling oscilloscope: .32

11.4.2 Real-time oscilloscope.32

12 Measurement of wander .33

12.1 Apparatus.33

12.2 Basic technique.33

12.2.1 Equipment connection .33

12.2.2 Equipment settings .34

12.2.3 Measurement procedure .35

13 Measurement of wander TDEV tolerance.35

13.1 Intent.35

13.2 Apparatus.35

13.3 Basic technique.35

13.4 Equipment connection .35

13.4.1 Wander TDEV tolerance measurement for the test signal of EUT .35

13.4.2 Wander TDEV tolerance measurement for timing reference signal of

EUT.36

13.5 Equipment settings.36

13.6 Measurement procedure.37

14 Measurement of wander TDEV transfer .37

14.1 Apparatus.37

14.2 Equipment connection .37

– 4 – 61280-2-3 © IEC:2009(E)

14.2.1 Wander TDEV transfer measurement for the test signal of EUT .37

14.2.2 Wander TDEV transfer measurement for timing reference signal of

EUT.37

14.3 Equipment settings.38

14.4 Measurement procedure.38

15 Test results .38

15.1 Mandatory information.38

15.2 Available information.39

Bibliography.40

Figure 1 – Jitter generation .11

Figure 2 – Example of jitter tolerance.13

Figure 3 – Jitter and wander generator .15

Figure 4 – Jitter and wander measurement .16

Figure 5 – Jitter stress generator .16

Figure 6 – Jitter tolerance measurement configuration: bit error ratio (BER) penalty

technique.18

Figure 7 – Jitter tolerance measurement configuration: Onset of errors technique .19

Figure 8 – Equipment configuration for stressed eye tolerance test.20

Figure 9 – Measurement of jitter transfer function: basic technique.22

Figure 10 – Measurement of Jitter transfer: analogue phase detector technique .23

Figure 11 – Output jitter measurement .25

Figure 12 – Systematic jitter measurement configuration: basic technique .26

Figure 13 – Measurement of the pattern-dependent phase sequence xi .27

Figure 14 – BERT scan bathtub curves (solid line for low jitter, dashed line for high

jitter).28

Figure 15 – Equipment setup for the BERT scan.29

Figure 16 – Dual Dirac jitter model.31

Figure 17 – Equipment setup for jitter separation measurement.31

Figure 18 – Measurement of time interval error.32

Figure 19 – Synchronized wander measurement configuration.34

Figure 20 – Non-synchronized wander measurement configuration .34

Figure 21 – Wander TDEV tolerance measurement configuration for the test signal of

EUT .36

Figure 22 – Wander TDEV tolerance measurement configuration for the timing signal

of EUT .36

Figure 23 – Wander TDEV transfer measurement configuration for the test signal of

EUT .37

Figure 24 – Wander TDEV transfer measurement configuration for the timing signal of

EUT .38

61280-2-3 © IEC:2009(E) – 5 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

FIBRE OPTIC COMMUNICATION SUBSYSTEM

TEST PROCEDURES –

Part 2-3: Digital systems –

Jitter and wander measurements

FOREWORD

1) The IEC (International Electrotechnical Commission) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of the IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, the IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. The IEC collaborates

closely with the International Organization for Standardization (ISO) in accordance with conditions determined

by agreement between the two organizations.

2) The formal decisions or agreements of the IEC on technical matters express, as nearly as possible, an

international consensus of opinion on the relevant subjects since each technical committee has representation

from all interested National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international unification, IEC National Committees undertake to apply IEC International

Standards transparently to the maximum extent possible in their national and regional standards. Any

divergence between the IEC Standard and the corresponding national or regional standard shall be clearly

indicated in the latter.

5) The IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any

equipment declared to be in conformity with one of its standards.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 61280-2-3 has been prepared by subcommittee 86C: Fibre optic

systems and active devices, of IEC technical committee 86: Fibre optics.

The text of this standard is based on the following documents:

FDIS Report on voting

86C/885/FDIS 86C/905/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

A list of all parts of the IEC 61280-2 series, published under the general title Fibre optic

communication subsystem test procedures – Digital systems, can be found on the IEC

website.

– 6 – 61280-2-3 © IEC:2009(E)

The committee has decided that the contents of this publication will remain unchanged until

the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in

the data related to the specific publication. At this date, the publication will be

• reconfirmed;

• withdrawn;

• replaced by a revised edition, or

• amended.

A bilingual version may be published at a later date.

61280-2-3 © IEC:2009(E) – 7 –

FIBRE OPTIC COMMUNICATION SUBSYSTEM

TEST PROCEDURES –

Part 2-3: Digital systems –

Jitter and wander measurements

1 Scope

This part of IEC 61280 specifies methods for the measurement of the jitter and wander

parameters associated with the transmission and handling of digital signals.

1.1 Types of jitter measurements

This standard covers the measurement of the following types of jitter parameters:

a) jitter tolerance

1) sinusoidal method

2) stressed eye method

b) jitter transfer function

c) output jitter

d) systematic jitter

e) jitter separation

1.2 Types of wander measurements

This standard covers the measurement of the following types of wander parameters:

a) non-synchronized wander

b) TDEV tolerance

c) TDEV transfer

d) synchronized wander

2 Normative references

The following referenced documents are indispensable for the application of this document.

For dated references, only the edition cited applies. For undated references, the latest edition

of the referenced document (including any amendments) applies.

IEC 60825-1, Safety of laser products – Part 1: Equipment classification and requirements

ITU-T Recommendation G.813, Timing characteristics of SDH equipment slave clocks (SEC)

3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

NOTE See also IEC 61931.

– 8 – 61280-2-3 © IEC:2009(E)

3.1

jitter

the short-term, non-cumulative, variation in time of the significant instances of a digital signal

from their ideal position in time. Short-term variations in this context are jitter components

with a repetition frequency equal to or exceeding 10 Hz

3.2

jitter amplitude

the deviation of the significant instance of a digital signal from its ideal position in time

NOTE For the purposes of this standard the jitter amplitude is expressed in terms of the unit interval (UI). It is

recognized that jitter amplitude may also be expressed in units of time.

3.3

unit interval (UI)

the shortest interval between two equivalent instances in ideal positions in time. In practice

this is equivalent to the ideal timing period of the digital signal

3.4

jitter frequency

the rate of variation in time of the significant instances of a digital signal relative to their ideal

position in time. Jitter frequency is expressed in Hertz (Hz)

3.5

jitter bandwidth

the jitter frequency at which the jitter amplitude has decreased by 3dB relative to its maximum

value

3.6

alignment jitter

jitter created when the timing of a data signal is recovered from the signal itself

3.7

timing jitter

jitter present on a timing source

3.8

systematic jitter

jitter components which are not random and have a predictable rate of occurrence.

Systematic jitter in a digital signal results from regularly recurring features in the digital signal,

such as frame alignment data, and justification control data. This is sometimes referred to as

deterministic jitter and is composed of periodic uncorrelated jitter and data dependent jitter

3.9

periodic uncorrelated jitter

a form of systematic jitter that occurs at a regular rate, but is uncorrelated to the data when

the data pattern repeats. Periodic uncorrelated jitter will be the same independent of which

edge in a pattern is observed over time. Sources of periodic uncorrelated jitter include

switching power supplies phase modulating reference clocks or any form of periodic phase

modulation of clocks that control data rates

3.10

inter-symbol interference jitter

caused by bandwidth limitations in transmission channels. If the channel bandwidth is low,

signal transitions may not reach full amplitude before transitioning to a different logic state.

Starting at a level closer to the midpoint between logic states, the time at which the signal

edge then crosses a specific amplitude threshold can be early compared to consecutive

identical digits which have reached full amplitude and then switch to the other logic state

61280-2-3 © IEC:2009(E) – 9 –

3.11

duty cycle distortion

occurs when the duration of a logic 1 (0-1-0) is different from the duration of a logic 0 (1-0-1).

For example, if the logic 1 has a longer duration, rising edges will occur early relative to

falling edges, compared to their ideal locations in time

3.12

data dependent jitter

represents jitter that is correlated to specific bits in a repeating data pattern. That is, when a

data pattern repeats, the jitter on any given signal edge will manifest itself in the same way for

any repetition of the pattern. It is due to either duty cycle distortion and/or inter-symbol

interference

3.13

waiting time jitter

applies to plesiochronous multiplexing and is defined as the jitter caused by the varying delay

between the demand for justification and its execution

3.14

jitter tolerance

maximum jitter amplitude that a digital receiver can accept for a given penalty or alternatively

without the addition of a given number of errors to the digital signal. The maximum jitter

amplitude tolerated is generally dependent on the frequency of the jitter

3.15

jitter generation

process of adding jitter impairment to a data signal

3.16

input jitter

magnitude of the jitter occurring at a hierarchical interface or the input port of equipment or a

device

3.17

output jitter

magnitude of the jitter occurring at a hierarchical interface or the output port of equipment or a

device

3.18

jitter transfer

amount of jitter transferred from the input to the output of an equipment or device. It is usually

expressed as a ratio (in dB) of the output jitter to the input jitter

3.19

total jitter

the summation (or convolution) of deterministic and random jitter. Total jitter is expressed as

a peak value

3.20

jitter bathtub curve

display of bit-error-ratio as a function of the time location of the BERT error detector sampling

point. The resulting curve is then a display of the probability that a data edge will be

misplaced at or beyond a specific location (closer to the centre of a bit) within a unit interval

3.21

wander

long-term, non-cumulative, variation in time of the significant instances of a digital signal from

their ideal position in time. Long-term variations in this context are jitter components with a

repetition frequency less than 10 Hz

– 10 – 61280-2-3 © IEC:2009(E)

NOTE For the purpose of this document, the wander amplitude is expressed in units of time (s). It is recognised

that wander amplitude may also be expressed in terms of unit interval (UI).

3.22

time interval error

TIE

difference between the measure of a time interval as provided by a clock and the measure of

that same time interval as provided by a reference clock. Mathematically, the time interval

error function TIE (t;τ) can be expressed as:

TIE(t;τ ) =[]T()t + τ −T(t) −[Tref (t + τ ) −Tref (t)] = x(t + τ ) − x(t) (1)

where τ is the time interval, usually called observation interval

3.23

maximum time interval error

MTIE

maximum peak-to-peak delay variation of a given timing signal with respect to an ideal timing

signal within an observation time (τ = nτ ) for all observation times of that length within the

measurement period (T). It is estimated using the following formula:

⎤

⎡

⎥

MTIE(nτ ) ≅ ⎢ − n = 1,2KN − 1 (2)

max maxx minx

i i

⎥

⎢

1≤k≤N −n⎣k≤i≤k+n k≤i≤k+n

⎥

⎦

3.24

time deviation

TDEV or σx

measure of the expected time variation of a signal as a function of integration time. TDEV can

also provide information about the spectral content of the phase (or time) noise of a signal.

TDEV is in units of time. Based on the sequence of time error samples, TDEV is estimated

using the following calculation:

N−3n+1 n+ j−1

⎡ ⎤

1 ⎛ N⎞

⎢ ⎥

TDEV()nτ ≅ ( − 2 + ) n = 1,2K,int part⎜ ⎟

(3)

∑ ∑

x x x

2 i+2n i+n i

⎢ ⎥ 3

6n (N − 3n + 1) ⎝ ⎠

j=1 i=j

⎣ ⎦

where

x denotes time error samples;

i

N denotes the total number of samples;

τ denotes the time error-sampling interval;

τ denotes the integration time, the independent variable of TDEV;

n denotes the number of sampling intervals within the integration time t.

3.25

bit error ratio

BER

number of bits received in error as a ratio of the total number of bits received

3.26

errored second

time of 1 s duration that contains one or more digital errors in a data stream

61280-2-3 © IEC:2009(E) – 11 –

4 General considerations

4.1 Jitter generation

Jitter in a digital signal is generated by three basic processes which are briefly described

below. The mathematical analysis of the jitter processes is complex and not within the scope

of this standard. A comprehensive analysis and early mathematical treatise of the jitter

processes is provided by [1] .

4.1.1 Timing jitter

Jitter impairment of the original data timing clock. Even the most stable timing sources

contain a certain amount of jitter, or unintended phase modulation or phase noise. In primary

timing generators this impairment is exceedingly small, but is increased when such timing

signals are distributed in a system. The effect of noise on the timing signal in a digital system

is demonstrated in an exaggerated degree in Figure 1.

Ideal timing

Noise on timing signal

Detection threshold

Timing signal

p- p Jitter amplitude

IEC 1164/09

Figure 1 – Jitter generation

4.1.2 Alignment jitter

When a digital pattern is presented to a timing recovery circuit, the continuous variation of the

digital pattern results in the creation of jitter in the recovered clock signal relative to the

incoming data (alignment jitter). This effect, first analyzed and described in detail by [2] is the

major cause of jitter generation. It means that the jitter components of the recovered clock

signal are added to the data when they are retimed. The jitter bandwidth created by this

process is the same as the analogue bandwidth of the clock recovery circuit used.

When the process is repeated at a similar equipment, the resultant clock signal shows

increased jitter due to the addition of timing and alignment jitter. Thus, jitter is added to the

data signal, and amplified at the next timing recovery operation. A repetition of this process,

such as occurs in transmission links with many repeaters, or chains of add-drop multiplexers,

can build up substantial jitter amplitudes; but as long as the bandwidth of the timing recovery

process is the same or greater than the jitter bandwidth of the signal, the jitter will always be

accommodated. An analysis of the accumulation of jitter in successive timing recovery

operations was first published by [3]. The jitter buildup can be represented by an equation of

the form:

—————————

Figures in square brackets refer to the Bibliography.

– 12 – 61280-2-3 © IEC:2009(E)

k

n

⎛ 1 ⎞

θn = θ (jω)⎜ ⎟ (4)

∑ 0

⎜ ⎟

1+ j ω / B

⎝ ⎠

k=1

The above equation yields a jitter power density spectrum which can be expressed in the

form:

⎡ n ⎤

sin ω

⎢ ⎥

2 2B

φ ≈ n φ for ω<

⎢ ⎥

n 0

n

⎢ ⎥

ω

⎢ ⎥

2B

⎣ ⎦

where

θ denotes the jitter amplitude after n timing recovery processes

n

θ denotes the jitter amplitude introduced at each individual timing recovery process

n denotes the number of tandem timing recovery processes

ω denotes the angular frequency (2πf) of the jitter component

B denotes the half angular bandwidth of the timing recovery circuit

Ф denotes the jitter power density after n timing recovery processes

n

Ф denotes the jitter power density introduced at each individual timing recovery process

It should be noted that for low values of frequency the power density and hence amplitude of

the jitter increases linearly with the number of tandem timing recovery processes.

In point-to-point communications systems, where transmitter timing is not derived from

incoming data, alignment jitter and jitter build-up is not a significant problem.

4.1.3 Other effects

In the course of the transmission of a digital signal, further impairments such as added noise

and dispersion effects provide additional jitter components when timing is recovered from the

signal. Such effects are more severe when analogue amplification is used rather than digital

regeneration in order to increase the length of a digital link.

4.2 Effects of jitter on signal quality

Jitter has no effect on the transmission of data as long as the equipment can accommodate

the jitter amplitude and rate of deviation (see 4.3). When jitter is large enough or fast enough

such that the receiver decision point is made near or beyond a data edge, a mistake can be

made and BER degraded. Jitter, depending on its amplitude and frequency, can also have

serious effects on analogue services such as music and television which have been

transmitted over digital links. The effect of jitter is to introduce unwanted frequency and phase

modulation products which are audible in music and visible on television pictures.

4.3 Jitter tolerance

In telecommunications systems, jitter tolerance requirements are typically specified in terms

of jitter templates, which cover a specified sinusoidal amplitude/frequency region. Jitter

templates represent the minimum amount of jitter the equipment shall be able to accept

without producing the specified degradation of error performance. A typical relationship

between actual jitter tolerance and its associated tolerance template is illustrated in Figure 2.

The jitter amplitudes that equipment actually tolerates at a given frequency are defined as all

amplitudes up to, but not including, that which causes the designated degradation of error

performance. The designated degradation of error performance may be expressed in terms of

either bit-error-ratio (BER) penalty or the onset of errors criteria. The existence of these two

61280-2-3 © IEC:2009(E) – 13 –

criteria arises because the input jitter tolerance of digital equipment is primarily determined by

the following three factors:

a) ability of the input clock recovery circuit to accurately recover the timing from a jittered

data signal, including the presence of other degradations such as pulse distortion,

crosstalk, noise, and other impairments;

b) ability of the input circuit buffer, for example an elastic store, to accommodate the jitter

amplitude;

c) ability of other components to accommodate dynamically varying input data rates such

as pulse justification capacity and synchronizer and de-synchronizer buffer size in an

asynchronous digital multiplex.

Actual jitter tolerance

Operating jitter margin

Template specification

Acceptable region

dB/decade

Unacceptable region

IEC 1165/09

Figure 2 – Example of jitter tolerance

In data communications systems, jitter tolerance is often determined with signal impairments

that are more complex than simple sinusoidal jitter. The general concept is to verify that the

receiver is capable of achieving the desired BER when presented with the allowable signal it

will encounter in a real system. Thus the jitter tolerance test signal will include impairments

that are allowed for both the transmitter and the channel. For example, a real transmitter may

have periodic jitter, random jitter, and duty cycle distortion. As the signal traverses the

channel, it may be further degraded through a bandwidth limited channel, thus adding inter-

symbol interference jitter. As the receiver shall be able to tolerate such a signal in a real

system, the signal used to verify receiver tolerance shall include all of these impairments.

This method of testing is sometimes referred to as “stressed eye” testing, indicating that the

eye diagram of the signal presented to a receiver has been intentionally degraded or

stressed.

4.4 Waiting time jitter

When asynchronous (plesiochronous) signals are multiplexed, a justification technique (also

known as pulse stuffing) is used which involves the comparison of the phase of the incoming

digital signal with the multiplexer’s tributary timing. When a preset difference is detected a

control signal is transmitted, via the overhead in the multiplex frame structure, to the

demultiplexer. In order to ensure the integrity of the control signal in the presence of errors, it

is repeated 3 or 5 times. At the demultiplexer a majority decision is taken to recognize the

– 14 – 61280-2-3 © IEC:2009(E)

control signal. This delay introduces an uncertainty and varying delay in the time between the

demand for justification and its execution at the demultiplexer, and expresses itself as waiting

time jitter.

4.5 Wander

Wander is essentially caused by periodic variations in the delay of a transmission path and

slow variations in the frequency of data clocks. The boundary between jitter and wander at a

frequency of 10 Hz is somewhat artificial since most significant wander effects occur at

repetition rates of hours, days, months and seasons. In general wander is caused by

temperature changes which affect the delays of the transmission medium or equipment. For

terrestrial transmission, wander components are normally limited to a few tens of

nanoseconds.

In synchronous networks the accommodation of wander is an essential feature since a single

bit slip will initiate a resynchronization process with consequent loss of data. If this occurs at

a high level demultiplexer, all lower levels will also resynchronize which will exacerbate the

loss of data. Wander is normally accommodated by increasing the size of the elastic store

used to accommodate jitter.

A special case is the wander effect that occurs in communications via geostationary satellites.

While the lateral position of such satellites is relatively stable, their mean height of some

35 000 km above the earth’s surface has a diurnal variation which may be up to approximately

±1 000 km. This results in delay variations per hop of approximately 26 ms. At a data rate of

150 Mbit/s this represents a wander rate of some 45 bits/s and requires an elastic store with a

capacity of at least 3,9 Mbits to accommodate it in a synchronous network.

5 Jitter test procedures

5.1 General considerations

In order to measure jitter, analogue and digital methods may be used. Both methods rely on

the phase comparison between a recovered timing signal representing the signal to be

measured, or in some cases the signal itself, and a stable clock signal whose frequency

represents the ideal signal. In telecommunications applications, this ideal signal is derived

from the long-term average frequency of the derived timing signal. In order to obtain

meaningful results, the jitter bandwidth of the derived clock shall be significantly less than 10

Hz. In data communications applications, the reference clock is also typically derived from the

signal, but the jitter bandwidth of the derived signal will often be similar to the clock recovery

bandwidth of the receiver for which a transmitter under test will be paired with. In system use,

jitter that is within the loop bandwidth of the receiver is accommodated by the receiver and of

lower concern. In test, jitter that is common to both the reference signal and the signal to be

measured may intentionally not be observed. This facilitates the ability to observe jitter

outside the jitter bandwidth.

5.1.1 Analogue method

The analogue method uses the analogue output from a phase comparison between the

recovered clock and the stable clock which provides a pulse width modulated signal

presentation of the jitter components in terms of amplitude and frequency. This is

subsequently converted into an analogue output which is used to process the results. Like all

analogue measuring techniques, this method requires careful calibration and is highly

dependant on the performance characteristics, including stability, of the phase comparator.

5.1.2 Digital method

5.1.2.1 Derived clock versus narrow jitter bandwidth clock

The digital method uses a very high speed sampling clock to measure the time difference

between the significant instances of the recovered and the derived stable clock signals. The

61280-2-3 © IEC:2009(E) – 15 –

results are then obtained by digital processing of the measured time intervals. This method is

capable of providing essentially accurate results and is naturally suited for measuring

equipment using digital techniques. The main difficulty with this method is to provide a timing

signal with a sufficiently high rate to obtain sufficient resolution.

5.1.2.2 Data edge versus reference or extracted clock

With a reference clock representing the ideal position of data edges, a population of edge

locations relative to ideal is collected. This population is then post-processed to determine the

jitter performance. Deterministic and random jitter contributions can be isolated. Further

processing allows the estimate of the aggregate jitter (total jitter) to extremely low

probabilities without the long measurement time required to make a direct measurement to

low probabilities. This technique is capable of making very accurate measurements and

estimations. The main difficu

...

IEC 61280-2-3 ®

Edition 1.0 2009-07

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

Fibre optic communication subsystem test procedures –

Part 2-3: Digital systems – Jitter and wander measurements

Procédures d'essai des sous-systèmes de télécommunications à fibres

optiques –

Partie 2-3: Systèmes numériques – Mesures des gigues et des dérapages

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by

any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or

IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication,

please contact the address below or your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite

ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie

et les microfilms, sans l'accord écrit de la CEI ou du Comité national de la CEI du pays du demandeur.

Si vous avez des questions sur le copyright de la CEI ou si vous désirez obtenir des droits supplémentaires sur cette

publication, utilisez les coordonnées ci-après ou contactez le Comité national de la CEI de votre pays de résidence.

IEC Central Office

3, rue de Varembé

CH-1211 Geneva 20

Switzerland

Email: inmail@iec.ch

Web: www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

ƒ Catalogue of IEC publications: www.iec.ch/searchpub

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,…).

It also gives information on projects, withdrawn and replaced publications.

ƒ IEC Just Published: www.iec.ch/online_news/justpub

Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available

on-line and also by email.

ƒ Electropedia: www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions

in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical

Vocabulary online.

ƒ Customer Service Centre: www.iec.ch/webstore/custserv

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service

Centre FAQ or contact us:

Email: csc@iec.ch

Tel.: +41 22 919 02 11

Fax: +41 22 919 03 00

A propos de la CEI

La Commission Electrotechnique Internationale (CEI) est la première organisation mondiale qui élabore et publie des

normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications CEI

Le contenu technique des publications de la CEI est constamment revu. Veuillez vous assurer que vous possédez

l’édition la plus récente, un corrigendum ou amendement peut avoir été publié.

ƒ Catalogue des publications de la CEI: www.iec.ch/searchpub/cur_fut-f.htm

Le Catalogue en-ligne de la CEI vous permet d’effectuer des recherches en utilisant différents critères (numéro de référence,

texte, comité d’études,…). Il donne aussi des informations sur les projets et les publications retirées ou remplacées.

ƒ Just Published CEI: www.iec.ch/online_news/justpub

Restez informé sur les nouvelles publications de la CEI. Just Published détaille deux fois par mois les nouvelles

publications parues. Disponible en-ligne et aussi par email.

ƒ Electropedia: www.electropedia.org

Le premier dictionnaire en ligne au monde de termes électroniques et électriques. Il contient plus de 20 000 termes et

définitions en anglais et en français, ainsi que les termes équivalents dans les langues additionnelles. Egalement appelé

Vocabulaire Electrotechnique International en ligne.

ƒ Service Clients: www.iec.ch/webstore/custserv/custserv_entry-f.htm

Si vous désirez nous donner des commentaires sur cette publication ou si vous avez des questions, visitez le FAQ du

Service clients ou contactez-nous:

Email: csc@iec.ch

Tél.: +41 22 919 02 11

Fax: +41 22 919 03 00

IEC 61280-2-3 ®

Edition 1.0 2009-07

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

colour

inside

Fibre optic communication subsystem test procedures –

Part 2-3: Digital systems – Jitter and wander measurements

Procédures d'essai des sous-systèmes de télécommunications à fibres

optiques –

Partie 2-3: Systèmes numériques – Mesures des gigues et des dérapages

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION

ELECTROTECHNIQUE

PRICE CODE

INTERNATIONALE

W

CODE PRIX

ICS 33.180.01 ISBN 978-2-88910-476-5

– 2 – 61280-2-3 © IEC:2009

CONTENTS

FOREWORD.5

1 Scope.7

1.1 Types of jitter measurements .7

1.2 Types of wander measurements .7

2 Normative references .7

3 Terms and definitions .7

4 General considerations.11

4.1 Jitter generation .11

4.1.1 Timing jitter .11

4.1.2 Alignment jitter .11

4.1.3 Other effects.12

4.2 Effects of jitter on signal quality.12

4.3 Jitter tolerance .12

4.4 Waiting time jitter .13

4.5 Wander .14

5 Jitter test procedures.14

5.1 General considerations.14

5.1.1 Analogue method .14

5.1.2 Digital method .14

5.2 Common test equipment.15

5.3 Safety .16

5.4 Fibre optic connections .17

5.5 Test sample .17

6 Jitter tolerance measurement procedure.17

6.1 Purpose .17

6.2 Apparatus.17

6.3 BER penalty technique .17

6.3.1 Equipment connection .17

6.3.2 Equipment settings .18

6.3.3 Measurement procedure .18

6.4 Onset of errors technique .18

6.4.1 Equipment connection .18

6.4.2 Equipment settings .19

6.4.3 Measurement procedure .19

6.5 Jitter tolerance stressed eye receiver test .20

6.5.1 Purpose.20

6.5.2 Apparatus.20

6.5.3 Sinusoidal jitter template technique .20

7 Measurement of jitter transfer function .21

7.1 General .21

7.2 Apparatus.21

7.3 Basic technique.22

7.3.1 Equipment connection .22

7.3.2 Equipment settings .22

7.3.3 Measurement procedure .22

7.4 Analogue phase detector technique.23

61280-2-3 © IEC:2009 – 3 –

7.4.1 Equipment connections.23

7.4.2 Equipment settings .23

7.4.3 Measurement procedure .24

7.4.4 Measurement calculations .24

8 Measurement of output jitter .24

8.1 General .24

8.2 Equipment connection .24

8.2.1 Equipment settings .24

8.2.2 Measurement procedure .24

8.2.3 Controlled data.25

9 Measurement of systematic jitter .25

9.1 Apparatus.25

9.2 Basic technique.25

9.2.1 Equipment connection .25

9.2.2 Equipment settings .26

9.2.3 Measurement procedure .26

10 BERT scan technique .27

10.1 Apparatus.29

10.2 Basic technique.29

10.2.1 Equipment connection .29

10.2.2 Equipment settings .29

10.2.3 Measurement process .29

11 Jitter separation technique .30

11.1 Apparatus.31

11.2 Equipment connections .31

11.3 Equipment settings.31

11.4 Measurement procedure.32

11.4.1 Sampling oscilloscope: .32

11.4.2 Real-time oscilloscope.32

12 Measurement of wander .33

12.1 Apparatus.33

12.2 Basic technique.33

12.2.1 Equipment connection .33

12.2.2 Equipment settings .34

12.2.3 Measurement procedure .35

13 Measurement of wander TDEV tolerance.35

13.1 Intent.35

13.2 Apparatus.35

13.3 Basic technique.35

13.4 Equipment connection .35

13.4.1 Wander TDEV tolerance measurement for the test signal of EUT .35

13.4.2 Wander TDEV tolerance measurement for timing reference signal of

EUT.36

13.5 Equipment settings.36

13.6 Measurement procedure.37

14 Measurement of wander TDEV transfer .37

14.1 Apparatus.37

14.2 Equipment connection .37

– 4 – 61280-2-3 © IEC:2009

14.2.1 Wander TDEV transfer measurement for the test signal of EUT .37

14.2.2 Wander TDEV transfer measurement for timing reference signal of

EUT.37

14.3 Equipment settings.38

14.4 Measurement procedure.38

15 Test results .38

15.1 Mandatory information.38

15.2 Available information.39

Bibliography.40

Figure 1 – Jitter generation .11

Figure 2 – Example of jitter tolerance.13

Figure 3 – Jitter and wander generator .15

Figure 4 – Jitter and wander measurement .16

Figure 5 – Jitter stress generator .16

Figure 6 – Jitter tolerance measurement configuration: bit error ratio (BER) penalty

technique.18

Figure 7 – Jitter tolerance measurement configuration: Onset of errors technique .19

Figure 8 – Equipment configuration for stressed eye tolerance test.20

Figure 9 – Measurement of jitter transfer function: basic technique.22

Figure 10 – Measurement of Jitter transfer: analogue phase detector technique .23

Figure 11 – Output jitter measurement .25

Figure 12 – Systematic jitter measurement configuration: basic technique .26

Figure 13 – Measurement of the pattern-dependent phase sequence xi .27

Figure 14 – BERT scan bathtub curves (solid line for low jitter, dashed line for high

jitter).28

Figure 15 – Equipment setup for the BERT scan.29

Figure 16 – Dual Dirac jitter model.31

Figure 17 – Equipment setup for jitter separation measurement.31

Figure 18 – Measurement of time interval error.32

Figure 19 – Synchronized wander measurement configuration.34

Figure 20 – Non-synchronized wander measurement configuration .34

Figure 21 – Wander TDEV tolerance measurement configuration for the test signal of

EUT .36

Figure 22 – Wander TDEV tolerance measurement configuration for the timing signal

of EUT .36

Figure 23 – Wander TDEV transfer measurement configuration for the test signal of

EUT .37

Figure 24 – Wander TDEV transfer measurement configuration for the timing signal of

EUT .38

61280-2-3 © IEC:2009 – 5 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

FIBRE OPTIC COMMUNICATION SUBSYSTEM

TEST PROCEDURES –

Part 2-3: Digital systems –

Jitter and wander measurements

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 61280-2-3 has been prepared by subcommittee 86C: Fibre optic

systems and active devices, of IEC technical committee 86: Fibre optics.

This bilingual version, published in 2010-02, corresponds to the English version.

The text of this standard is based on the following documents:

FDIS Report on voting

86C/885/FDIS 86C/905/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

The French version of this standard has not been voted upon.

– 6 – 61280-2-3 © IEC:2009

A list of all parts of the IEC 61280-2 series, published under the general title Fibre optic

communication subsystem test procedures – Digital systems, can be found on the IEC

website.

The committee has decided that the contents of this publication will remain unchanged until

the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in

the data related to the specific publication. At this date, the publication will be

• reconfirmed;

• withdrawn;

• replaced by a revised edition, or

• amended.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates

that it contains colours which are considered to be useful for the correct

understanding of its contents. Users should therefore print this document using a

colour printer.

61280-2-3 © IEC:2009 – 7 –

FIBRE OPTIC COMMUNICATION SUBSYSTEM

TEST PROCEDURES –

Part 2-3: Digital systems –

Jitter and wander measurements

1 Scope

This part of IEC 61280 specifies methods for the measurement of the jitter and wander

parameters associated with the transmission and handling of digital signals.

1.1 Types of jitter measurements

This standard covers the measurement of the following types of jitter parameters:

a) jitter tolerance

1) sinusoidal method

2) stressed eye method

b) jitter transfer function

c) output jitter

d) systematic jitter

e) jitter separation

1.2 Types of wander measurements

This standard covers the measurement of the following types of wander parameters:

a) non-synchronized wander

b) TDEV tolerance

c) TDEV transfer

d) synchronized wander

2 Normative references

The following referenced documents are indispensable for the application of this document.

For dated references, only the edition cited applies. For undated references, the latest edition

of the referenced document (including any amendments) applies.

IEC 60825-1, Safety of laser products – Part 1: Equipment classification and requirements

ITU-T Recommendation G.813, Timing characteristics of SDH equipment slave clocks (SEC)

3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

NOTE See also IEC 61931.

– 8 – 61280-2-3 © IEC:2009

3.1

jitter

the short-term, non-cumulative, variation in time of the significant instances of a digital signal

from their ideal position in time. Short-term variations in this context are jitter components

with a repetition frequency equal to or exceeding 10 Hz

3.2

jitter amplitude

the deviation of the significant instance of a digital signal from its ideal position in time

NOTE For the purposes of this standard the jitter amplitude is expressed in terms of the unit interval (UI). It is

recognized that jitter amplitude may also be expressed in units of time.

3.3

unit interval

UI

the shortest interval between two equivalent instances in ideal positions in time. In practice

this is equivalent to the ideal timing period of the digital signal

3.4

jitter frequency

the rate of variation in time of the significant instances of a digital signal relative to their ideal

position in time. Jitter frequency is expressed in Hertz (Hz)

3.5

jitter bandwidth

the jitter frequency at which the jitter amplitude has decreased by 3dB relative to its maximum

value

3.6

alignment jitter

jitter created when the timing of a data signal is recovered from the signal itself

3.7

timing jitter

jitter present on a timing source

3.8

systematic jitter

jitter components which are not random and have a predictable rate of occurrence.

Systematic jitter in a digital signal results from regularly recurring features in the digital signal,

such as frame alignment data, and justification control data. This is sometimes referred to as

deterministic jitter and is composed of periodic uncorrelated jitter and data dependent jitter

3.9

periodic uncorrelated jitter

a form of systematic jitter that occurs at a regular rate, but is uncorrelated to the data when

the data pattern repeats. Periodic uncorrelated jitter will be the same independent of which

edge in a pattern is observed over time. Sources of periodic uncorrelated jitter include

switching power supplies phase modulating reference clocks or any form of periodic phase

modulation of clocks that control data rates

3.10

inter-symbol interference jitter

caused by bandwidth limitations in transmission channels. If the channel bandwidth is low,

signal transitions may not reach full amplitude before transitioning to a different logic state.

Starting at a level closer to the midpoint between logic states, the time at which the signal

edge then crosses a specific amplitude threshold can be early compared to consecutive

identical digits which have reached full amplitude and then switch to the other logic state

61280-2-3 © IEC:2009 – 9 –

3.11

duty cycle distortion

occurs when the duration of a logic 1 (0-1-0) is different from the duration of a logic 0 (1-0-1).

For example, if the logic 1 has a longer duration, rising edges will occur early relative to

falling edges, compared to their ideal locations in time

3.12

data dependent jitter

represents jitter that is correlated to specific bits in a repeating data pattern. That is, when a

data pattern repeats, the jitter on any given signal edge will manifest itself in the same way for

any repetition of the pattern. It is due to either duty cycle distortion and/or inter-symbol

interference

3.13

waiting time jitter

applies to plesiochronous multiplexing and is defined as the jitter caused by the varying delay

between the demand for justification and its execution

3.14

jitter tolerance

maximum jitter amplitude that a digital receiver can accept for a given penalty or alternatively

without the addition of a given number of errors to the digital signal. The maximum jitter

amplitude tolerated is generally dependent on the frequency of the jitter

3.15

jitter generation

process of adding jitter impairment to a data signal

3.16

input jitter

magnitude of the jitter occurring at a hierarchical interface or the input port of equipment or a

device

3.17

output jitter

magnitude of the jitter occurring at a hierarchical interface or the output port of equipment or a

device

3.18

jitter transfer

amount of jitter transferred from the input to the output of an equipment or device. It is usually

expressed as a ratio (in dB) of the output jitter to the input jitter

3.19

total jitter

the summation (or convolution) of deterministic and random jitter. Total jitter is expressed as

a peak value

3.20

jitter bathtub curve

display of bit-error-ratio as a function of the time location of the BERT error detector sampling

point. The resulting curve is then a display of the probability that a data edge will be

misplaced at or beyond a specific location (closer to the centre of a bit) within a unit interval

3.21

wander

long-term, non-cumulative, variation in time of the significant instances of a digital signal from

their ideal position in time. Long-term variations in this context are jitter components with a

repetition frequency less than 10 Hz

– 10 – 61280-2-3 © IEC:2009

NOTE For the purpose of this document, the wander amplitude is expressed in units of time (s). It is recognised

that wander amplitude may also be expressed in terms of unit interval (UI).

3.22

time interval error

TIE

difference between the measure of a time interval as provided by a clock and the measure of

that same time interval as provided by a reference clock. Mathematically, the time interval

error function TIE (t;τ) can be expressed as:

TIE(t;τ ) =[]T()t + τ − T(t) −[Tref (t + τ ) − Tref (t)] = x(t + τ ) − x(t) (1)

where τ is the time interval, usually called observation interval

3.23

maximum time interval error

MTIE

maximum peak-to-peak delay variation of a given timing signal with respect to an ideal timing

signal within an observation time (τ = nτ ) for all observation times of that length within the

measurement period (T). It is estimated using the following formula:

⎤

⎡

⎥

MTIE(nτ ) ≅ ⎢ − n = 1,2K N − 1 (2)

max max x min x

i i

⎥

⎢

1≤k≤N −n⎣ k≤i≤k+n k≤i≤k+n

⎥

⎦

3.24

time deviation

TDEV or σx

measure of the expected time variation of a signal as a function of integration time. TDEV can

also provide information about the spectral content of the phase (or time) noise of a signal.

TDEV is in units of time. Based on the sequence of time error samples, TDEV is estimated

using the following calculation:

N−3n+1 n+ j−1

⎡ ⎤

1 ⎛ N⎞

⎢ ⎥

TDEV()nτ ≅ ( − 2 + ) n = 1,2K,int part⎜ ⎟

(3)

∑ ∑

x x x

2 i+2n i+n i

⎢ ⎥ 3

6n (N − 3n + 1) ⎝ ⎠

j=1 i= j

⎣ ⎦

where

x denotes time error samples;

i

N denotes the total number of samples;

τ denotes the time error-sampling interval;

τ denotes the integration time, the independent variable of TDEV;

n denotes the number of sampling intervals within the integration time t.

3.25

bit error ratio

BER

number of bits received in error as a ratio of the total number of bits received

3.26

errored second

time of 1 s duration that contains one or more digital errors in a data stream

61280-2-3 © IEC:2009 – 11 –

4 General considerations

4.1 Jitter generation

Jitter in a digital signal is generated by three basic processes which are briefly described

below. The mathematical analysis of the jitter processes is complex and not within the scope

of this standard. A comprehensive analysis and early mathematical treatise of the jitter

processes is provided by [1] .

4.1.1 Timing jitter

Jitter impairment of the original data timing clock. Even the most stable timing sources

contain a certain amount of jitter, or unintended phase modulation or phase noise. In primary

timing generators this impairment is exceedingly small, but is increased when such timing

signals are distributed in a system. The effect of noise on the timing signal in a digital system

is demonstrated in an exaggerated degree in Figure 1.

Ideal timing

Noise on timing signal

Detection threshold

Timing signal

p- p Jitter amplitude

IEC 1164/09

Figure 1 – Jitter generation

4.1.2 Alignment jitter

When a digital pattern is presented to a timing recovery circuit, the continuous variation of the

digital pattern results in the creation of jitter in the recovered clock signal relative to the

incoming data (alignment jitter). This effect, first analyzed and described in detail by [2] is the

major cause of jitter generation. It means that the jitter components of the recovered clock

signal are added to the data when they are retimed. The jitter bandwidth created by this

process is the same as the analogue bandwidth of the clock recovery circuit used.

When the process is repeated at a similar equipment, the resultant clock signal shows

increased jitter due to the addition of timing and alignment jitter. Thus, jitter is added to the

data signal, and amplified at the next timing recovery operation. A repetition of this process,

such as occurs in transmission links with many repeaters, or chains of add-drop multiplexers,

can build up substantial jitter amplitudes; but as long as the bandwidth of the timing recovery

process is the same or greater than the jitter bandwidth of the signal, the jitter will always be

accommodated. An analysis of the accumulation of jitter in successive timing recovery

operations was first published by [3]. The jitter buildup can be represented by an equation of

the form:

—————————

Figures in square brackets refer to the Bibliography.

– 12 – 61280-2-3 © IEC:2009

k

n

⎛ 1 ⎞

θn = θ ( jω)⎜ ⎟ (4)

∑ 0

⎜ ⎟

1+ j ω / B

⎝ ⎠

k=1

The above equation yields a jitter power density spectrum which can be expressed in the

form:

⎡ n ⎤

sin ω

⎢ ⎥

2 2B

φ ≈ n φ for ω<

⎢ ⎥

n 0

n

⎢ ⎥

ω

⎢ ⎥

2B

⎣ ⎦

where

θ denotes the jitter amplitude after n timing recovery processes;

n

θ denotes the jitter amplitude introduced at each individual timing recovery process;

n denotes the number of tandem timing recovery processes;

ω denotes the angular frequency (2πf) of the jitter component;

B denotes the half angular bandwidth of the timing recovery circuit;

Ф denotes the jitter power density after n timing recovery processes;

n

Ф denotes the jitter power density introduced at each individual timing recovery process.

It should be noted that for low values of frequency the power density and hence amplitude of

the jitter increases linearly with the number of tandem timing recovery processes.

In point-to-point communications systems, where transmitter timing is not derived from

incoming data, alignment jitter and jitter build-up is not a significant problem.

4.1.3 Other effects

In the course of the transmission of a digital signal, further impairments such as added noise

and dispersion effects provide additional jitter components when timing is recovered from the

signal. Such effects are more severe when analogue amplification is used rather than digital

regeneration in order to increase the length of a digital link.

4.2 Effects of jitter on signal quality

Jitter has no effect on the transmission of data as long as the equipment can accommodate

the jitter amplitude and rate of deviation (see 4.3). When jitter is large enough or fast enough

such that the receiver decision point is made near or beyond a data edge, a mistake can be

made and BER degraded. Jitter, depending on its amplitude and frequency, can also have

serious effects on analogue services such as music and television which have been

transmitted over digital links. The effect of jitter is to introduce unwanted frequency and phase

modulation products which are audible in music and visible on television pictures.

4.3 Jitter tolerance

In telecommunications systems, jitter tolerance requirements are typically specified in terms

of jitter templates, which cover a specified sinusoidal amplitude/frequency region. Jitter

templates represent the minimum amount of jitter the equipment shall be able to accept

without producing the specified degradation of error performance. A typical relationship

between actual jitter tolerance and its associated tolerance template is illustrated in Figure 2.

The jitter amplitudes that equipment actually tolerates at a given frequency are defined as all

amplitudes up to, but not including, that which causes the designated degradation of error

performance. The designated degradation of error performance may be expressed in terms of

either bit-error-ratio (BER) penalty or the onset of errors criteria. The existence of these two

61280-2-3 © IEC:2009 – 13 –

criteria arises because the input jitter tolerance of digital equipment is primarily determined by

the following three factors:

a) ability of the input clock recovery circuit to accurately recover the timing from a jittered

data signal, including the presence of other degradations such as pulse distortion,

crosstalk, noise, and other impairments;

b) ability of the input circuit buffer, for example an elastic store, to accommodate the jitter

amplitude;

c) ability of other components to accommodate dynamically varying input data rates such

as pulse justification capacity and synchronizer and de-synchronizer buffer size in an

asynchronous digital multiplex.

Actual jitter tolerance

Operating jitter margin

Template specification

Acceptable region

dB/decade

Unacceptable region

IEC 1165/09

Figure 2 – Example of jitter tolerance

In data communications systems, jitter tolerance is often determined with signal impairments

that are more complex than simple sinusoidal jitter. The general concept is to verify that the

receiver is capable of achieving the desired BER when presented with the allowable signal it

will encounter in a real system. Thus the jitter tolerance test signal will include impairments

that are allowed for both the transmitter and the channel. For example, a real transmitter may

have periodic jitter, random jitter, and duty cycle distortion. As the signal traverses the

channel, it may be further degraded through a bandwidth limited channel, thus adding inter-

symbol interference jitter. As the receiver shall be able to tolerate such a signal in a real

system, the signal used to verify receiver tolerance shall include all of these impairments.

This method of testing is sometimes referred to as “stressed eye” testing, indicating that the

eye diagram of the signal presented to a receiver has been intentionally degraded or

stressed.

4.4 Waiting time jitter

When asynchronous (plesiochronous) signals are multiplexed, a justification technique (also

known as pulse stuffing) is used which involves the comparison of the phase of the incoming

digital signal with the multiplexer’s tributary timing. When a preset difference is detected a

control signal is transmitted, via the overhead in the multiplex frame structure, to the

demultiplexer. In order to ensure the integrity of the control signal in the presence of errors, it

is repeated 3 or 5 times. At the demultiplexer a majority decision is taken to recognize the

– 14 – 61280-2-3 © IEC:2009

control signal. This delay introduces an uncertainty and varying delay in the time between the

demand for justification and its execution at the demultiplexer, and expresses itself as waiting

time jitter.

4.5 Wander

Wander is essentially caused by periodic variations in the delay of a transmission path and

slow variations in the frequency of data clocks. The boundary between jitter and wander at a

frequency of 10 Hz is somewhat artificial since most significant wander effects occur at

repetition rates of hours, days, months and seasons. In general wander is caused by

temperature changes which affect the delays of the transmission medium or equipment. For

terrestrial transmission, wander components are normally limited to a few tens of

nanoseconds.

In synchronous networks the accommodation of wander is an essential feature since a single

bit slip will initiate a resynchronization process with consequent loss of data. If this occurs at

a high level demultiplexer, all lower levels will also resynchronize which will exacerbate the

loss of data. Wander is normally accommodated by increasing the size of the elastic store

used to accommodate jitter.

A special case is the wander effect that occurs in communications via geostationary satellites.

While the lateral position of such satellites is relatively stable, their mean height of some

35 000 km above the earth’s surface has a diurnal variation which may be up to approximately

±1 000 km. This results in delay variations per hop of approximately 26 ms. At a data rate of

150 Mbit/s this represents a wander rate of some 45 bits/s and requires an elastic store with a

capacity of at least 3

...

Questions, Comments and Discussion