IEC 60747-5-6:2016

(Main)Semiconductor devices - Part 5-6: Optoelectronic devices - Light emitting diodes

Semiconductor devices - Part 5-6: Optoelectronic devices - Light emitting diodes

IEC 60747-5-6:2016 specifies the terminology, the essential ratings and characteristics, the measuring methods and the quality evaluations of light emitting diodes (LEDs) for general industrial applications such as signals, controllers, sensors, etc. LEDs for lighting applications are out of the scope of this part of IEC 60747. The types of LED are divided into the following five classes:

a) LED package;

b) LED flat illuminator;

c) LED numeric display and alpha-numeric display;

d) LED dot-matrix display;

e) I LED (infrared-emitting diode).

LEDs with a heat spreader or having a terminal geometry that performs the function of a heat spreader are within the scope of this part of IEC 60747. An integration of LEDs and controlgears, integrated LED modules, semi-integrated LED modules, integrated LED lamps or semi-integrated LED lamps, are out of the scope of this part of IEC 60747. This first edition of IEC 60747-5-6, together with IEC 60747-5-4, IEC 60747-5-5 and IEC 60747-5-7, cancels and replaces IEC 60747-5-1, IEC 60747-5-2 and IEC 60747-5-3, published in 1997, and their amendments. This edition constitutes a technical revision. This edition includes significant technical changes to the clauses for light emitting diodes in IEC 60747-5-1:1997, IEC 60747-5-2:1997 and IEC 60747-5-3:1997, including their amendments.

Dispositifs à semiconducteurs - Partie 5-6: Dispositifs optoélectroniques - Diodes électroluminescentes

L'IEC 60747-5-6:2016 spécifie la terminologie, les caractéristiques et caractéristiques assignées essentielles, les méthodes de mesure et les appréciations de qualité des diodes électroluminescentes (DEL), pour des applications industrielles générales telles que les signaux, les contrôleurs, les capteurs, etc. Les DEL destinées aux applications d'éclairage sont exclues du domaine d'application de la présente partie de l'IEC 60747. Les types de DEL sont divisés en cinq catégories comme suit:

a) groupe multi DEL;

b) illuminateur plat à DEL;

c) afficheur numérique et afficheur alphanumérique à DEL;

d) afficheur à matrice de points à DEL;

e) DEL infrarouge.

Les DEL munies d'un diffuseur de chaleur, ou dont la géométrie des bornes remplit la fonction de diffuseur de chaleur, sont incluses dans le domaine d'application de la présente partie de l'IEC 60747. Les intégrations de DEL et d'appareillage de commande, les modules DEL intégrés ou semi-intégrés, ou bien les lampes DEL intégrées ou semi-intégrées, sont exclus du domaine d'application de la présente partie de l'IEC 60747. Cette première édition de l'IEC 60747-5-6, ainsi que l'IEC 60747-5-4, l'IEC 60747-5-5 et l'IEC 60747-5-7, annulent et remplacent l'IEC 60747-5-1, l'IEC 60747-5-2 et l'IEC 60747-5-3, parues en 1997, y compris leurs amendements, suite à une refonte. Cette édition constitue une révision technique. Cette édition inclut des modifications techniques majeures aux articles traitant des diodes électroluminescentes dans l'IEC 60747-5-1:1997, l'IEC 60747-5-2:1997 et l'IEC 60747-5-3:1997, y compris leurs amendements.

General Information

- Status

- Published

- Publication Date

- 22-Feb-2016

- Technical Committee

- SC 47E - Discrete semiconductor devices

- Drafting Committee

- WG 9 - TC 47/SC 47E/WG 9

- Current Stage

- DELPUB - Deleted Publication

- Start Date

- 06-Jul-2021

- Completion Date

- 29-Mar-2019

Relations

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

Overview

IEC 60747-5-6:2016 is an international standard published by the International Electrotechnical Commission (IEC) that focuses on semiconductor optoelectronic devices, specifically light emitting diodes (LEDs). This standard establishes the terminology, essential ratings, characteristics, measurement methods, and quality evaluation criteria for LEDs designed for general industrial applications such as signals, controllers, and sensors. It excludes LEDs intended for lighting applications.

The document provides comprehensive guidelines applicable to various types of LEDs, including LED packages, flat illuminators, numeric and alphanumeric displays, dot-matrix displays, and infrared-emitting diodes. The edition released in 2016 represents a significant technical revision, replacing previous IEC standards on LEDs and updating testing procedures and terminology to reflect advances in optoelectronic technology.

Key Topics

Terminology and Definitions

The standard defines critical terms related to LED characteristics, radiation measurement, and photometric quantities to ensure consistent understanding across the industry.Absolute Maximum Ratings

Specifies the maximum permissible electrical and thermal limits for LEDs to maintain safe and reliable operation.Electrical and Optical Characteristics

Details parameters such as forward and reverse voltage, differential resistance, reverse current, and luminous flux vital for LED performance benchmarking.Measurement Methods

Comprehensive procedures cover measurement of key parameters including:- Forward/reverse voltage and current

- Capacitance and differential resistance

- Junction temperature and thermal resistance

- Response time and frequency response

- Luminous flux, radiant power, luminous and radiant intensity

- Luminance, emission spectrum, peak wavelength, and spectral bandwidth

- Chromaticity and directional characteristics

Quality Evaluation

The standard emphasizes quality control through precise testing, ensuring LEDs meet industrial application requirements.

Applications

IEC 60747-5-6:2016 supports the design, testing, and quality assurance of LEDs used in an extensive variety of industrial equipment:

Signal Indicators

Used in control panels and machinery to provide status indication through LEDs that comply with defined electrical and optical standards.Controllers and Sensors

Ensures consistent performance for LEDs integrated into control systems and sensor devices requiring reliable optoelectronic emission.Display Technologies

Applied for numeric, alphanumeric, and dot-matrix LED displays, improving measurement accuracy and functional consistency.Infrared Communication and Sensing

Defines specifications for infrared-emitting diodes, facilitating their use in remote controls, data transmission, and detection systems.

This standard aids manufacturers and engineers in developing LEDs that deliver robust, reproducible performance for industrial applications while excluding general lighting products for which separate standards apply.

Related Standards

IEC 60747-5-6:2016 is part of a broader family of IEC standards covering semiconductor optoelectronic devices. It works in conjunction with:

IEC 60747-5-4, -5, and -7

Other parts addressing different types of optoelectronic devices and related measurement and testing practices.IEC 60747-5-1, -2, and -3 (Superseded)

Previous editions related to LEDs replaced by the 2016 revision to harmonize terminology and testing procedures.

For lighting applications involving LEDs or integrated LED modules, separate specialized standards apply, ensuring comprehensive coverage across all LED use cases.

Keywords: IEC 60747-5-6, LED standards, light emitting diodes, optoelectronic devices, LED measurement methods, industrial LED applications, luminous flux measurement, LED electrical characteristics, semiconductor device standards, IEC LED testing

Frequently Asked Questions

IEC 60747-5-6:2016 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Semiconductor devices - Part 5-6: Optoelectronic devices - Light emitting diodes". This standard covers: IEC 60747-5-6:2016 specifies the terminology, the essential ratings and characteristics, the measuring methods and the quality evaluations of light emitting diodes (LEDs) for general industrial applications such as signals, controllers, sensors, etc. LEDs for lighting applications are out of the scope of this part of IEC 60747. The types of LED are divided into the following five classes: a) LED package; b) LED flat illuminator; c) LED numeric display and alpha-numeric display; d) LED dot-matrix display; e) I LED (infrared-emitting diode). LEDs with a heat spreader or having a terminal geometry that performs the function of a heat spreader are within the scope of this part of IEC 60747. An integration of LEDs and controlgears, integrated LED modules, semi-integrated LED modules, integrated LED lamps or semi-integrated LED lamps, are out of the scope of this part of IEC 60747. This first edition of IEC 60747-5-6, together with IEC 60747-5-4, IEC 60747-5-5 and IEC 60747-5-7, cancels and replaces IEC 60747-5-1, IEC 60747-5-2 and IEC 60747-5-3, published in 1997, and their amendments. This edition constitutes a technical revision. This edition includes significant technical changes to the clauses for light emitting diodes in IEC 60747-5-1:1997, IEC 60747-5-2:1997 and IEC 60747-5-3:1997, including their amendments.

IEC 60747-5-6:2016 specifies the terminology, the essential ratings and characteristics, the measuring methods and the quality evaluations of light emitting diodes (LEDs) for general industrial applications such as signals, controllers, sensors, etc. LEDs for lighting applications are out of the scope of this part of IEC 60747. The types of LED are divided into the following five classes: a) LED package; b) LED flat illuminator; c) LED numeric display and alpha-numeric display; d) LED dot-matrix display; e) I LED (infrared-emitting diode). LEDs with a heat spreader or having a terminal geometry that performs the function of a heat spreader are within the scope of this part of IEC 60747. An integration of LEDs and controlgears, integrated LED modules, semi-integrated LED modules, integrated LED lamps or semi-integrated LED lamps, are out of the scope of this part of IEC 60747. This first edition of IEC 60747-5-6, together with IEC 60747-5-4, IEC 60747-5-5 and IEC 60747-5-7, cancels and replaces IEC 60747-5-1, IEC 60747-5-2 and IEC 60747-5-3, published in 1997, and their amendments. This edition constitutes a technical revision. This edition includes significant technical changes to the clauses for light emitting diodes in IEC 60747-5-1:1997, IEC 60747-5-2:1997 and IEC 60747-5-3:1997, including their amendments.

IEC 60747-5-6:2016 is classified under the following ICS (International Classification for Standards) categories: 31.080.99 - Other semiconductor devices. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 60747-5-6:2016 has the following relationships with other standards: It is inter standard links to IEC 60747-5-1:1997, IEC 60747-5-2:1997/AMD1:2002, IEC 60747-5-1:1997/AMD1:2001, IEC 60747-5-2:1997, IEC 60747-5-3:1997/AMD1:2002, IEC 60747-5-1:1997/AMD2:2002, IEC 60747-5-3:1997, IEC 60747-5-6:2021. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 60747-5-6:2016 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC 60747-5-6 ®

Edition 1.0 2016-02

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

Semiconductor devices –

Part 5-6: Optoelectronic devices – Light emitting diodes

Dispositifs à semiconducteurs –

Partie 5-6: Dispositifs optoélectroniques – Diodes électroluminescentes

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form

or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from

either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC

copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or

your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite

ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie

et les microfilms, sans l'accord écrit de l'IEC ou du Comité national de l'IEC du pays du demandeur. Si vous avez des

questions sur le copyright de l'IEC ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez

les coordonnées ci-après ou contactez le Comité national de l'IEC de votre pays de résidence.

IEC Central Office Tel.: +41 22 919 02 11

3, rue de Varembé Fax: +41 22 919 03 00

CH-1211 Geneva 20 info@iec.ch

Switzerland www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

IEC Catalogue - webstore.iec.ch/catalogue Electropedia - www.electropedia.org

The stand-alone application for consulting the entire The world's leading online dictionary of electronic and

bibliographical information on IEC International Standards, electrical terms containing 20 000 terms and definitions in

Technical Specifications, Technical Reports and other English and French, with equivalent terms in 15 additional

documents. Available for PC, Mac OS, Android Tablets and languages. Also known as the International Electrotechnical

iPad. Vocabulary (IEV) online.

IEC publications search - www.iec.ch/searchpub IEC Glossary - std.iec.ch/glossary

The advanced search enables to find IEC publications by a 65 000 electrotechnical terminology entries in English and

variety of criteria (reference number, text, technical French extracted from the Terms and Definitions clause of

committee,…). It also gives information on projects, replaced IEC publications issued since 2002. Some entries have been

and withdrawn publications. collected from earlier publications of IEC TC 37, 77, 86 and

CISPR.

IEC Just Published - webstore.iec.ch/justpublished

Stay up to date on all new IEC publications. Just Published IEC Customer Service Centre - webstore.iec.ch/csc

details all new publications released. Available online and If you wish to give us your feedback on this publication or

also once a month by email. need further assistance, please contact the Customer Service

Centre: csc@iec.ch.

A propos de l'IEC

La Commission Electrotechnique Internationale (IEC) est la première organisation mondiale qui élabore et publie des

Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications IEC

Le contenu technique des publications IEC est constamment revu. Veuillez vous assurer que vous possédez l’édition la

plus récente, un corrigendum ou amendement peut avoir été publié.

Catalogue IEC - webstore.iec.ch/catalogue Electropedia - www.electropedia.org

Application autonome pour consulter tous les renseignements

Le premier dictionnaire en ligne de termes électroniques et

bibliographiques sur les Normes internationales,

électriques. Il contient 20 000 termes et définitions en anglais

Spécifications techniques, Rapports techniques et autres

et en français, ainsi que les termes équivalents dans 15

documents de l'IEC. Disponible pour PC, Mac OS, tablettes

langues additionnelles. Egalement appelé Vocabulaire

Android et iPad.

Electrotechnique International (IEV) en ligne.

Recherche de publications IEC - www.iec.ch/searchpub

Glossaire IEC - std.iec.ch/glossary

La recherche avancée permet de trouver des publications IEC 65 000 entrées terminologiques électrotechniques, en anglais

en utilisant différents critères (numéro de référence, texte, et en français, extraites des articles Termes et Définitions des

comité d’études,…). Elle donne aussi des informations sur les publications IEC parues depuis 2002. Plus certaines entrées

projets et les publications remplacées ou retirées. antérieures extraites des publications des CE 37, 77, 86 et

CISPR de l'IEC.

IEC Just Published - webstore.iec.ch/justpublished

Service Clients - webstore.iec.ch/csc

Restez informé sur les nouvelles publications IEC. Just

Published détaille les nouvelles publications parues. Si vous désirez nous donner des commentaires sur cette

Disponible en ligne et aussi une fois par mois par email. publication ou si vous avez des questions contactez-nous:

csc@iec.ch.

IEC 60747-5-6 ®

Edition 1.0 2016-02

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

Semiconductor devices –

Part 5-6: Optoelectronic devices – Light emitting diodes

Dispositifs à semiconducteurs –

Partie 5-6: Dispositifs optoélectroniques – Diodes électroluminescentes

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION

ELECTROTECHNIQUE

INTERNATIONALE

ICS 31.080.99 ISBN 978-2-8322-3209-5

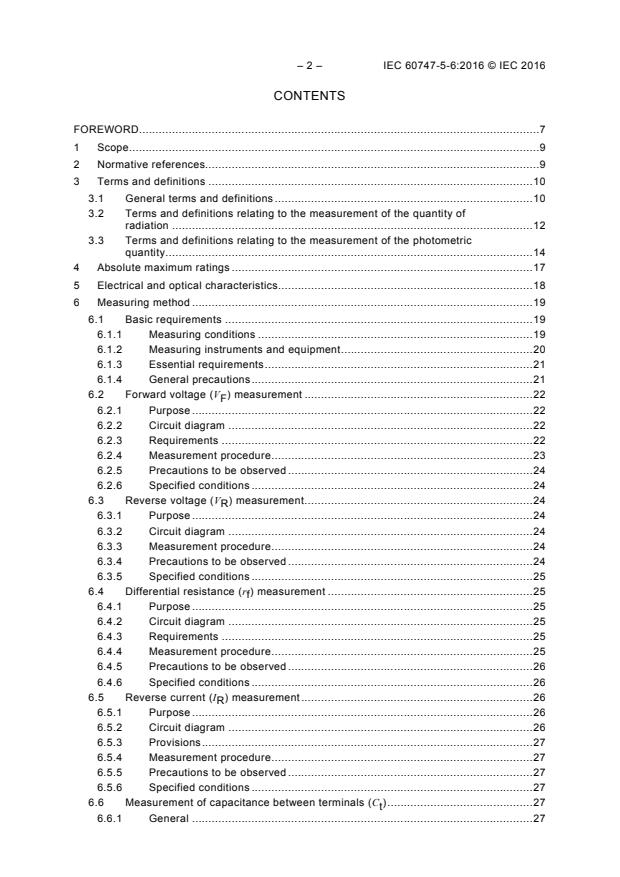

– 2 – IEC 60747-5-6:2016 © IEC 2016

CONTENTS

FOREWORD . 7

1 Scope . 9

2 Normative references. 9

3 Terms and definitions . 10

3.1 General terms and definitions . 10

3.2 Terms and definitions relating to the measurement of the quantity of

radiation . 12

3.3 Terms and definitions relating to the measurement of the photometric

quantity . 14

4 Absolute maximum ratings . 17

5 Electrical and optical characteristics . 18

6 Measuring method . 19

6.1 Basic requirements . 19

6.1.1 Measuring conditions . 19

6.1.2 Measuring instruments and equipment . 20

6.1.3 Essential requirements . 21

6.1.4 General precautions . 21

6.2 Forward voltage (V ) measurement . 22

F

6.2.1 Purpose . 22

6.2.2 Circuit diagram . 22

6.2.3 Requirements . 22

6.2.4 Measurement procedure . 23

6.2.5 Precautions to be observed . 24

6.2.6 Specified conditions . 24

6.3 Reverse voltage (V ) measurement . 24

R

6.3.1 Purpose . 24

6.3.2 Circuit diagram . 24

6.3.3 Measurement procedure . 24

6.3.4 Precautions to be observed . 24

6.3.5 Specified conditions . 25

6.4 Differential resistance (r ) measurement . 25

f

6.4.1 Purpose . 25

6.4.2 Circuit diagram . 25

6.4.3 Requirements . 25

6.4.4 Measurement procedure . 25

6.4.5 Precautions to be observed . 26

6.4.6 Specified conditions . 26

6.5 Reverse current (I ) measurement . 26

R

6.5.1 Purpose . 26

6.5.2 Circuit diagram . 26

6.5.3 Provisions . 27

6.5.4 Measurement procedure . 27

6.5.5 Precautions to be observed . 27

6.5.6 Specified conditions . 27

6.6 Measurement of capacitance between terminals (C ) . 27

t

6.6.1 General . 27

6.6.2 Measurement using LCR meter . 27

6.6.3 Measurement using AC bridge . 28

6.7 Measurement of junction temperature and thermal resistance (R ) . 29

th(j-X)

6.7.1 Purpose . 29

6.7.2 Measurement principle . 29

6.7.3 Measurement procedure . 30

6.7.4 Precautions to be observed . 33

6.8 Response time measurement . 34

6.8.1 Purpose . 34

6.8.2 Circuit diagram . 34

6.8.3 Provisions . 34

6.8.4 Measurement procedure . 34

6.8.5 Precautions to be observed . 35

6.8.6 Specified conditions . 35

6.9 Frequency response and cut-off frequency (f ) measurement . 36

c

6.9.1 Purpose . 36

6.9.2 Circuit diagram . 36

6.9.3 Provisions . 37

6.9.4 Measurement procedure . 37

6.9.5 Precautions to be observed . 38

6.9.6 Specified conditions . 38

6.10 Luminous flux (Φ ) measurement . 38

V

6.10.1 Purpose . 38

6.10.2 Measurement principle . 38

6.10.3 Measuring circuit . 38

6.10.4 Measurement procedure . 39

6.10.5 Precautions to be observed . 39

6.10.6 Measurement conditions to be defined . 40

6.11 Radiant power (Φ ) measurement . 40

e

6.11.1 Purpose . 40

6.11.2 Measurement principle . 40

6.11.3 Measuring circuit . 40

6.11.4 Measurement procedure . 41

6.11.5 Precautions to be observed . 41

6.11.6 Measurement conditions to be defined . 42

6.12 Luminous intensity (I ) measurement . 42

V

6.12.1 Purpose . 42

6.12.2 Measurement principle . 42

6.12.3 Measuring circuit . 43

6.12.4 Measurement procedure . 44

6.12.5 Precautions to be observed . 44

6.12.6 Measurement conditions to be defined . 44

6.13 Radiant intensity (I ) measurement . 44

e

6.13.1 Purpose . 44

6.13.2 Measurement principle . 44

6.13.3 Measuring circuit . 45

6.13.4 Measurement procedure . 45

6.13.5 Measurement conditions to be defined . 45

6.14 Luminance (L ) measurement . 45

v

– 4 – IEC 60747-5-6:2016 © IEC 2016

6.14.1 Purpose . 45

6.14.2 Measuring circuit . 46

6.14.3 Measurement procedure . 46

6.14.4 Measurement conditions to be defined . 46

6.15 Emission spectrum distribution, peak emission wavelength (λ ), and spectral

p

half bandwidth (∆λ) measurement . 47

6.15.1 Purpose . 47

6.15.2 Measuring circuit . 47

6.15.3 Measurement procedure . 48

6.15.4 Measurement conditions to be defined . 48

6.16 Chromaticity measurement . 49

6.16.1 Purpose . 49

6.16.2 Measurement principle . 49

6.16.3 Measuring circuit . 51

6.16.4 Measurement procedure . 51

6.16.5 Measuring conditions to be defined . 51

6.17 Directional characteristics measurement . 51

6.17.1 Purpose . 51

6.17.2 Measuring circuit . 51

6.17.3 Measurement procedure . 52

6.17.4 Measuring conditions to be defined . 53

6.18 Illuminance (E ) measurement . 54

V

6.18.1 Purpose . 54

6.18.2 Measuring circuit . 54

6.18.3 Measurement procedure . 54

6.18.4 Measuring conditions to be defined . 54

7 Items to be indicated on the package . 54

8 Quality evaluation . 55

8.1 Classification of quality evaluations . 55

8.1.1 General . 55

8.1.2 Classification I . 55

8.1.3 Classification II . 55

8.1.4 Classification III . 55

8.1.5 Precautions to be observed . 55

8.2 Quality evaluation test . 60

8.2.1 General . 60

8.2.2 Specimens . 60

8.3 Lot quality inspection . 60

8.3.1 General . 60

8.3.2 Specimens . 60

8.4 Periodical quality inspection . 60

8.4.1 General . 60

8.4.2 Specimens . 60

8.4.3 Inspection period . 60

8.5 Easing of the lot quality inspection standards . 61

8.6 Periodical evaluation maintenance tests . 61

8.6.1 Test items and specimens . 61

8.6.2 Test period . 61

8.7 Long-term storage products . 61

8.8 Continuous current test . 61

8.8.1 General . 61

8.8.2 Initial measurement . 61

8.8.3 Test circuits . 61

8.8.4 Test conditions . 62

8.8.5 Post-treatment . 62

8.8.6 Final measurement . 62

Annex A (normative) Standard luminous efficiency . 63

Annex B (normative) How to obtain the self-absorption correction factor . 66

B.1 Purpose . 66

B.2 LED light sources for self-absorption measurement . 66

B.3 Method . 66

Annex C (normative) How to obtain the colour correction factor . 68

C.1 Purpose . 68

C.2 Method . 68

C.2.1 Luminous flux and luminous intensity measurement . 68

C.2.2 Radiant power and radiant intensity measurement . 69

Annex D (normative) Calibration of the luminance meter . 70

D.1 Purpose . 70

D.2 How to perform the calibration . 70

Annex E (normative) Colour-matching function of the XYZ colour system . 72

Annex F (normative) Spectral chromaticity coordinates . 77

Annex G (normative) Illuminometer calibration . 82

G.1 Purpose . 82

G.2 How to perform the calibration . 82

Bibliography . 83

Figure 1 – Radiant intensity . 12

Figure 2 – Radiance . 13

Figure 3 – Radiant exitance . 14

Figure 4 – Irradiance . 14

Figure 5 – Spectral luminous efficiency . 15

Figure 6 – Circuit diagram for V measurement . 22

F

Figure 7 – Circuit diagram for V measurement with a constant voltage source and a

F

current-limiting resistor . 23

Figure 8 – Circuit diagram for V measurement using an SMU . 23

F

Figure 9 – Circuit diagram for V measurement . 24

R

Figure 10 – circuit diagram for r mesurement . 25

f

Figure 11 – Circuit diagram for I measurement . 26

R

Figure 12 – Circuit diagram for C measurement . 27

t

Figure 13 – Circuit diagram for C measurement . 28

t

Figure 14 – Circuit diagram for measurement of change in V . 30

F

Figure 15 – Waveform of change in V . 32

F

Figure 16 – Transient change in thermal resistance (double-logarithmic plots) . 33

Figure 17 – Circuit diagram for response time measurement . 34

Figure 18 – Waveform of response time measurement . 36

– 6 – IEC 60747-5-6:2016 © IEC 2016

Figure 19 – Circuit diagram for f measurement . 37

c

Figure 20 – Circuit diagram for Φ measurement. 39

V

Figure 21 – circuit diagram for Φ measurement . 41

e

Figure 22 – Schematic diagram for I measurement . 43

V

Figure 23 – Circuit diagram for I measurement . 43

V

Figure 24 – circuit diagram for I measurement . 45

e

Figure 25 – Circuit diagram for L measurement . 46

v

Figure 26 – Circuit diagram for λ measurement . 47

p

Figure 27 – Circuit diagram for λ measurement . 48

p

Figure 28 – Schematic diagram of ∆λ measurement . 48

Figure 29 – Chromaticity . 50

Figure 30 – Circuit diagram for chromaticity measurement . 52

Figure 31 – Directional characteristics (example 1) . 53

Figure 32 – Directional characteristics (example 2) . 53

Figure 33 – Circuit diagram for E measurement. 54

v

Figure 34 – Circuit diagram for continuous current test . 62

Figure B.1 – Schematic diagram for self-absorption measurement . 66

Figure D.1 – Schematic diagrams for calibration . 71

Figure G.1 – Schematic diagram for calibration . 82

Table 1 – Absolute maximum ratings . 18

Table 2 – Electrical and optical characteristics . 19

Table 3 – CIE averaged LED intensity measurements . 43

Table 4 – Items for the screening test and their conditions(reference) . 55

Table 5 – Quality evaluation tests (1 of 2) . 56

Table 6 – Lot quality inspection . 58

Table 7 – Periodical quality inspection . 59

Table A.1 – Definitive values of the spectral luminous efficiency function for photopic

vision V(λ) (1 of 3) . 63

Table E.1 – Colour-matching function of the XYZ colour system (1 of 5) . 72

Table F.1 – Spectral chromaticity coordinates (1 of 5). 77

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

SEMICONDUCTOR DEVICES –

Part 5-6: Optoelectronic devices – Light emitting diodes

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 60747-5-6 has been prepared by subcommittee 47E: Discrete

semiconductor devices, of IEC technical committee 47: Semiconductor devices.

This first edition of IEC 60747-5-6, together with IEC 60747-5-4, IEC 60747-5-5 and

IEC 60747-5-7, cancels and replaces IEC 60747-5-1, IEC 60747-5-2 and IEC 60747-5-3,

published in 1997, and their amendments. This edition constitutes a technical revision.

This edition includes significant technical changes to the clauses for light emitting diodes in

IEC 60747-5-1:1997, IEC 60747-5-2:1997 and IEC 60747-5-3:1997, including their

amendments.

– 8 – IEC 60747-5-6:2016 © IEC 2016

The text of this standard is based on the following documents:

FDIS Rapport de vote

47E/529/FDIS 47E/535/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all parts in the IEC 60747 series, published under the general title Semiconductor

devices, can be found on the IEC website.

The committee has decided that the contents of this publication will remain unchanged until

the stability date indicated on the IEC website under "http://webstore.iec.ch" in the data

related to the specific publication. At this date, the publication will be

• reconfirmed,

• withdrawn,

• replaced by a revised edition, or

• amended.

SEMICONDUCTOR DEVICES –

Part 5-6: Optoelectronic devices – Light emitting diodes

1 Scope

This part of IEC 60747 specifies the terminology, the essential ratings and characteristics, the

measuring methods and the quality evaluations of light emitting diodes (LEDs) for general

industrial applications such as signals, controllers, sensors, etc. LEDs for lighting applications

are out of the scope of this part of IEC 60747.

The types of LED are divided into the following five classes:

a) LED package;

b) LED flat illuminator;

c) LED numeric display and alpha-numeric display;

d) LED dot-matrix display;

e) I LED (infrared-emitting diode).

LEDs with a heat spreader or having a terminal geometry that performs the function of a heat

spreader are within the scope of this part of IEC 60747.

An integration of LEDs and controlgears, integrated LED modules, semi-integrated LED

modules, integrated LED lamps or semi-integrated LED lamps, are out of the scope of this

part of IEC 60747.

2 Normative references

The following documents, in whole or in part, are normatively referenced in this document and

are indispensable for its application. For dated references, only the edition cited applies. For

undated references, the latest edition of the referenced document (including any

amendments) applies.

IEC 60051 (all parts), Direct acting indicating analogue electrical measuring instruments and

their accessories

IEC 60068-2-30, Environmental testing – Part 2-30: Tests – Test Db: Damp heat, cyclic

(12 h + 12 h cycle)

IEC 60749-6, Semiconductor devices – Mechanical and climatic test methods – Part 6:

Storage at high temperature

IEC 60749-10, Semiconductor devices – Mechanical and climatic test methods – Part 10:

Mechanical shock

IEC 60749-12, Semiconductor devices – Mechanical and climatic test methods – Part 12:

Vibration, variable frequency

IEC 60749-14, Semiconductor devices – Mechanical and climatic test methods – Part 14:

Robustness of terminations (lead integrity)

– 10 – IEC 60747-5-6:2016 © IEC 2016

IEC 60749-15 Semiconductor devices – Mechanical and climatic test methods – Part 15:

Resistance to soldering temperature for through-hole mounted devices

IEC 60749-20 Semiconductor devices – Mechanical and climatic test methods – Part 20:

Resistance of plastic encapsulated SMDs to the combined effect of moisture and soldering

heat

IEC 60749-21 Semiconductor devices – Mechanical and climatic test methods – Part 21:

Solderability

IEC 60749-24 Semiconductor devices – Mechanical and climatic test methods – Part 24:

Accelerated moisture resistance – Unbiased HAST

IEC 60749-25 Semiconductor devices – Mechanical and climatic test methods – Part 25:

Temperature cycling

IEC 60749-36 Semiconductor devices – Mechanical and climatic test methods – Part 36:

Acceleration, steady state

ISO 2859, Sampling procedures for inspection by attributes

3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

3.1 General terms and definitions

3.1.1

integrating sphere

hollow sphere whose internal surface is a diffuse reflector, as non-selective as possible

[SOURCE: IEC 60050-845:1987, 845-05-24, modified – The term "Ulbricht sphere" and the

note have been removed.]

3.1.2

diffuse reflector

reflector composed of a surface with diffuse reflection

3.1.3

diffuse reflection

diffusion by reflection in which, on the macroscopic scale, there is no regular reflection

[SOURCE: IEC 60050-845:1987, 845-04-47]

3.1.4

diffuse transmission

diffusion by transmission in which, on the macroscopic scale, there is no regular transmission

[SOURCE: IEC 60050-845:1987, 845-04-48]

3.1.5

diffuse reflectance

R

d

ratio of the diffusely reflected part of the (whole) reflected flux, to the incident flux

Note 1 to entry: R = R + R

r d

Note 2 to entry: The results of the measurements of R and R depend on the instruments and the measuring

r d

techniques used.

[SOURCE: IEC 60050-845:1987, 845-04-62]

3.1.6

diffuse transmittance

T

d

ratio of the diffusely transmitted part of the (whole) transmitted flux, to the incident flux

Note 1 to entry: T = T + T

r d

Note 2 to entry: The results of the measurements of T and T depend on the instruments and the measuring

r d

techniques used.

[SOURCE: IEC 60050-845:1987, 845-04-63]

3.1.7

lambertian surface

ideal surface for which the radiation coming from that surface is distributed angularly

according to Lambert's cosine law

Note 1 to entry: For a lambertian surface, M = πL, where M is the radiant or luminous exitance, and L the radiance

or luminance.

[SOURCE: IEC 60050-845:1987, 845-04-57]

3.1.8

spectral reflectance

R(λ)

ratio between the spectral radiant flux of wavelength λ that is reflected by an object and the

spectral radiant flux of wavelength λ that is absorbed by the object

Note 1 to entry: Spectral reflectance is also known as the “spectral reflection factor.”

3.1.9

spectral transmittance

T(λ)

ratio between the spectral radiant flux of wavelength λ that is transmitted by an object and the

spectral radiant flux of wavelength λ that is absorbed by the object

Note 1 to entry: Spectral transmittance is also known as the “spectral transmittance factor”.

3.1.10

spectral distribution

proportion of the quantum of radiation per unit wavelength included in the micro wavelength

interval centre on wavelength λ, which is expressed as a function of wavelength λ

Note 1 to entry: Spectral distribution is also known as the “spectrum distribution”.

3.1.11

spectral sensitivity

S(λ)

light sensitivity as a function of wavelength

Note 1 to entry: The response output of the optical receiver for the radiant power (or luminous flux) input of

wavelength λ is expressed as a function of wavelength λ.

– 12 – IEC 60747-5-6:2016 © IEC 2016

3.1.12

distribution temperature

temperature of the Planckian radiator whose relative spectral distribution S(λ) is the same or

nearly the same as that of the radiation considered in the spectral range of interest

Note 1 to entry: The unit used is: K.

[SOURCE: IEC 60050-845:1987, 845-04-14]

3.2 Terms and definitions relating to the measurement of the quantity of radiation

3.2.1

radiant energy

Q

e

time integral of the radiant flux Φ over a given duration ∆t

e

Q = Φ dt

e e

∫

∆t

Note 1 to entry: The unit used is: J (1 J = 1 W ⋅ s).

[SOURCE: IEC 60050-845:1987, 845-01-27]

3.2.2

radiant flux

Φ

e

power emitted, transmitted or received in the form of radiation

dQ

e

Φ =

e

dt

Note 1 to entry: The unit used is: W.

[SOURCE: IEC 60050-845:1987, 845-01-24, modified – The formula has been added.]

3.2.3

radiant intensity

I

e

quotient of the radiant flux dΦ leaving the source and propagated in the element of solid

e

angle dΩ containing the given direction, by the element of solid angle

dΦ

e

(dΩ: solid angle)

I =

e

dΩ

Source

dΦ

dΩ I

e

e

IEC

Figure 1 – Radiant intensity

Note 1 to entry: For a rad

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...