IEC 60747-5-3:1997/AMD1:2002

(Amendment)Amendment 1 - Discrete semiconductor devices and integrated circuits - Part 5-3: Optoelectronic devices - Measuring methods

Amendment 1 - Discrete semiconductor devices and integrated circuits - Part 5-3: Optoelectronic devices - Measuring methods

Amendement 1 - Dispositifs discrets à semiconducteurs et circuits intégrés - Partie 5-3: Dispositifs optoélectroniques - Méthodes de mesure

General Information

- Status

- Replaced

- Publication Date

- 24-Mar-2002

- Technical Committee

- SC 47E - Discrete semiconductor devices

- Drafting Committee

- WG 9 - TC 47/SC 47E/WG 9

- Current Stage

- DELPUB - Deleted Publication

- Start Date

- 23-Feb-2016

- Completion Date

- 13-Feb-2026

Relations

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

Frequently Asked Questions

IEC 60747-5-3:1997/AMD1:2002 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Amendment 1 - Discrete semiconductor devices and integrated circuits - Part 5-3: Optoelectronic devices - Measuring methods". This standard covers: Amendment 1 - Discrete semiconductor devices and integrated circuits - Part 5-3: Optoelectronic devices - Measuring methods

Amendment 1 - Discrete semiconductor devices and integrated circuits - Part 5-3: Optoelectronic devices - Measuring methods

IEC 60747-5-3:1997/AMD1:2002 is classified under the following ICS (International Classification for Standards) categories: 31.080.99 - Other semiconductor devices. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 60747-5-3:1997/AMD1:2002 has the following relationships with other standards: It is inter standard links to IEC 60747-5-5:2007, IEC 60747-5-7:2016, IEC 60747-5-4:2006, IEC 60747-5-6:2016, IEC 60747-5-3:1997. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 60747-5-3:1997/AMD1:2002 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

NORME CEI

INTERNATIONALE IEC

60747-5-3

INTERNATIONAL

STANDARD

AMENDEMENT 1

AMENDMENT 1

2002-03

Amendement 1

Dispositifs discrets à semiconducteurs

et circuits intégrés –

Partie 5-3:

Dispositifs optoélectroniques –

Méthodes de mesure

Amendment 1

Discrete semiconductor devices

and integrated circuits –

Part 5-3:

Optoelectronic devices –

Measuring methods

IEC 2002 Droits de reproduction réservés Copyright - all rights reserved

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland

Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: inmail@iec.ch Web: www.iec.ch

CODE PRIX

M

Commission Electrotechnique Internationale

PRICE CODE

International Electrotechnical Commission

Международная Электротехническая Комиссия

Pour prix, voir catalogue en vigueur

For price, see current catalogue

– 2 – 60747-5-3 Amend. 1 CEI:2002

AVANT-PROPOS

Le présent amendement a été établi par le sous-comité 47E: Dispositifs discrets à

semiconducteurs, du comité d'études 47 de la CEI: Dispositifs à semiconducteurs.

Le texte de cet amendement est issu des documents suivants:

FDIS Rapport de vote

47E/210/FDIS 47E/215/RVD

Le rapport de vote indiqué dans le tableau ci-dessus donne toute information sur le vote

ayant abouti à l'approbation de cet amendement.

Le comité a décidé que le contenu de la publication de base et de ses amendements ne sera

pas modifié avant 2004. A cette date, la publication sera

• reconduite;

• supprimée;

• remplacée par une édition révisée, ou

• amendée.

_____________

Page 56

Ajouter les nouveaux paragraphes 5.8 et 5.15.2 suivants:

5.8 Courant de crête à l'état bloqué (I )

DRM

a) Objet

Mesurer le courant de fuite direct entre les bornes de sortie à l'état bloqué dans des

conditions spécifiées.

60747-5-3 Amend. 1 IEC:2002 – 3 –

FOREWORD

This amendment has been prepared by subcommittee 47E: Discrete semiconductor devices,

of IEC technical committee 47: Semiconductor devices.

The text of this amendment is based on the following documents:

FDIS Report on voting

47E/210/FDIS 47E/215/RVD

Full information on the voting for the approval of this amendment can be found in the report

on voting indicated in the above table.

The committee has decided that the contents of the base publication and its amendments will

remain unchanged until 2004. At this date, the publication will be

• reconfirmed;

• withdrawn;

• replaced by a revised edition, or

• amended.

____________

Page 57

Add the following new subclauses 5.8 to 5.15.2:

5.8 Peak off-state current (I )

DRM

a) Purpose

To measure the forward leakage current between the output terminals in off-state under

specified conditions.

– 4 – 60747-5-3 Amend. 1 CEI:2002

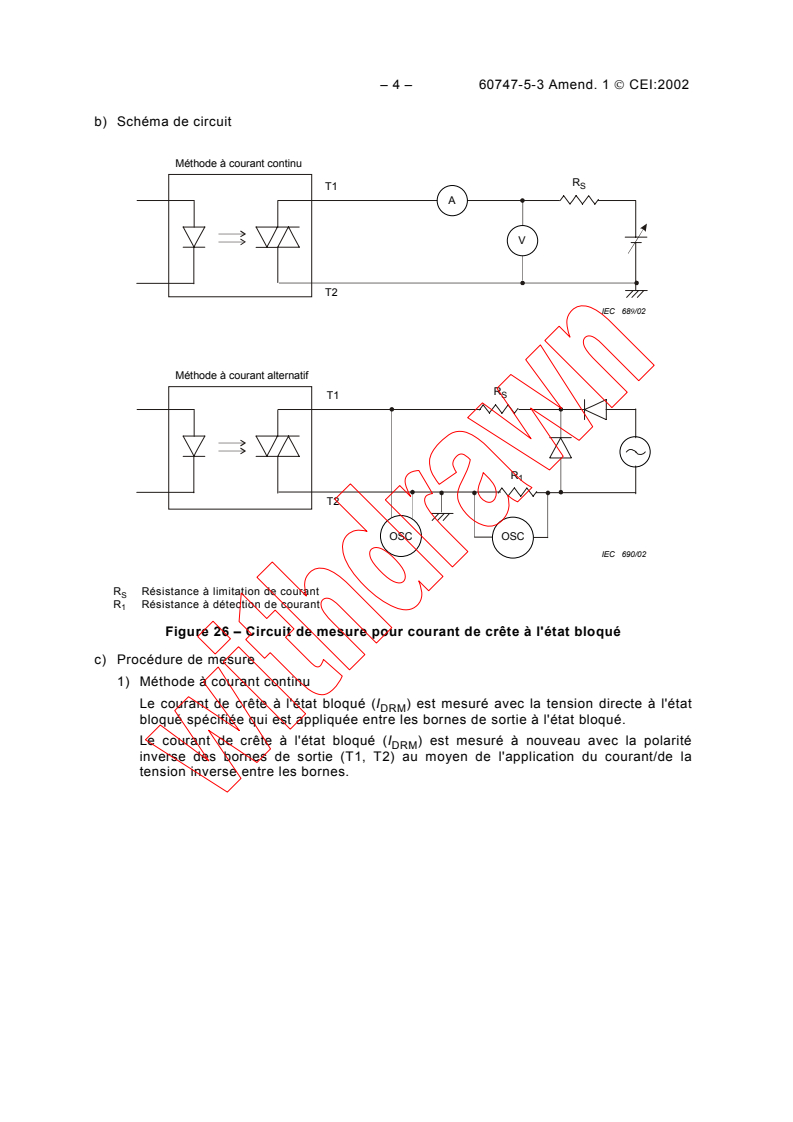

b) Schéma de circuit

Méthode à courant continu

R

S

T1

A

V

T2

IEC 689/02

Méthode à courant alternatif

R

S

T1

R

T2

OSC OSC

IEC 690/02

R Résistance à limitation de courant

S

R

Résistance à détection de courant

Figure 26 – Circuit de mesure pour courant de crête à l'état bloqué

c) Procédure de mesure

1) Méthode à courant continu

Le courant de crête à l'état bloqué (I ) est mesuré avec la tension directe à l'état

DRM

bloqué spécifiée qui est appliquée entre les bornes de sortie à l'état bloqué.

Le courant de crête à l'état bloqué (I ) est mesuré à nouveau avec la polarité

DRM

inverse des bornes de sortie (T1, T2) au moyen de l'application du courant/de la

tension inverse entre les bornes.

60747-5-3 Amend. 1 IEC:2002 – 5 –

b) Circuit diagram

DC method

R

S

T1

A

V

T2

IEC 689/02

AC method

R

S

T1

R

T2

OSC OSC

IEC 690/02

R Current limiting resistor

S

R Current detecting resistor

Figure 26 – Measurement circuit for peak off-state current

c) Measurement procedure

1) DC method

The peak off-state current (I ) is measured with the specified forward off-state

DRM

voltage which is applied between the output terminals in off-state.

The peak off-state current (I ) is measured again with inverted polarity of the output

DRM

terminals (T1, T2) by applying the reverse voltage/current between the terminals.

– 6 – 60747-5-3 Amend. 1 CEI:2002

2) Méthode à courant alternatif

Le courant de crête à l'état bloqué (I ) est mesuré à la tension de crête à l'état

DRM

bloqué spécifiée avec la tension à courant alternatif à rectification à simple alternance

avec la fréquence de ligne à courant alternatif commerciale, qui est appliquée entre

les bornes de sortie à l'état bloqué.

Le courant de crête à l'état bloqué (I ) est mesuré à nouveau avec la polarité

DRM

inverse des bornes de sortie (T1, T2) au moyen de l'application du courant/de la

tension inverse entre les bornes.

Tension

Tension spécifiée

de crête à l'état bloqué

Temps

Courant

Courant de crête

à l'état bloqué

Temps

IEC 691/02

Figure 27 – Formes d'ondes de la tension et du courant de crête à l'état bloqué

d) Prescriptions

1) La méthode de mesure du courant de crête à l'état bloqué utilise deux polarités de

tension forcée (T1→T2 et T2→T1).

2) Dans le cas de la méthode à courant continu, il convient que le taux de balayage de

la tension continue appliquée entre les bornes de sortie (T1, T2) ne dépasse pas le

taux critique d'augmentation de la tension à l'état bloqué (dV/dt).

Dans le cas de la méthode à courant alternatif, il convient que le taux de variation

(dV/dt) de la tension sinusoïdale appliquée entre les bornes de sortie (T1, T2) ne

dépasse pas le taux critique d'augmentation de la tension à l'état bloqué (dV/dt).

e) Conditions spécifiées

1) Tension de crête à l'état bloqué (V )

DRM

2) Température ambiante (T ).

amb

5.9 Tension de crête à l'état passant (V )

TM

a) Objet

Mesurer la tension de crête à l'état passant entre les bornes de sortie à l'état passant

dans des conditions spécifiées, lorsque le courant spécifié à l'état passant est appliqué

entre les bornes de sortie à l'état passant.

60747-5-3 Amend. 1 IEC:2002 – 7 –

2) AC method

The peak off-state current (I ) is measured at the specified peak off-state voltage

DRM

with the half-wave-rectified a.c. voltage with commercial a.c. line frequency, which is

applied between the output terminals in off-state.

The peak off-state current (I ) is measured again with inverted polarity of the output

DRM

terminals (T1, T2) by applying the reverse voltage/current between the terminals.

Voltage

Specified peak

off-state voltage

Time

Current

Peak off-state

current

Time

IEC 691/02

Figure 27 – Waveforms of the peak off-state voltage and current

d) Requirements

1) The measurement method of the peak off-state current uses two forced-voltage

polarities (T1→T2 and T2→T1).

2) In the case of the d.c. method, the slew rate of the applied d.c. voltage between the

output terminals (T1, T2) should not exceed the critical rate of rise of the off-state

voltage (dV/dt).

In the case of the a.c. method, the rate of change (dV/dt) of the applied sine-wave-

voltage between the output terminals (T1, T2) should not exceed the critical rate of

rise of the off-state voltage (dV/dt).

e) Specified conditions

1) Peak off-state voltage (V )

DRM

2) Ambient temperature (T ).

amb

5.9 Peak on-state voltage (V )

TM

a) Purpose

To measure the peak on-state voltage between the output terminals in on-state under

specified conditions, when the specified on-state current is applied between the output

terminals in on-state.

– 8 – 60747-5-3 Amend. 1 CEI:2002

b) Schéma de circuit

Méthode à courant continu

I

R F

S1

R

S2

T1

A

A

V

T2

IEC 692/02

Méthode à courant alternatif

I

F

D

R

2 R

S1

S2

T1

A

R D

2 1

R

T2

OSC OSC

IEC 693/02

R , R Résistances à limitation de courant

S1 S2

R Résistance à détection de courant

R Résistance destinée à empêcher le phototriaque d'être hors tension

D Diode destinée à diminuer la partie du courant continu dans la ligne électrique

NOTE Il convient que R soit sélectionnée de façon approximative pour régler la tension entre les bornes,

qui est causée par le courant de fuite à travers D , à presque zéro volt.

Figure 28 – Circuit de mesure pour courant de crête à l'état passant

c) Procédure de mesure

1) Méthode à courant continu

Le courant direct d'entrée spécifié (I ) est appliqué pour l'établissement de la sortie.

F

Par la suite, le courant spécifié à l'état passant est appliqué entre les bornes de

sortie.

On mesure la tension entre les bornes de sortie (tension de crête à l'état passant

(V )). La tension entre les bornes de sortie est mesurée à nouveau avec la polarité

TM

inversée des bornes de sortie (T1, T2) au moyen de l'application de la tension/du

courant inverse entre les bornes.

Une source de courant constante peut être utilisée à la place d'une source de tension

constante du côté de l'entrée.

2) Méthode à courant alternatif

Le courant direct d'entrée spécifié (I ) est appliqué pour l'établissement de la sortie.

F

Par la suite, la tension à courant alternatif à rectification à simple alternance avec la

fréquence de ligne à courant alternatif commerciale est appliquée entre les bornes de

sortie. On mesure la tension entre les bornes de sortie (tension de crête à l'état

passant (V )) au courant de crête à l'état passant spécifié.

TM

60747-5-3 Amend. 1 IEC:2002 – 9 –

b) Circuit diagram

DC method

I

R F

S1

R

S2

T1

A

A

V

T2

IEC 692/02

AC method

I

F

D

R

2 R

S1

S2

T1

A

R D

R

T2

OSC OSC

IEC 693/02

R , R Current limiting resistors

S1 S2

R Current detecting resistor

R Resistor to prevent the phototriac from being off-voltage

D Diode for decreasing d.c. current part in power line

NOTE R should be selected approximately to adjust the voltage between the terminals, which is caused by the

leakage current through D , to nearly zero volt.

Figure 28 – Measurement circuit for peak on-state voltage

c) Measurement procedure

1) DC method

The specified input forward current (I ) is applied to turn on the output, after which

F

the specified on-state current is applied between the output terminals.

The voltage between the output terminals (peak on-state voltage (V )) is measured.

TM

The voltage between the output terminals is measured again with inverted polarity of

the output terminals (T1, T2) by applying the reverse voltage/current between the

terminals.

A constant current source may be used instead of a constant voltage source on the

input side.

2) AC method

The specified input forward current (I ) is applied to turn on the output, after which

F

the half-wave-rectified a.c. voltage with commercial a.c. line frequency is applied

between the output terminals. The voltage between the output terminals (peak on-

state voltage (V )) is measured at the specified peak on-state current.

TM

– 10 – 60747-5-3 Amend. 1 CEI:2002

La tension entre les bornes de sortie est mesurée à nouveau avec la polarité inversée

des bornes de sortie (T1, T2) au moyen de l'application de la tension/du courant

inverse entre les bornes.

Une source de courant constant peut être utilisée à la place d'une source de tension

constante du côté de l'entrée.

Tension

Tension de crête

à l'état passant

Temps

Courant

Courant spécifié de crête

à l'état passant

Temps

IEC 694/02

Figure 29 – Formes d'ondes de la tension et du courant de crête à l'état passant

d) Prescriptions

La méthode de mesure de la tension de crête à l'état passant utilise deux polarités de

tension forcée (T1→T2 et T2→T1).

e) Conditions spécifiées

1) Courant de crête à l'état passant (I )

TM

2) Courant direct d'entrée (I )

F

3) Température ambiante (T ).

amb

5.10 Courant continu à l'état bloqué (I )

BD

a) Objet

Mesurer le courant de fuite entre les bornes de sortie à l'état bloqué dans des conditions

spécifiées.

b) Schéma de circuit

R

S

T1

A

V

T2

IEC 695/02

R Résistance à limitation de courant

S

Figure 30 – Circuit de mesure pour courant continu à l'état bloqué

60747-5-3 Amend. 1 IEC:2002 – 11 –

The voltage between the output terminals is measured again with inverted polarity of

the output terminals (T1, T2) by applying the reverse voltage/current between the

terminals.

A constant current source may be used instead of a constant voltage source on the

input side.

Voltage

Peak on-state

voltage

Time

Current

Specified peak on-state

current

Time

IEC 694/02

Figure 29 – Waveforms of the peak on-state voltage and current

d) Requirements

The measurement method of the peak on-state voltage uses two forced-voltage polarities

(T1→T2 and T2→T1).

e) Specified conditions

1) Peak on-state current (I )

TM

2) Input forward current (I )

F

3) Ambient temperature (T ).

amb

5.10 DC off-state current (I )

BD

a) Purpose

To measure the leakage current between the output terminals in off-state under specified

conditions.

b) Circuit diagram

R

S

T1

A

V

T2

IEC 695/02

R Current limiting resistor

S

Figure 30 – Measurement circuit for d.c. off-state current

– 12 – 60747-5-3 Amend. 1 CEI:2002

c) Procédure de mesure

La tension continue à l'état bloqué spécifiée est appliquée entre les bornes de sortie à

l'état bloqué. Le courant de fuite est mesuré à nouveau avec la polarité inversée des

bornes de sortie (T1, T2) au moyen de l'application du courant/de la tension inverse entre

les bornes.

d) Prescriptions

1) La méthode de mesure du courant continu à l'état bloqué utilise deux polarités de

tension forcée (T1→T2 et T2→T1).

2) Il convient que le taux de balayage de la tension continue appliquée entre les bornes

de sortie (T1, T2) ne dépasse pas le taux critique d'augmentation de tension à l'état

bloqué (dV/dt).

e) Conditions spécifiées

1) Tension continue à l'état bloqué (V )

BD

2) Température ambiante (T ).

amb

5.11 Tension continue à l'état passant (V )

T

a) Objet

Mesurer la tension continue entre les bornes de sortie à l'état passant dans des

conditions spécifiées, lorsque le courant direct spécifié est appliqué entre les bornes de

sortie à l'état passant.

b) Schéma de circuit

I

F

R

R

S1 S2

T1

A

A

V

T2

IEC 696/02

R , R Résistances à limitation de courant

S1 S2

Figure 31 – Circuit de mesure pour courant continu à l'état passant

c) Procédure de mesure

Le courant direct d'entrée spécifié (I ) est appliqué pour l'établissement de la sortie. Par

F

la suite, le courant continu spécifié à l'état passant est appliqué entre les bornes de

sortie.

On mesure la tension entre les bornes de sortie (tension continue à l'état passant (V )).

T

La tension entre les bornes de sortie est mesurée à nouveau avec la polarité inversée

des bornes de sortie (T1, T2) au moyen de l'application de la tension/du courant inverse

entre les bornes.

Une source de courant constant peut être utilisée à la place d'une source de tension

constante du côté de l'entrée.

d) Prescriptions

La méthode de mesure de la tension continue à l'état passant utilise deux polarités de

tension forcée (T1→T2 et T2→T1).

60747-5-3 Amend. 1 IEC:2002 – 13 –

c) Measurement procedure

The specified d.c. off-state voltage is applied between the output terminals in off-state.

The leakage current is measured again with inverted polarity of the output terminals (T1,

T2) by applying the reverse voltage/current between the terminals.

d) Requirements

1) The measurement method of the d.c. off-state current uses two forced-voltage

polarities (T1→T2 and T2→T1).

2) The slew rate of the applied d.c. voltage between the output terminals (T1, T2) should

not exceed the critical rate of rise of the off-state voltage (dV/dt).

e) Specified conditions

1) DC off-state voltage (V )

BD

2) Ambient temperature (T ).

amb

5.11 DC on-state voltage (V )

T

a) Purpose

To measure the d.c. voltage between the output terminals in on-state under specified

conditions, when the specified forward current is applied between the output terminals in

on-state.

b) Circuit diagram

I

F

R

R

S1 S2

T1

A

A

V

T2

IEC 696/02

R , R Current limiting resistors

S1 S2

Figure 31 – Measurement circuit for d.c. on-state voltage

c) Measurement procedure

The specified input forward current (I ) is applied to turn on the output, after which the

F

specified d.c. on-state current is applied between the output terminals.

The voltage between the output terminals (d.c. on-state voltage (V )) is measured. The

T

voltage between the output terminals is measured again with inverted polarity of the output

terminals (T1, T2) by means of applying the reverse voltage/current between the terminals.

A constant current source may be used instead of a constant voltage source on the input

side.

d) Requirements

The measurement method of the d.c. on-state voltage uses two forced-voltage polarities

(T1→T2 and T2→T1).

– 14 – 60747-5-3 Amend. 1 CEI:2002

e) Conditions spécifiées

1) Courant continu à l'état passant (I )

T

2) Courant direct d'entrée (I )

F

3) Température ambiante (T ).

amb

5.12 Courant de maintien (I )

H

a) Objet

Mesurer le courant minimal en sortie à l'état passant pour maintenir l'état passant dans

des conditions spécifiées.

b) Schéma de circuit

R S S R

S1 1 2 S2

T1

A

T2

IEC 697/02

R , R Résistances à limitation de courant

S1 S2

S , S Interrupteurs

1 2

Figure 32 – Circuit de mesure pour courant de maintien

c) Procédure de mesure

Le courant direct d'entrée est appliqué tandis que l'interrupteur S est fermé. Il convient

que le courant d'entrée dépasse le courant d'entrée d'amorçage (I ) pour maintenir la

FT

sortie en marche.

Au même moment, un courant à l'état passant suffisant est appliqué tandis que

l'interrupteur S est fermé. Alors l'interrupteur S est ouvert et il convient de maintenir la

2 1

sortie en marche. Le courant à l'état passant est diminué graduellement en augmentant

la résistance de limitation du courant R .

S2

Le courant à l'état passant (courant de maintien (I )) à travers les bornes de sortie est

H

mesuré comme le courant au-dessous duquel l'état passant ne peut être maintenu,

comme le courant à l'état passant diminue au-dessous du courant à l'état bloqué.

Le courant à l'état passant entre les bornes de sortie est mesuré à nouveau avec la

polarité inversée des bornes de sortie (T1, T2) au moyen de l'application de la tension/du

courant inverse entre les bornes.

Une source de courant constant peut être utilisée à la place d'une source de tension

constante du côté de l'entrée.

d) Prescriptions

La méthode de mesure du courant de maintien utilise deux polarités de tension forcée

(T1→T2 et T2→T1).

e) Condition spécifiée

Température am

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...