IEC 60749-21:2004

(Main)Semiconductor devices - Mechanical and climatic test methods - Part 21: Solderability

Semiconductor devices - Mechanical and climatic test methods - Part 21: Solderability

Establishes a standard procedure for determining the solderability of device package terminations that are intended to be joined to another surface using tin-lead or lead-free solder for the attachment. Provides a procedure for 'dip and look' solderability testing of through hole, axial and surface mount devices as well as an optional procedure for a board mounting solderability test for SMDs for the purpose of allowing simulation of the soldering process to be used in the device application.

Dispositifs à semiconducteurs - Méthodes d'essais mécaniques et climatiques - Partie 21: Brasabilité

L'objet de cette méthode d'essai est de fournir un moyen pour déterminer la brasabilité des sorties des boîtiers de dispositifs qui sont destinées à être fixées sur une autre surface en utilisant de la brasure étain-plomb ou sans-plomb pour réaliser cette fixation. Cette méthode d'essai décrit une procédure pour les essais de brasabilité par "immersion puis examen visuel" des dispositifs à montage en surface (CMS) par trous traversants, axial et en surface, ainsi qu'une procédure optionnelle d'essai de brasabilité pour des CMS pour montage en surface sur carte afin de permettre la simulation du processus de brasage devant être utilisé dans l'application du dispositif. La méthode d'essai fournit également des conditions optionnelles pour le vieillissement. Cet essai est considéré comme destructif sauf indication contraire dans la spécification applicable.

General Information

- Status

- Published

- Publication Date

- 14-Mar-2004

- Technical Committee

- TC 47 - Semiconductor devices

- Drafting Committee

- WG 2 - TC 47/WG 2

- Current Stage

- DELPUB - Deleted Publication

- Start Date

- 07-Apr-2011

- Completion Date

- 13-Feb-2026

Relations

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

- Effective Date

- 05-Sep-2023

Overview

IEC 60749-21:2004 defines a standardized test method for solderability of semiconductor device terminations intended for attachment with tin‑lead (SnPb) or lead‑free (Pb‑free) solder. The standard describes a primary “dip and look” solderability test for through‑hole, axial and surface‑mount devices (SMDs) and an optional simulated board‑mount reflow procedure for SMDs. It includes preconditioning (steam ageing or high‑temperature storage), test apparatus, materials (flux, solder, paste) and visual inspection requirements.

Key topics and technical requirements

- Scope & purpose: Determines wetting and solderability of package terminations; normally destructive unless otherwise specified.

- Test methods:

- Dip and look: Controlled immersion in a solder bath followed by visual inspection.

- Simulated board mounting (SMD): Solder‑paste stencil application and reflow to simulate assembly.

- Test apparatus:

- Solder bath - minimum depth 40 mm and volume 300 ml; temperature control ±5 °C.

- Dipping device - controlled immersion/emersion rates and dwell time.

- Optical inspection - microscope magnification 10×–20×.

- Reflow equipment - convection (preferred) or IR ovens for SMD reflow profiles.

- Materials:

- Flux - typically 25% colophony in 75% isopropanol; physical property limits specified.

- SnPb solder - composition and melting range specified (e.g., ~60 % Sn alloy solid ≈183 °C / liquid ≈188 °C).

- Pb‑free solder - typical Sn/Ag/Cu composition provided and solder‑paste particle size/viscosity guidance.

- Preconditioning: Steam ageing or high‑temperature storage options and conditions to simulate device exposure before testing.

- Inspection: Defined areas and acceptance criteria (visual “look”) for gull‑wing, J‑lead and other package types.

Applications and who uses it

IEC 60749-21 is used by:

- Semiconductor manufacturers for qualification of package terminations.

- Quality and reliability labs conducting incoming component or failure analysis.

- PCB assemblers and OEMs verifying component compatibility with SnPb or Pb‑free processes.

- Procurement and compliance teams requiring standardized solderability data for supplier evaluation.

Benefits include consistent, repeatable assessment of wetting performance, support for lead‑free migration, and simulation of board assembly processes.

Related standards

- IEC 60749‑15 / IEC 60749‑20 - related mechanical/thermal stress methods referenced for soldering thermal stress evaluation.

- IEC 60068 - general environmental test guidance (note: IEC 60749‑21 is semiconductor‑specific).

Keywords: IEC 60749-21, solderability testing, dip and look, SMD reflow, lead‑free solder, semiconductor devices, solder bath, steam ageing.

IEC 60749-21:2004 - Semiconductor devices - Mechanical and climatic test methods - Part 21: Solderability Released:3/15/2004 Isbn:2831874289

IEC 60749-21:2004 - Semiconductor devices - Mechanical and climatic test methods - Part 21: Solderability Released:3/15/2004 Isbn:2831882389

Frequently Asked Questions

IEC 60749-21:2004 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Semiconductor devices - Mechanical and climatic test methods - Part 21: Solderability". This standard covers: Establishes a standard procedure for determining the solderability of device package terminations that are intended to be joined to another surface using tin-lead or lead-free solder for the attachment. Provides a procedure for 'dip and look' solderability testing of through hole, axial and surface mount devices as well as an optional procedure for a board mounting solderability test for SMDs for the purpose of allowing simulation of the soldering process to be used in the device application.

Establishes a standard procedure for determining the solderability of device package terminations that are intended to be joined to another surface using tin-lead or lead-free solder for the attachment. Provides a procedure for 'dip and look' solderability testing of through hole, axial and surface mount devices as well as an optional procedure for a board mounting solderability test for SMDs for the purpose of allowing simulation of the soldering process to be used in the device application.

IEC 60749-21:2004 is classified under the following ICS (International Classification for Standards) categories: 31.080.01 - Semiconductor devices in general. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC 60749-21:2004 has the following relationships with other standards: It is inter standard links to IEC 60749:1996/AMD2:2001, IEC 60749:1996/AMD1:2000, IEC 60749:1996, IEC PAS 62173:2000, IEC 60749-21:2011. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

IEC 60749-21:2004 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

INTERNATIONAL IEC

STANDARD 60749-21

First edition

2004-03

Semiconductor devices –

Mechanical and climatic test methods –

Part 21:

Solderability

Reference number

Publication numbering

As from 1 January 1997 all IEC publications are issued with a designation in the

60000 series. For example, IEC 34-1 is now referred to as IEC 60034-1.

Consolidated editions

The IEC is now publishing consolidated versions of its publications. For example,

edition numbers 1.0, 1.1 and 1.2 refer, respectively, to the base publication, the

base publication incorporating amendment 1 and the base publication incorporating

amendments 1 and 2.

Further information on IEC publications

The technical content of IEC publications is kept under constant review by the IEC,

thus ensuring that the content reflects current technology. Information relating to

this publication, including its validity, is available in the IEC Catalogue of

publications (see below) in addition to new editions, amendments and corrigenda.

Information on the subjects under consideration and work in progress undertaken

by the technical committee which has prepared this publication, as well as the list

of publications issued, is also available from the following:

• IEC Web Site (www.iec.ch)

• Catalogue of IEC publications

The on-line catalogue on the IEC web site (www.iec.ch/searchpub) enables you to

search by a variety of criteria including text searches, technical committees

and date of publication. On-line information is also available on recently issued

publications, withdrawn and replaced publications, as well as corrigenda.

• IEC Just Published

This summary of recently issued publications (www.iec.ch/online_news/ justpub)

is also available by email. Please contact the Customer Service Centre (see

below) for further information.

• Customer Service Centre

If you have any questions regarding this publication or need further assistance,

please contact the Customer Service Centre:

Email: custserv@iec.ch

Tel: +41 22 919 02 11

Fax: +41 22 919 03 00

INTERNATIONAL IEC

STANDARD 60749-21

First edition

2004-03

Semiconductor devices –

Mechanical and climatic test methods –

Part 21:

Solderability

IEC 2004 Copyright - all rights reserved

No part of this publication may be reproduced or utilized in any form or by any means, electronic or

mechanical, including photocopying and microfilm, without permission in writing from the publisher.

International Electrotechnical Commission, 3, rue de Varembé, PO Box 131, CH-1211 Geneva 20, Switzerland

Telephone: +41 22 919 02 11 Telefax: +41 22 919 03 00 E-mail: inmail@iec.ch Web: www.iec.ch

PRICE CODE

Commission Electrotechnique Internationale R

International Electrotechnical Commission

МеждународнаяЭлектротехническаяКомиссия

For price, see current catalogue

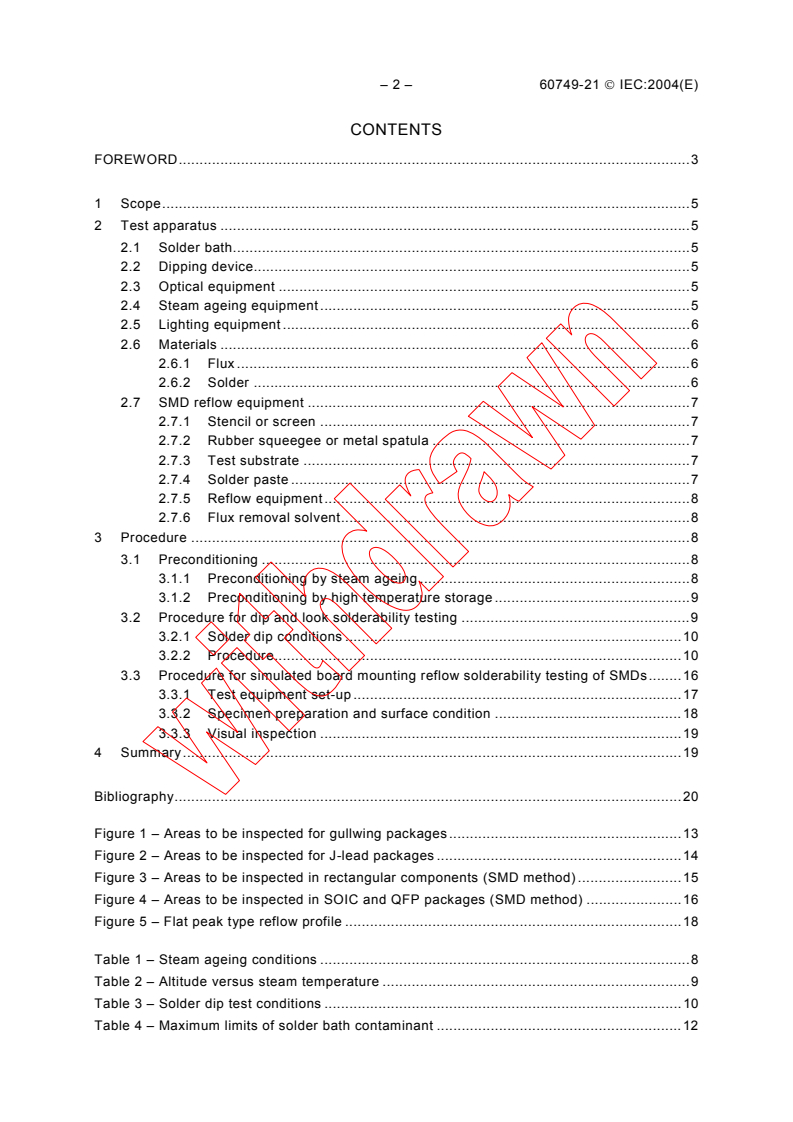

– 2 – 60749-21 IEC:2004(E)

CONTENTS

FOREWORD.3

1 Scope.5

2 Test apparatus.5

2.1 Solder bath.5

2.2 Dipping device.5

2.3 Optical equipment.5

2.4 Steam ageing equipment .5

2.5 Lighting equipment.6

2.6 Materials.6

2.6.1 Flux.6

2.6.2 Solder.6

2.7 SMD reflow equipment.7

2.7.1 Stencil or screen.7

2.7.2 Rubber squeegee or metal spatula .7

2.7.3 Test substrate.7

2.7.4 Solder paste.7

2.7.5 Reflow equipment.8

2.7.6 Flux removal solvent.8

3 Procedure.8

3.1 Preconditioning .8

3.1.1 Preconditioning by steam ageing .8

3.1.2 Preconditioning by high temperature storage .9

3.2 Procedure for dip and look solderability testing .9

3.2.1 Solder dip conditions.10

3.2.2 Procedure.10

3.3 Procedure for simulated board mounting reflow solderability testing of SMDs.16

3.3.1 Test equipment set-up.17

3.3.2 Specimen preparation and surface condition .18

3.3.3 Visual inspection.19

4 Summary.19

Bibliography.20

Figure 1 – Areas to be inspected for gullwing packages.13

Figure 2 – Areas to be inspected for J-lead packages .14

Figure 3 – Areas to be inspected in rectangular components (SMD method) .15

Figure 4 – Areas to be inspected in SOIC and QFP packages (SMD method) .16

Figure 5 – Flat peak type reflow profile .18

Table 1 – Steam ageing conditions .8

Table 2 – Altitude versus steam temperature .9

Table 3 – Solder dip test conditions .10

Table 4 – Maximum limits of solder bath contaminant .12

60749-21 IEC:2004(E) – 3 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

SEMICONDUCTOR DEVICES –

MECHANICAL AND CLIMATIC TEST METHODS –

Part 21: Solderability

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any

equipment declared to be in conformity with an IEC Publication.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 60749-21 has been prepared by IEC technical committee 47:

Semiconductor devices.

This standard cancels and replaces IEC/PAS 62173 published in 2000. This first edition

constitutes a technical revision.

This part of IEC 60749 series completes the full revision of IEC 60749 (1996).

The text of this standard is based on the following documents:

FDIS Report on voting

47/1741/FDIS 47/1749/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

– 4 – 60749-21 IEC:2004(E)

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

The committee has decided that the contents of this publication will remain unchanged until

2006. At this date, the publication will be

• reconfirmed;

• withdrawn;

• replaced by a revised edition, or

• amended.

60749-21 IEC:2004(E) – 5 –

SEMICONDUCTOR DEVICES –

MECHANICAL AND CLIMATIC TEST METHODS –

Part 21: Solderability

1 Scope

This part of IEC 60749 establishes a standard procedure for determining the solderability of

device package terminations that are intended to be joined to another surface using tin-lead

(SnPb) or lead-free (Pb-free) solder for the attachment.

This test method provides a procedure for ‘dip and look’ solderability testing of through hole,

axial and surface mount devices (SMDs) as well as an optional procedure for a board

mounting solderability test for SMDs for the purpose of allowing simulation of the soldering

process to be used in the device application. The test method also provides optional

conditions for ageing.

This test is considered destructive unless otherwise detailed in the relevant specification.

NOTE 1 This test method is in general accord with IEC 60068, but due to specific requirements of semi-

conductors, the following text is applied.

NOTE 2 This test method does not assess the effect of thermal stresses which may occur during the soldering

process. Reference should be made IEC 60749-15 or IEC 60749-20.

NOTE 3 This mechanical and climatic test method as it relates to solderability, is a complete rewrite of the test

contained in Subclause 2.1 of Chapter 2 of IEC 60749 (1996).

2 Test apparatus

This test method requires the following equipment.

2.1 Solder bath

The solder bath shall be not less than 40 mm in depth and not less than 300 ml in volume

such that it can contain at least 1 kg of solder. The apparatus shall be capable of maintaining

the solder at the specified temperature within ±5 °C.

2.2 Dipping device

A mechanical dipping device capable of controlling the rates of immersion and emersion of

the terminations and providing a dwell time (time of total immersion to the required depth) in

the solder bath as specified shall be used.

2.3 Optical equipment

An optical microscope capable of providing magnification inspection from 10× to 20× shall be

used.

2.4 Steam ageing equipment

A non-corrodible container and cover of sufficient size to allow the placement of specimens

inside the vessel shall be used. The specimens shall be placed such that the lowest portion of

the specimen is a minimum of 40 mm above the surface of the water. A suitable method of

supporting the specimens shall be improvised using non-contaminating material.

NOTE During steam ageing, the test devices should be located in a manner so as to prevent water (steam

condensate) from dripping on them.

– 6 – 60749-21 IEC:2004(E)

2.5 Lighting equipment

A lighting system shall be used that will provide a uniform, non-glare, non-directional

illumination of the specimen.

2.6 Materials

2.6.1 Flux

Unless otherwise detailed in the relevant specification, the flux shall consist of 25 % by weight

colophony in 75 % by weight of a 99,5 % (min.) by weight 2-propanol (issopropanol) solvent.

The specific gravity of the flux shall be maintained within the range of 0,838 to 0,913 at 25 °C.

The specification shall be as follows:

Colophony

Colour To WW colour specification or paler

Acid value (mg KOH/g colophony) 155 (minimum)

Softening point (ball and ring) 70 °C (minimum)

Flow point (Ubbelohde) 76 °C (minimum)

Ash 0,05 % (maximum).

Solubility A solution of the colophony in an equal part by weight

of 2-propanol (isopropanol) shall be clear, and after a

week at room temperature there shall be no sign of a

deposit.

2-propanol (isopropanol)

Purity Minimum 99,5 % 2-propanol (isopropanol) by weight

Acidity as acetic acid Maximum 0,002 % weight (other than carbon dioxide)

Non-volatile matter Maximum 2 mg per 100 ml.

2.6.2 Solder

2.6.2.1 Tin-lead

Unless otherwise detailed in the relevant specification, the solder specification for SnPb shall

be as follows:

Chemical composition

The composition in percentage by weight shall be as follows:

Tin 59 % to 61 %

Antimony 0,5 % maximum

Copper 0,1 % maximum

Arsenic 0,05 % maximum

Iron 0,02 % maximum

Lead the remainder.

The solder shall not contain such impurities as aluminium, zinc or cadmium in amounts which

will adversely affect the properties of the solder.

60749-21 IEC:2004(E) – 7 –

Melting temperature range

The melting temperature range of the 60 % solder is as follows:

Completely solid 183 °C

Completely liquid 188 °C.

2.6.2.2 Lead-free

Unless otherwise detailed in the relevant specification, the solder specification for Pb-free

shall be as follows:

The composition in percentage by weight shall be as follows:

Tin 95 % to 96,5 %

Silver 3 % to 4 %

Copper 0,5 % to 1 %.

2.7 SMD reflow equipment

2.7.1 Stencil or screen

A stencil or screen with pad geometry opening that is appropriate for the terminals being

tested. Unless otherwise agreed upon between vendor and user, nominal stencil thickness

should be 0,1 mm for terminals with less than 0,5 mm component lead pitch, 0,15 mm for a

component with lead pitch of 0,5 mm to 0,65 mm and 0,2 mm for a component with lead pitch

greater than 0,65 mm.

2.7.2 Rubber squeegee or metal spatula

Solder paste shall be applied on to the stencil or screen using a spatula for fine pitch or a

squeegee for standard pitch.

2.7.3 Test substrate

SMD specimens for simulated board mounting reflow solderability testing shall be evaluated

using a substrate.

NOTE 1 A ceramic (alumina 90 % – 98 %) may be used for all reflow requirements.

NOTE 2 A glass epoxy substrate may be used for all reflow requirements. The glass epoxy substrate should be

capable of withstanding the soldering temperature (e.g. it is not suitable for hot plate soldering).

NOTE 3 For visual inspection of the tested device terminations, the test substrate should be unmetallized (no

lands).

2.7.4 Solder paste

Unless otherwise specified, the composition of the solder paste shall be as follows:

2.7.4.1 Pb-containing paste

The solder composition shall be as specified in 2.6.2.

Unless otherwise specified in the relevant specification, the particle size of the solder powder

shall be 20 µm to 45 µm.

The composition of the flux shall be as specified in 2.6.1.

The viscosity range of the solder paste and method of measurement shall be detailed in the

relevant specification.

– 8 – 60749-21 IEC:2004(E)

2.7.4.2 Pb-free paste

The solder composition shall be as specified in 2.6.2.

The solder powder size shall be as follows:

− less than 1 %, larger than 53 μm;

− at least 90 %, between 22-53 μm;

− less than 10 %, smaller than 22 μm.

The shape of solder powder shall be spherical.

The flux to be used shall consist of 30 wt % of polymerization rosin (softening point,

approximately 95 °C), 30 wt % of dibasic acid degeneration rosin (softening point,

approximately 140 °C), 34,7 wt % of diethylene glycol monobutyl ether, 0,9 wt % of 1,3-

diphenylguanidine-HBr, 0,5 wt % of adipic acid (chlorine content less than 0,1 wt %) and

4 wt % of stiffening castor oil.

The solder paste to be used shall consist of 88 wt % of solder powder and 12 wt % of flux.

The viscosity range shall be (180 ± 5) Pa s.

NOTE Paste storage and shelf life should be in accordance with manufacturer’s specifications.

2.7.5 Reflow equipment

Convection reflow ovens (preferred) or infrared reflow ovens capable of reaching the reflow

temperature profile of the paste may be used.

2.7.6 Flux removal solvent

Material used for cleaning flux from leads and terminations shall be capable of removing

visible flux residues and meet local environmental regulations.

3 Procedure

3.1 Preconditioning

Preconditioning, also known as accelerated ageing, is an optional step which may be required

before solderability testing.

3.1.1 Preconditioning by steam ageing

Steam age preconditioning options are given in Table 1.

Table 1 – Steam ageing conditions

Exposure time

Condition

h ± 0,5

A 1

B 4

C 8

D 16

NOTE 1 Ageing may be interrupted once for 10 min maximum.

NOTE 2 PRECAUTION: Mounting should be such that water does not collect on the surface to be tested.

NOTE 3 Unless otherwise stated in the relevant specification, steam age precondition B should be used.

60749-21 IEC:2004(E) – 9 –

NOTE 4 Preconditioning in a moist environment in order to test the effects of moisture and soldering heat of

surface mount semiconductor packages is not part of this standard solderability test method.

...

IEC 60749-21

Edition 1.0 2004-03

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

Semiconductor devices – Mechanical and climatic test methods –

Part 21: Solderability

Dispositifs à semiconducteurs – Méthodes d’essais mécaniques et climatiques –

Partie 21: Brasabilité

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by

any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either IEC or

IEC's member National Committee in the country of the requester.

If you have any questions about IEC copyright or have an enquiry about obtaining additional rights to this publication,

please contact the address below or your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite

ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie

et les microfilms, sans l'accord écrit de la CEI ou du Comité national de la CEI du pays du demandeur.

Si vous avez des questions sur le copyright de la CEI ou si vous désirez obtenir des droits supplémentaires sur cette

publication, utilisez les coordonnées ci-après ou contactez le Comité national de la CEI de votre pays de résidence.

IEC Central Office

3, rue de Varembé

CH-1211 Geneva 20

Switzerland

Email: inmail@iec.ch

Web: www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

ƒ Catalogue of IEC publications: www.iec.ch/searchpub

The IEC on-line Catalogue enables you to search by a variety of criteria (reference number, text, technical committee,…).

It also gives information on projects, withdrawn and replaced publications.

ƒ IEC Just Published: www.iec.ch/online_news/justpub

Stay up to date on all new IEC publications. Just Published details twice a month all new publications released. Available

on-line and also by email.

ƒ Electropedia: www.electropedia.org

The world's leading online dictionary of electronic and electrical terms containing more than 20 000 terms and definitions

in English and French, with equivalent terms in additional languages. Also known as the International Electrotechnical

Vocabulary online.

ƒ Customer Service Centre: www.iec.ch/webstore/custserv

If you wish to give us your feedback on this publication or need further assistance, please visit the Customer Service

Centre FAQ or contact us:

Email: csc@iec.ch

Tel.: +41 22 919 02 11

Fax: +41 22 919 03 00

A propos de la CEI

La Commission Electrotechnique Internationale (CEI) est la première organisation mondiale qui élabore et publie des

normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications CEI

Le contenu technique des publications de la CEI est constamment revu. Veuillez vous assurer que vous possédez

l’édition la plus récente, un corrigendum ou amendement peut avoir été publié.

ƒ Catalogue des publications de la CEI: www.iec.ch/searchpub/cur_fut-f.htm

Le Catalogue en-ligne de la CEI vous permet d’effectuer des recherches en utilisant différents critères (numéro de référence,

texte, comité d’études,…). Il donne aussi des informations sur les projets et les publications retirées ou remplacées.

ƒ Just Published CEI: www.iec.ch/online_news/justpub

Restez informé sur les nouvelles publications de la CEI. Just Published détaille deux fois par mois les nouvelles

publications parues. Disponible en-ligne et aussi par email.

ƒ Electropedia: www.electropedia.org

Le premier dictionnaire en ligne au monde de termes électroniques et électriques. Il contient plus de 20 000 termes et

définitions en anglais et en français, ainsi que les termes équivalents dans les langues additionnelles. Egalement appelé

Vocabulaire Electrotechnique International en ligne.

ƒ Service Clients: www.iec.ch/webstore/custserv/custserv_entry-f.htm

Si vous désirez nous donner des commentaires sur cette publication ou si vous avez des questions, visitez le FAQ du

Service clients ou contactez-nous:

Email: csc@iec.ch

Tél.: +41 22 919 02 11

Fax: +41 22 919 03 00

IEC 60749-21

Edition 1.0 2004-03

INTERNATIONAL

STANDARD

NORME

INTERNATIONALE

Semiconductor devices – Mechanical and climatic test methods –

Part 21: Solderability

Dispositifs à semiconducteurs – Méthodes d’essais mécaniques et climatiques –

Partie 21: Brasabilité

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION

ELECTROTECHNIQUE

PRICE CODE

INTERNATIONALE

S

CODE PRIX

ICS 31.080 ISBN 2-8318-8238-9

– 2 – 60749-21 © CEI:2004

SOMMAIRE

AVANT-PROPOS.6

1 Domaine d’application .12

2 Appareillage d’essai .12

2.1 Bain de brasage .12

2.2 Dispositif d'immersion .12

2.3 Equipement optique.12

2.4 Equipement de vieillissement à la vapeur .14

2.5 Equipement d’éclairage .14

2.6 Matières .14

2.6.1 Flux .14

2.6.2 Brasure .14

2.7 Equipement de fusion pour CMS .16

2.7.1 Stencil ou écran .16

2.7.2 Raclette en caoutchouc ou spatule métallique .16

2.7.3 Substrat en céramique.16

2.7.4 Pâte de brasage .18

2.7.5 Equipement de fusion .18

2.7.6 Solvant pour le nettoyage du flux.18

3 Procédure .20

3.1 Préconditionnement.20

3.1.1 Procédure de vieillissement à la vapeur.20

3.1.2 Préconditionnement par stockage à haute température .22

3.2 Procédure pour les essais de brasabilité par immersion et examen visuel .22

3.2.1 Conditions d’immersion dans la brasure .22

3.2.2 Procédure.22

3.3 Procédure pour les essais simulés de brasabilité avec fusion pour le

montage sur carte à CMS.38

3.3.1 Montage de l’équipement d’essai.38

3.3.2 Préparation de l'éprouvette et condition de surface .40

3.3.3 Examen visuel .42

4 Résumé.42

Bibliographie.44

Figure 1 – Zones à contrôler pour les boîtiers en aile de mouette .30

Figure 2 – Zones à contrôler pour les boîtiers à sortie en J.32

Figure 3 – Zones à contrôler pour les composants rectangulaires (Méthode CMS).34

Figure 4 – Zones à contrôler pour les boîtiers SOEIC et QFP (Méthode CMS) .36

Figure 5 – Courbe de fusion pour les types à valeur maximale de température plate .40

60749-21 © IEC:2004 – 3 –

CONTENTS

FOREWORD.7

1 Scope.13

2 Test apparatus .13

2.1 Solder bath.13

2.2 Dipping device.13

2.3 Optical equipment .13

2.4 Steam ageing equipment .15

2.5 Lighting equipment .15

2.6 Materials .15

2.6.1 Flux .15

2.6.2 Solder .15

2.7 SMD reflow equipment .17

2.7.1 Stencil or screen .17

2.7.2 Rubber squeegee or metal spatula .17

2.7.3 Test substrate .17

2.7.4 Solder paste .19

2.7.5 Reflow equipment.19

2.7.6 Flux removal solvent.19

3 Procedure .21

3.1 Preconditioning .21

3.1.1 Preconditioning by steam ageing .21

3.1.2 Preconditioning by high temperature storage .23

3.2 Procedure for dip and look solderability testing .23

3.2.1 Solder dip conditions .23

3.2.2 Procedure.23

3.3 Procedure for simulated board mounting reflow solderability testing of SMDs.39

3.3.1 Test equipment set-up .39

3.3.2 Specimen preparation and surface condition .41

3.3.3 Visual inspection .43

4 Summary.43

Bibliography.45

Figure 1 – Areas to be inspected for gullwing packages.31

Figure 2 – Areas to be inspected for J-lead packages .33

Figure 3 – Areas to be inspected in rectangular components (SMD method) .35

Figure 4 – Areas to be inspected in SOIC and QFP packages (SMD method) .37

Figure 5 – Flat peak type reflow profile .41

– 4 – 60749-21 © CEI:2004

Tableau 1 – Conditions de vieillissement à la vapeur .20

Tableau 2 – Altitude en fonction de la température de vapeur.20

Tableau 3 – Conditions d’essai d’immersion dans la brasure .22

Tableau 4 – Limites maximales de contaminant de bain de brasage .28

60749-21 © IEC:2004 – 5 –

Table 1 – Steam ageing conditions .21

Table 2 – Altitude versus steam temperature .21

Table 3 – Solder dip test conditions .23

Table 4 – Maximum limits of solder bath contaminant .29

– 6 – 60749-21 © CEI:2004

COMMISSION ÉLECTROTECHNIQUE INTERNATIONALE

____________

DISPOSITIFS À SEMICONDUCTEURS –

MÉTHODES D’ESSAIS MÉCANIQUES ET CLIMATIQUES –

Partie 21: Brasabilité

AVANT-PROPOS

1) La Commission Electrotechnique Internationale (CEI) est une organisation mondiale de normalisation

composée de l'ensemble des comités électrotechniques nationaux (Comités nationaux de la CEI). La CEI a

pour objet de favoriser la coopération internationale pour toutes les questions de normalisation dans les

domaines de l'électricité et de l'électronique. A cet effet, la CEI – entre autres activités – publie des Normes

internationales, des Spécifications techniques, des Rapports techniques, des Spécifications accessibles au

public (PAS) et des Guides (ci-après dénommés "Publication(s) de la CEI"). Leur élaboration est confiée à des

comités d'études, aux travaux desquels tout Comité national intéressé par le sujet traité peut participer. Les

organisations internationales, gouvernementales et non gouvernementales, en liaison avec la CEI, participent

également aux travaux. La CEI collabore étroitement avec l'Organisation Internationale de Normalisation (ISO),

selon des conditions fixées par accord entre les deux organisations.

2) Les décisions ou accords officiels de la CEI concernant les questions techniques représentent, dans la mesure

du possible, un accord international sur les sujets étudiés, étant donné que les Comités nationaux de la CEI

intéressés sont représentés dans chaque comité d’études.

3) Les Publications de la CEI se présentent sous la forme de recommandations internationales et sont agréées

comme telles par les Comités nationaux de la CEI. Tous les efforts raisonnables sont entrepris afin que la CEI

s'assure de l'exactitude du contenu technique de ses publications; la CEI ne peut pas être tenue responsable

de l'éventuelle mauvaise utilisation ou interprétation qui en est faite par un quelconque utilisateur final.

4) Dans le but d'encourager l'uniformité internationale, les Comités nationaux de la CEI s'engagent, dans toute la

mesure possible, à appliquer de façon transparente les Publications de la CEI dans leurs publications

nationales et régionales. Toutes divergences entre toutes Publications de la CEI et toutes publications

nationales ou régionales correspondantes doivent être indiquées en termes clairs dans ces dernières.

5) La CEI n’a prévu aucune procédure de marquage valant indication d’approbation et n'engage pas sa

responsabilité pour les équipements déclarés conformes à une de ses Publications.

6) Tous les utilisateurs doivent s'assurer qu'ils sont en possession de la dernière édition de cette publication.

7) Aucune responsabilité ne doit être imputée à la CEI, à ses administrateurs, employés, auxiliaires ou

mandataires, y compris ses experts particuliers et les membres de ses comités d'études et des Comités

nationaux de la CEI, pour tout préjudice causé en cas de dommages corporels et matériels, ou de tout autre

dommage de quelque nature que ce soit, directe ou indirecte, ou pour supporter les coûts (y compris les frais

de justice) et les dépenses découlant de la publication ou de l'utilisation de cette Publication de la CEI ou de

toute autre Publication de la CEI, ou au crédit qui lui est accordé.

8) L'attention est attirée sur les références normatives citées dans cette publication. L'utilisation de publications

référencées est obligatoire pour une application correcte de la présente publication.

9) L’attention est attirée sur le fait que certains des éléments de la présente Publication de la CEI peuvent faire

l’objet de droits de propriété intellectuelle ou de droits analogues. La CEI ne saurait être tenue pour

responsable de ne pas avoir identifié de tels droits de propriété et de ne pas avoir signalé leur existence.

La Norme internationale CEI 60749-21 a été établie par le comité d'études 47 de la CEI:

Dispositifs à semiconducteurs.

Cette norme annule et remplace la IEC/PAS 62173 publiée en 2000. Cette première édition

constitue une révision technique.

Cette partie de la série CEI 60749 termine la révision complète de la CEI 60749 (1996).

Cette version bilingue, publiée en 2005-10, correspond à la version anglaise.

Le texte anglais de cette norme est issu des documents 47/1741/FDIS et 47/1749/RVD.

60749-21 © IEC:2004 – 7 –

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

SEMICONDUCTOR DEVICES –

MECHANICAL AND CLIMATIC TEST METHODS –

Part 21: Solderability

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any

equipment declared to be in conformity with an IEC Publication.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 60749-21 has been prepared by IEC technical committee 47:

Semiconductor devices.

This standard cancels and replaces IEC/PAS 62173 published in 2000. This first edition

constitutes a technical revision.

This part of the IEC 60749 series completes the full revision of IEC 60749 (1996).

This bilingual version, published in 2005-10, corresponds to the English version.

– 8 – 60749-21 © CEI:2004

Le rapport de vote 47/1749/RVD donne toute information sur le vote ayant abouti à

l’approbation de cette norme.

La version française de cette norme n’a pas été soumise au vote.

Cette publication a été rédigée selon les Directives ISO/CEI, Partie 2.

La CEI 60749 comprend les parties suivantes sous le titre général Dispositifs à

semiconducteurs – Méthodes d’essais mécaniques et climatiques:

Partie 1: Généralités

Partie 2: Basse pression atmosphérique

Partie 3 : Examen visuel externe

Partie 4: Essai continu fortement accéléré de contrainte de chaleur humide (HAST)

Partie 5: Essai continu de durée de vie sous température et humidité avec polarisation

Partie 6: Stockage à haute température

Partie 7: Mesure de la teneur en humidité interne et analyse des autres gaz résiduels

Partie 8: Etanchéité

Partie 9: Permanence du marquage

Partie 10: Chocs mécaniques

Partie 11: Variations rapides de température - Méthode des deux bains

Partie 12: Vibrations, fréquences variables

Partie 13 : Atmosphère saline

Partie 14: Robustesse des sorties (integrité des connexions)

Partie 15: Résistance à la température de soudage pour dispositifs par trous traversants

Partie 16: Détection de bruit d'impact de particules (PIND)

Partie 17: Irradiation aux neutrons

Partie 18: Rayonnements ionisants (dose totale)

Partie 19: Résistance de la pastille au cisaillement

Partie 20: Résistance des CMS à boîtier plastique à l'effet combiné de l'humidité et de la

chaleur de soudage

Partie 21: Brasabilité

Partie 22: Robustesse des contacts soudés

Partie 23 : Durée de vie en fonctionnement à haute température

Partie 24: Résistance à l’humidité accélérée - HAST sans polarization

Partie 25: Cycles de température

Partie 26: Essai de sensibilité aux décharges électrostatiques (DES) - Modèle du corps

humain (HBM)

Partie 27: Essai de sensibilité aux décharges électrostatiques (DES) - Modèle de machine

(MM)

Partie 28: Essai de sensibilité aux décharges électrostatiques (DES) – Modèle de dispositif

chargé (CDM)

———————

A publier

60749-21 © IEC:2004 – 9 –

The text of this standard is based on the following documents:

FDIS Report on voting

47/1741/FDIS 47/1749/RVD

Full information on the voting for the approval of this standard can be found in the report on

voting indicated in the above table.

The French version of this standard has not been voted upon.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

IEC 60749 consists of the following parts, under the general title Semiconductor devices –

Mechanical and climatic test methods:

Part 1: General

Part 2: Low air pressure

Part 3: External visual inspection

Part 4: Damp heat, steady state, highly accelerated stress test (HAST)

Part 5: Steady-state temperature humidity bias life test

Part 6: Storage at high temperature

Part 7: Internal moisture content measurement and the analysis of other residual gases

Part 8: Sealing

Part 9: Permanence of marking

Part 10: Mechanical shock

Part 11: Rapid change of temperature – Two-fluid-bath method

Part 12: Vibration, variable frequency

Part 13: Salt atmosphere

Part 14: Robustness of terminations (lead integrity)

Part 15: Resistance to soldering temperature for through-hole mounted devices

Part 16: Particle impact noise detection (PIND)

Part 17: Neutron irradiation

Part 18: Ionizing radiation (total dose)

Part 19: Die shear strength

Part 20: Resistance of plastic-encapsulated SMDs to the combined effect of moisture and

soldering heat

Part 21: Solderability

Part 22: Bond strength

Part 23: High temperature operating life

Part 24: Accelerated moisture resistance – Unbiased HAST

Part 25: Temperature cycling

Part 26: Electrostatic discharge (ESD) sensitivity testing – Human body model (HBM)

Part 27: Electrostatic discharge (ESD) sensitivity testing – Machine model (MM)

Part 28: Electrostatic discharge (ESD) sensitivity testing – Charged device model (CDM)

———————

To be published

– 10 – 60749-21 © CEI:2004

Partie 29: Essai de verrouillage

Partie 30: Préconditionnement des composants pour montage en surface non hermétiques

avant les essais de fiabilité

Partie 31: Inflammabilité des dispositifs à encapsulation plastique (cas d'une cause interne

d'inflammation)

Partie 32: Inflammabilité des dispositifs à encapsulation plastique (cas d'une cause

extérieure d'inflammation)

Partie 33: Résistance à l'humidité accélérée - autoclave sans polarisation

Partie 34: Cycles en puissance

Partie 35: Microscopie acoustique pour composants électroniques à boîtier plastique

Partie 36: Accélération constante

Le comité a décidé que le contenu de cette publication ne sera pas modifié avant la date de

maintenance indiquée sur le site web de la CEI sous «http://webstore.iec.ch» dans les

données relatives à la publication recherchée. A cette date, la publication sera

• reconduite;

• supprimée;

• remplacée par une édition révisée, ou

• amendée.

———————

A publier

60749-21 © IEC:2004 – 11 –

Part 29: Latch-up test

Part 30: Preconditioning of non-hermetic surface mount devices prior to reliability testing

Part 31: Flammability of plastic-encapsulated devices (internally induced)

Part 32: Flammability of plastic-encapsulated devices (externally induced)

Part 33: Accelerated moisture resistance – Unbiased autoclave

Part 34: Power cycling

Part 35: Acoustic microscopy for plastic encapsulated electronic components

Part 36: Acceleration, steady state

The committee has decided that the contents of this publication will remain unchanged until

the maintenance result date indicated on the IEC web site under "http://webstore.iec.ch" in

the data related to the specific publication. At this date, the publication will be

• reconfirmed;

• withdrawn;

• replaced by a revised edition, or

• amended.

———————

To be published

– 12 – 60749-21 © CEI:2004

DISPOSITIFS À SEMICONDUCTEURS –

MÉTHODES D’ESSAIS MÉCANIQUES ET CLIMATIQUES –

Partie 21: Brasabilité

1 Domaine d’application

L’objet de cette méthode d’essai est de fournir un moyen pour déterminer la brasabilité des

sorties des boîtiers de dispositifs qui sont destinées à être fixées sur une autre surface en

utilisant de la brasure étain-plomb ou sans-plomb pour réaliser cette fixation.

Cette méthode d’essai décrit une procédure pour les essais de brasabilité par "immersion

puis examen visuel" des dispositifs à montage en surface (CMS) par trous traversants, axial

et en surface, ainsi qu'une procédure optionnelle d'essai de brasabilité pour des CMS pour

montage en surface sur carte afin de permettre la simulation du processus de brasage devant

être utilisé dans l’application du dispositif. La méthode d'essai fournit également des

conditions optionnelles pour le vieillissement.

Cet essai est considéré comme destructif sauf indication contraire dans la spécification

applicable.

NOTE 1 Cette méthode d’essai est en accord général avec la CEI 60068, mais c’est le texte ci-dessous qui

s’applique compte tenu des exigences spécifiques que présentent les semiconducteurs.

NOTE 2 Cette méthode d'essai ne prend pas en compte l'effet des contraintes thermiques qui peuvent se

produire pendant la procédure de brasure. Il convient de faire référence aux CEI 60749-15 ou 60749-20.

NOTE 3 Cette méthode d'essai climatique et mécanique se référant à la brasabilité constitue une refonte

complète de l'essai contenu dans la CEI 60749 (1996) Chapitre 2, Paragraphe 2.1.

2 Appareillage d’essai

Cette méthode d'essai nécessite l'équipement suivant.

2.1 Bain de brasage

Le bain de brasage doit avoir une profondeur d'au mois 40 mm et un volume d'au moins

300 ml pour contenir au moins 1 kg de brasure. L'appareillage doit être capable de maintenir

la brasure à la température spécifiée à ± 5 °C.

2.2 Dispositif d'immersion

Un dispositif mécanique d’immersion capable de contrôler les rythmes d’immersion et

émersion des sorties et d’offrir un temps de maintien (durée d’immersion totale à la

profondeur exigée) dans le bain de brasage comme spécifié doit être utilisé.

2.3 Equipement optique

Un microscope optique capable d’offrir un contrôle avec grossissement de 10x à 20x doit être

utilisé.

60749-21 © IEC:2004 – 13 –

SEMICONDUCTOR DEVICES –

MECHANICAL AND CLIMATIC TEST METHODS –

Part 21: Solderability

1 Scope

This part of IEC 60749 establishes a standard procedure for determining the solderability of

device package terminations that are intended to be joined to another surface using tin-lead

(SnPb) or lead-free (Pb-free) solder for the attachment.

This test method provides a procedure for ‘dip and look’ solderability testing of through hole,

axial and surface mount devices (SMDs) as well as an optional procedure for a board

mounting solderability test for SMDs for the purpose of allowing simulation of the soldering

process to be used in the device application. The test method also provides optional

conditions for ageing.

This test is considered destructive unless otherwise detailed in the relevant specification.

NOTE 1 This test method is in general accord with IEC 60068, but due to specific requirements of semi-

conductors, the following text is applied.

NOTE 2 This test method does not assess the effect of thermal stresses which may occur during the soldering

process. Reference should be made IEC 60749-15 or IEC 60749-20.

NOTE 3 This mechanical and climatic test method as it relates to solderability, is a complete rewrite of the test

contained in Subclause 2.1 of Chapter 2 of IEC 60749 (1996).

2 Test apparatus

This test method requires the following equipment.

2.1 Solder bath

The solder bath shall be not less than 40 mm in depth and not less than 300 ml in volume

such that it can contain at least 1 kg of solder. The apparatus shall be capable of maintaining

the solder at the specified temperature within ±5 °C.

2.2 Dipping device

A mechanical dipping device capable of controlling the rates of immersion and emersion of

the terminations and providing a dwell time (time of total immersion to the required depth) in

the solder bath as specified shall be used.

2.3 Optical equipment

An optical microscope capable of providing magnification inspection from 10× to 20× shall be

used.

– 14 – 60749-21 © CEI:2004

2.4 Equipement de vieillissement à la vapeur

On doit utiliser un conteneur insensible à la corrosion et un couvercle de taille suffisante pour

permettre le placement des éprouvettes à l’intérieur de la cuve. Les éprouvettes doivent être

placées de telle manière que leur partie la plus basse soit au minimum à 40 mm au-dessus de

la surface de l’eau. Une méthode adaptée pour maintenir les éprouvettes doit être improvisée

en utilisant une matière non contaminatrice.

NOTE Pendant le vieillissement à la vapeur, il convient que les dispositifs en essai soient situés de manière à

éviter que l'eau (vapeur condensée) s'égoutte sur eux.

2.5 Equipement d’éclairage

L’équipement d’éclairage à utiliser doit offrir un éclairement uniforme, non éblouissant, non

directionnel de l'éprouvette.

2.6 Matières

2.6.1 Flux

Sauf indication contraire dans la spécification applicable, le flux doit être composé en masse

de 25 % de colophane dans 75 % en masse de solvant de 2-propanol (isopropanol) à 99,5 %

(min.) en masse. La gravité spécifique du flux doit être maintenue dans la plage comprise

entre 0,838 et 0,913 à 25 °C. La spécification doit être la suivante:

Colophane

Couleur selon spécification de couleur WW ou plus pale

Indice d’acidité 155 (minimum)

(colophane mg KOH/g )

Point de ramollissement

70 °C (minimum)

(boule et anneau)

Point de d’écoulement

76 °C (minimum)

(selon Ubbelohde)

Cendres 0,05 % maximum

Solubilité une solution de colophane dans une proportion égale en

masse de 2-propanol (isopropanol) doit être claire, et,

après une semaine à température ambiante, il ne doit pas

y avoir de signe de dépôt.

2-propanol (isopropanol)

Pureté Minimum 99,5 % 2-propanol (isopropanol) en masse

Acidité comme acide acétique Maximum 0,002 % de la masse

(autre que dioxyde de carbone)

Matière non volatile Maximum 2 mg par 100 ml.

2.6.2 Brasure

2.6.2.1 Etain-plomb

Sauf indication contraire dans la spécification applicable, la spécification de brasure pour

SnPb doit être la suivante:

60749-21 © IEC:2004 – 15 –

2.4 Steam ageing equipment

A non-corrodible container and cover of sufficient size to allow the placement of specimens

inside the vessel shall be used. The specimens shall be placed such that the lowest portion of

the specimen is a minimum of 40 mm above the surface of the water. A suitable method of

supporting the specimens shall be improvised using non-contaminating material.

NOTE During steam ageing, the test devices should be located in a manner so as to prevent water (steam

condensate) from dripping on them.

2.5 Lighting equipment

A lighting system shall be used that will provide a uniform, non-glare, non-directional

illumination of the specimen.

2.6 Materials

2.6.1 Flux

Unless otherwise detailed in the relevant specification, the flux shall consist of 25 % by weight

colophony in 75 % by weight of a 99,5 % (min.) by weight 2-propanol (issopropanol) solvent.

The specific gravity of the flux shall be maintained within the range of 0,838 to 0,913 at 25 °C.

The specification shall be as follows:

Colophony

Colour To WW colour specification or paler

Acid value (mg KOH/g colophony) 155 (minimum)

Softening point (ball and ring) 70 °C (minimum)

Flow point (Ubbelohde) 76 °C (minimum)

Ash 0,05 % (maximum).

Solubility A solution of the colophony in an equal part by weight

of 2-propanol (isopropanol) shall be clear, and after a

week at room temperature there shall be no sign of a

deposit.

2-propanol (isopropanol)

Purity Minimum 99,5 % 2-propanol (isopropanol) by weight

Acidity as acetic acid Maximum 0,002 % weight (other than carbon dioxide)

Non-volatile matter Maximum 2 mg per 100 ml.

2.6.2 Solder

2.6.2.1 Tin-lead

Unless otherwise detailed in the relevant specification, the solder specification for SnPb shall

be as follows:

– 16 – 60749-21 © CEI:2004

Composition chimique

La composition en pourcentage en masse doit être la suivante:

Etain 59 % à 61 %

Antimoine 0,5 % maximum

Cuivre 0,1 % maximum

Arsenic 0,05 % maximum

Fer 0,02 % maximum

Plomb le reste

La brasure ne doit pas contenir d’impuretés telles que l'aluminium, le zinc ou le cadmium

dans des quantités qui nuisent à ses propriétés.

Plage de températures de fusion

La plage de températures de fusion de la brasure à 60 % est la suivante:

Complètement solide 183°C

Complètement liquide 188°C

2.6.2.2 Sans plomb

Sauf indication contraire dans la spécification applicable, la spécification de brasure pour le

sans Pb doit être la suivante:

La composition en pourcentage en masse doit être la suivante:

Etain 95 % à 96,5 %

Argent 3 % à 4 %

Cuivre 0,5 % à 1 %

2.7 Equipement de fusion pour CMS

2.7.1 Stencil ou écran

Un stencil ou un écran avec ouvertures géométriques de report qui sont appropriées aux

bornes en essai. Sauf accord contraire entre le vendeur et l’utilisateur, il est recommandé que

l’épaisseur nominale du stencil soit de 0,1 mm pour les bornes avec un pas de sortie de

composant inférieur à 0,5 mm, de 0,15 mm pour un composant de pas de sortie entre 0,5 mm

et 0,65 mm et de 0,2 mm pour un composant de pas de sortie supérieur à 0,65 mm.

2.7.2 Raclette en caoutchouc ou spatule métallique

La pâte à braser doit être appliquée sur le stencil ou l’écran en utilisant une spatule pour un

pas fin ou une raclette pour un pas standard.

2.7.3 Substrat en céramique

Les éprouvettes CMS pour les essais simulés de brasabilité avec fusion pour le montage sur

carte doivent être évaluées en utilisant un substrat.

NOTE 1 De la céramique (alumine 90 % − 98 %) peut être utilisée pour toutes les exigences de fusion.

60749-21 © IEC:2004 – 17 –

Chemical composition

The composition in percentage by weight shall be as follows:

Tin 59 % to 61 %

Antimony 0,5 % maximum

Copper 0,1 % maximum

Arsenic 0,05 % maximum

Iron 0,02 % maximum

Lead the remainder.

The solder shall not contain such impurities as aluminium, zinc or cadmium in amounts which

will adversely affect the properties of the solder.

Melting temperature range

The melting temperature range of the 60 % solder is as follows:

Completely solid 183 °C

Completely liquid 188 °C.

2.6.2.2 Lead-free

Unless otherwise detailed in the relevant specification, the solder specification for Pb-free

shall be as follows:

The composition in percentage by weight shall be as follows:

Tin 95 % to 96,5 %

Silver 3 % to 4 %

Copper 0,5 % to 1 %.

2.7 SMD reflow equipment

2.7.1 Stencil or screen

A stencil or screen with pad geometry opening that is appropriate for the terminals being

tested. Unless otherwise agreed upon between vendor and user, nominal stencil thickness

should be 0,1 mm for terminals with less than 0,5 mm component lead pitch, 0,15 mm for a

component with lead pitch of 0,5 mm to 0,65 mm and 0,2 mm for a component with lead pitch

greater than 0,65 mm.

2.7.2 Rubber squeegee or metal spatula

Solder paste shall be applied on to the stencil or screen using a spatula for fine pitch or a

squeegee for standard pitch.

2.7.3 Test substrate

SMD specimens for simulated board mounting reflow solderability testing shall be evaluated

using a substrate.

NOTE 1 A ceramic (alumina 90 % – 98 %) may be used for all reflow requirements.

– 18 – 60749-21 © CEI:2004

NOTE 2 Du substrat verre-epoxy peut être utilisé pour toutes les exigences de fusion. Il convient que le substrat

verre-epoxy puisse résister à la température de brasure (par exemple il ne convient pas pour de la brasure sur

plaque chaude).

NOTE 3 Pour l'inspection visuelle des sorties des dispositifs en essai, il convient que le substrat testé ne soit pas

métallisé (pas de plages de connexions).

2.7.4 Pâte de brasage

Sauf indication contraire, la composition de la pâte de brasage doit être la suivante:

2.7.4.1 Pâte contenant du plomb

La composition de la pâte de brasage doit être conforme au Paragraphe 2.6.2.

Sauf indication contraire dans la spécification applicable, la dimension de la particule de la

poudre de brasage doit être de 20 μm à 45 μm.

La composition du flux doit être conforme au Paragraphe 2.6.1.

La gamme de viscosité de la pâte de brasage et la méthode de mesure doivent être décrite

dans la spécification.

2.7.4.2 Pâte ne contenant pas de plomb

La composition de la brasure doit être conforme à 2.6.2.

La dimension de la poudre de brasage doit être la suivante:

– inférieure à 1 %, plus grande que 53 µm;

– au moins 90 %, entre 22-53 µm;

– inférieure à 10 %, moins de 22 µm.

La forme de la poudre de brasage doit être sphérique.

Le flux utilisé doit consister en masse de 30 % de colophane de polymérisation (point de

ramollissement d'environ 95 °C), 30 % de colophane de dégénération acide dibasique (point

de ramollissement, d'environ 140 °C), 34,7 % d'éther monobutyle de diéthylène glycol, 0,9 %

de 1,3-diphenylguanidine-HBr, 0,5 % d'acide adipique (avec un contenu de chlorine inférieur

à 0,1 %) et 4 % d'huile de ricin figée.

La pâte de brasage à utiliser doit contenir en masse 88 % de poudre de brasage et 12 % de

flux. La gamme de viscosité doit être (180 ±5) Pa s.

NOTE Il convient que le stockage de la pâte et sa durée de vie sur étagère soient conformes aux spécifications

du fabricant.

2.7.5 Equipement de fusion

Un four de fusion à convection ( de préférence), ou un four de fusion à infrarouge, capable

d’atteindre la courbe de température de fusion de la pâte peut être utilisé.

2.7.6 Solvant pour le nettoyage du flux

Matière utilisée pour nettoyer le flux sur les sorties qui doit être capable d’éliminer les résidus

visibles de flux et de satisfaire aux réglementations locales en matière d’environnement.

60749-21 © IEC:2004 – 19 –

NOTE 2 A glass epoxy substrate may be used for all reflow requirements. The glass epoxy substrate should be

capable of withstanding the soldering temperature (e.g. it is not suitable for hot plate soldering).

NOTE 3 For visual inspection of the tested device terminations, the test substrate should be unmetallized (no

lands).

2.7.4 Solder paste

Unless otherwise specified, the composition of the solder paste shall be as follows:

2.7.4.1 Pb-containing paste

The solder composition shall be as specified in 2.6.2.

Unless otherwise specified in the relevant specification, the particle size of the solder powder

shall be 20 µm to 45 µm.

The composition of the flux shall be as specified in 2.6.1.

The viscosity range of the solder paste and method of measurement shall be detailed in the

relevant specification.

2.7.4.2 Pb-free paste

The solder comp

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...