prEN IEC 61189-3-720:2025

(Main)Test methods for electrical materials, printed boards and other interconnection structures and assemblies - Part 3-720: Test methods for interconnection structures (circuit boards) - Transmission loss test method for high frequency multilayer circuit boards

Test methods for electrical materials, printed boards and other interconnection structures and assemblies - Part 3-720: Test methods for interconnection structures (circuit boards) - Transmission loss test method for high frequency multilayer circuit boards

Prüfverfahren für Elektromaterialien, Leiterplatten und andere Verbindungsstrukturen und Baugruppen – Teil 3-720: Prüfverfahren für Verbindungsstrukturen (Leiterplatten) – Prüfverfahren für Übertragungsverluste bei Hochfrequenz-Mehrschichtleiterplatten

Preskusne metode za električne materiale, tiskana vezja ter druge povezovalne strukture in sestave - 3-720. del: Preskusne metode za povezovalne strukture (tiskana vezja) - Preskusna metoda za določanje prenosnih izgub pri visokofrekvenčnih večplastnih tiskanih vezjih

General Information

- Status

- Not Published

- Publication Date

- 18-Jul-2027

- Technical Committee

- CLC/SR 91 - Electronics assembly technology

- Current Stage

- 4060 - Enquiry results established and sent to TC, SR, BTTF - Enquiry

- Start Date

- 20-Mar-2026

- Completion Date

- 20-Mar-2026

Overview

prEN IEC 61189-3-720:2025 is a draft European and International standard developed by the CLC and IEC, specifying test methods for transmission loss measurement in high frequency multilayer circuit boards. This standard, part of the IEC 61189-3 series, focuses on evaluating signal transmission loss in printed circuit boards (PCBs) and interconnection structures operating at frequencies up to 50 GHz. Utilizing the VIPPO (Via-In-Pad Plated Over) structure and advanced measurement methods, it addresses the need for reliable, repeatable characterization of loss mechanisms affecting high-speed, multilayer PCBs.

The purpose of this standard is to provide a uniform method for determining the transmission loss in high frequency interconnection structures, enhancing measurement accuracy and supporting the design and quality assessment of advanced electronic assemblies.

Key Topics

- Transmission Loss in High Frequency PCBs:

Establishes a standardized approach for measuring S-parameters, especially S21 and S11, to evaluate signal loss in multilayer circuit boards. - VIPPO Structure Application:

Details the advantages of the Via-In-Pad Plated Over (VIPPO) design in minimizing parasitic effects and improving signal integrity at high frequencies. - Test Equipment and Setup:

Specifies requirements for Instrumentation, including Vector Network Analyzers (VNA) with bandwidths up to 50 GHz and calibrated test fixtures tailored for PCB measurements. - Specimen Preparation:

Recommends consistent fabrication and handling of test specimens, emphasizing VIPPO design for minimizing discontinuities and ensuring accurate measurements. - De-embedding Methods:

Highlights the use of the IEEE P370 two-line method for fixture de-embedding, ensuring accurate extraction of PCB transmission characteristics independent of test setup influences. - Reporting Requirements:

Outlines essential elements for measurement reporting, including specimen dimensions, materials, apparatus specifications, and detailed result diagrams (e.g., S21, S22).

Applications

prEN IEC 61189-3-720:2025 is practically valuable for:

- PCB Design and Manufacturing:

Enables designers and manufacturers to validate the electrical performance of high-speed, multilayer PCBs used in servers, networking equipment, and RF/microwave systems. - Quality Assurance:

Supports production testing and ensures compliance with stringent signal integrity requirements, especially for telecommunications and data center applications. - R&D and Prototyping:

Provides a scientific basis for evaluating new materials, PCB stackups, and interconnection technologies under real high-frequency conditions. - Component Qualification:

Assists component and PCB suppliers in qualifying their products against internationally-recognized transmission loss benchmarks. - Customer/Supplier Communication:

Establishes a common framework for specifying, comparing, and understanding transmission loss performance, promoting transparency in the supply chain.

Related Standards

- IEC 61189 Series:

General test methods for electrical materials, interconnection structures, and assemblies. - IEEE P370:

Fixture design and data quality metrics for interconnect measurements up to 50 GHz; referenced for de-embedding methods and best practices. - IPC TM 650 2.5.5.14:

Measures high frequency signal loss and propagation on printed boards using frequency domain methods. - Other PCB and signal integrity standards:

Such as IPC-2221 (Generic Standard on Printed Board Design) and standards related to high-frequency PCB material properties.

Keywords: transmission loss test, high frequency PCB, multilayer circuit board, S-parameters, VIPPO structure, signal integrity, IEEE P370, PCB testing standard, IEC 61189-3-720, vector network analyzer, de-embedding method, interconnection structures, quality assurance.

Frequently Asked Questions

prEN IEC 61189-3-720:2025 is a draft published by CLC. Its full title is "Test methods for electrical materials, printed boards and other interconnection structures and assemblies - Part 3-720: Test methods for interconnection structures (circuit boards) - Transmission loss test method for high frequency multilayer circuit boards". This standard covers: Test methods for electrical materials, printed boards and other interconnection structures and assemblies - Part 3-720: Test methods for interconnection structures (circuit boards) - Transmission loss test method for high frequency multilayer circuit boards

Test methods for electrical materials, printed boards and other interconnection structures and assemblies - Part 3-720: Test methods for interconnection structures (circuit boards) - Transmission loss test method for high frequency multilayer circuit boards

prEN IEC 61189-3-720:2025 is classified under the following ICS (International Classification for Standards) categories: 31.180 - Printed circuits and boards. The ICS classification helps identify the subject area and facilitates finding related standards.

prEN IEC 61189-3-720:2025 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

SLOVENSKI STANDARD

01-februar-2026

Preskusne metode za električne materiale, tiskana vezja ter druge povezovalne

strukture in sestave - 3-720. del: Preskusne metode za povezovalne strukture

(tiskana vezja) - Preskusna metoda za določanje prenosnih izgub pri

visokofrekvenčnih večplastnih tiskanih vezjih

Test methods for electrical materials, printed boards and other interconnection structures

and assemblies - Part 3-720: Test methods for interconnection structures (circuit boards)

- Transmission loss test method for high frequency multilayer circuit boards

Ta slovenski standard je istoveten z: prEN IEC 61189-3-720:2025

ICS:

31.180 Tiskana vezja (TIV) in tiskane Printed circuits and boards

plošče

2003-01.Slovenski inštitut za standardizacijo. Razmnoževanje celote ali delov tega standarda ni dovoljeno.

91/2081/CDV

COMMITTEE DRAFT FOR VOTE (CDV)

PROJECT NUMBER:

IEC 61189-3-720 ED1

DATE OF CIRCULATION: CLOSING DATE FOR VOTING:

2025-12-26 2026-03-20

SUPERSEDES DOCUMENTS:

91/2013/CD, 91/2056/CC

IEC TC 91 : ELECTRONICS ASSEMBLY TECHNOLOGY

SECRETARIAT: SECRETARY:

Japan Mr Osamu IKEDA

OF INTEREST TO THE FOLLOWING COMMITTEES: HORIZONTAL FUNCTION(S):

ASPECTS CONCERNED:

SUBMITTED FOR CENELEC PARALLEL VOTING NOT SUBMITTED FOR CENELEC PARALLEL VOTING

Attention IEC-CENELEC parallel voting

The attention of IEC National Committees, members of

CENELEC, is drawn to the fact that this Committee Draft for

Vote (CDV) is submitted for parallel voting.

The CENELEC members are invited to vote through the

CENELEC online voting system.

This document is still under study and subject to change. It should not be used for reference purposes.

Recipients of this document are invited to submit, with their comments, notification of any relevant patent rights of which t hey

are aware and to provide supporting documentation.

Recipients of this document are invited to submit, with their comments, notification of any relevant “In Some Countries”

clauses to be included should this proposal proceed. Recipients are reminded that the CDV stage is the final stage for

submitting ISC clauses. (SEE AC/22/2007 OR NEW GUIDANCE DOC).

TITLE:

Test methods for electrical materials, printed boards and other interconnection structures and

assemblies - Part 3-720: Test methods for interconnection structures (circuit boards) - Transmission

loss test method for high frequency multilayer circuit boards

PROPOSED STABILITY DATE: 2030

NOTE FROM TC/SC OFFICERS:

Approved in WG.

electronic file, to make a copy and to print out the content for the sole purpose of preparing National Committee positions.

You may not copy or "mirror" the file or printed version of the document, or any part of it, for any other purpose without

permission in writing from IEC.

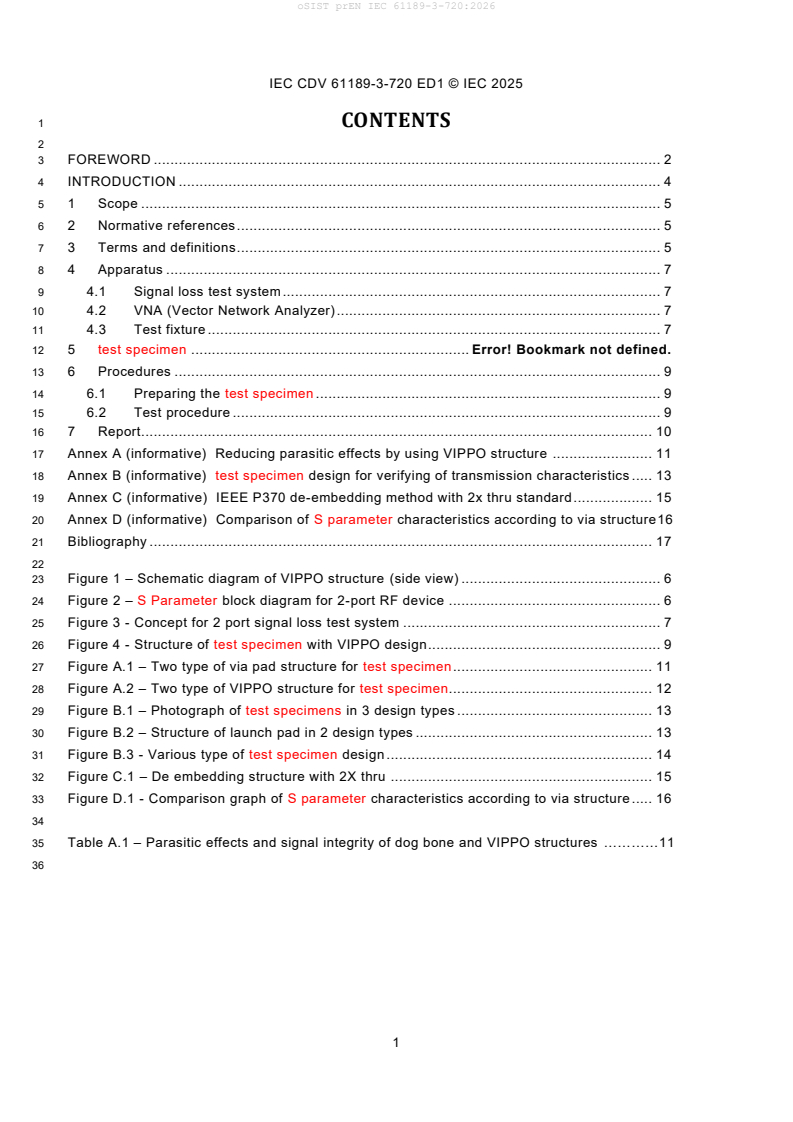

IEC CDV 61189-3-720 ED1 © IEC 2025

1 CONTENTS

3 FOREWORD . 2

4 INTRODUCTION . 4

5 1 Scope . 5

6 2 Normative references . 5

7 3 Terms and definitions . 5

8 4 Apparatus . 7

9 4.1 Signal loss test system . 7

10 4.2 VNA (Vector Network Analyzer) . 7

11 4.3 Test fixture . 7

12 5 test specimen . Error! Bookmark not defined.

13 6 Procedures . 9

14 6.1 Preparing the test specimen . 9

15 6.2 Test procedure . 9

16 7 Report. 10

17 Annex A (informative) Reducing parasitic effects by using VIPPO structure . 11

18 Annex B (informative) test specimen design for verifying of transmission characteristics . 13

19 Annex C (informative) IEEE P370 de-embedding method with 2x thru standard . 15

20 Annex D (informative) Comparison of S parameter characteristics according to via structure16

21 Bibliography . 17

23 Figure 1 – Schematic diagram of VIPPO structure (side view) . 6

24 Figure 2 – S Parameter block diagram for 2-port RF device . 6

25 Figure 3 - Concept for 2 port signal loss test system . 7

26 Figure 4 - Structure of test specimen with VIPPO design . 9

27 Figure A.1 – Two type of via pad structure for test specimen . 11

28 Figure A.2 – Two type of VIPPO structure for test specimen. 12

29 Figure B.1 – Photograph of test specimens in 3 design types . 13

30 Figure B.2 – Structure of launch pad in 2 design types . 13

31 Figure B.3 - Various type of test specimen design . 14

32 Figure C.1 – De embedding structure with 2X thru . 15

33 Figure D.1 - Comparison graph of S parameter characteristics according to via structure . 16

35 Table A.1 – Parasitic effects and signal integrity of dog bone and VIPPO structures …………11

IEC CDV 61189-3-720 ED1 © IEC 2025

37 INTERNATIONAL ELECTROTECHNICAL COMMISSION

38 ____________

39 TEST METHODS FOR ELECTRICAL MATERIALS, PRINTED BOARDS AND OTHER

40 INTERCONNECTION STRUCTURES AND ASSEMBLIES –

42 PART 3-720: TEST METHODS FOR INTERCONNECTION STRUCTURES (CIRCUIT

43 BOARDS) –

45 TRANSMISSION LOSS TEST METHOD FOR HIGH FREQUENCY MULTILAYER

46 CIRCUIT BOARDS

49 FOREWORD

50 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national

51 electrotechnical committees (IEC National Committees). The object of IEC is to promote international co -operation on all

52 questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities ,

53 IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS)

54 and Guides (hereafter referred to as “IEC Publication(s)”). Their preparation is entrusted to technical committees; any IEC

55 National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental

56 and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with

57 the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between

58 the two organizations.

59 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus

60 of opinion on the relevant subjects since each technical committee has representation from all interested IEC National

61 Committees.

62 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in

63 that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC

64 cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

65 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to

66 the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and

67 the corresponding national or regional publication shall be clearly indicated in the latter.

68 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment

69 services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by

70 independent certification bodies.

71 6) All users should ensure that they have the latest edition of this publication.

72 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of

73 its technical committees and IEC National Committees for any personal injury, property damage or other damage of any

74 nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publicatio n,

75 use of, or reliance upon, this IEC Publication or any other IEC Publications.

76 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable

77 for the correct application of this publication.

78 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights.

79 IEC shall not be held responsible for identifying any or all such patent rights.

80 IEC 6XXXX has been prepared by subcommittee XX: TITLE, of IEC technical committee XX: TITLE. It

81 is […an International Standard, a Technical Specification: specify document type…].

82 Full information on the voting for its approval can be found in the report on voting indicated in the above

83 table.

84 The language used for the development of this International Standard is English.

85 This document was drafted in accordance with ISO/IEC Directives, Part 2, and developed in accordance

86 with ISO/IEC Directives, Part 1 and ISO/IEC Directives, IEC Supplement, available at

87 www.iec.ch/members_experts/refdocs. The main document types developed by IEC are described in

88 greater detail at www.iec.ch/publications.

IEC CDV 61189-3-720 ED1 © IEC 2025

89 The committee has decided that the contents of this document will remain unchanged until the stability

90 date indicated on the IEC website under webstore.iec.ch in the data related to the specific document.

91 At this date, the document will be

92 • reconfirmed,

93 • withdrawn,

94 • replaced by a revised edition, or

95 • amended.

IEC CDV 61189-3-720 ED1 © IEC 2025

97 INTRODUCTION

98 The International Electrotechnical Commission (IEC) draws attention to the fact that it is claimed that

99 compliance with this document may involve the use of a patent. IEC takes no position concerning the

100 evidence, validity, and scope of this patent right.

101 The holder of this patent right has assured IEC that s/he is willing to negotiate licences under reasonable

102 and non-discriminatory terms and conditions with applicants throughout the world. In this respect, the

103 statement of the holder of this patent right is registered with IEC. Information may be obtained from the

104 patent database available at patents.iec.ch/.

105 Attention is drawn to the possibility that some of the elements of this document may be the subject of

106 patent rights other than those in the patent database. IEC shall not be held responsible for identifying

107 any or all such patent rights.

IEC CDV 61189-3-720 ED1 © IEC 2025

110 TEST METHODS FOR ELECTRICAL MATERIALS, PRINTED BOARDS AND OTHER

111 INTERCONNECTION STRUCTURES AND ASSEMBLIES –

113 PART 3-720: TEST METHODS FOR INTERCONNECTION STRUCTURES (CIRCUIT

114 BOARDS) –

116 TRANSMISSION LOSS TEST METHOD FOR HIGH FREQUENCY MULTILAYER

117 CIRCUIT BOARDS

120 Scope

121 This International Standard specifies the S Parameter test method for the internal transmission circuit

122 of a multilayer CB(Circuit Board) for high frequency up to 50 GHz. The transmission loss test method

123 that applies the VIPPO structure to the CB surface contributes to improving the signal loss measurement

124 precision and signal integrity of the internal transmission circuit of the high frequency CB. And use of

125 back-drilling with Via In Pad Plated Over(VIPPO) structure can eliminate influence of stubs on signal

126 transmission.

128 Normative references

129 The following documents are referred to in the text in such a way that some or all of their content

130 constitutes requirements of this document. For dated references, only the edition cited applies. For

131 undated references, the latest edition of the referenced document (including any amendments) applies.

132 IEEE P370, A Fixture Design and Data Quality Metric Standard for Interconnects up to 50 GHz

133 Terms and definitions

134 For the purposes of this document, the following terms and definitions apply.

135 ISO and IEC maintain terminology databases for use in standardization at the following addresses:

136 • IEC Electropedia: available at https://www.electropedia.org/

137 • ISO Online browsing platform: available at https://www.iso.org/obp

138 3.1

139 Via in pad plated over

140 VIPPO

141 plated hole that has been filled with conductive or non-conductive material, capped, and plated over,

142 thereby forming a solderable surface pad (see Figure 1).

IEC CDV 61189-3-720 ED1 © IEC 2025

145 Key

146 1 plated via

147 2 filled via with conductive or non-conductive material

148 3 over plated cap

149 NOTE Figure 1 shows the side view of a CB formed with VIPPO structure.

150 Figure 1 – Schematic diagram of VIPPO structure (side view)

151 3.2

152 S Parameter

153 ratio of output voltage to input voltage in frequency domain, The “S Parameters” describe the

154 relationship between the incident and reflected waves at each port. For example, S21 means the ratio

155 of the transmitted output voltage at port 2 to the input voltage at port 1. In other words, it is a value that

156 indicates how much power input into port 1 is output through port 2. Where S11 means the ratio of the

157 reflected voltage at port 1 to the input voltage at port 1. Where S12 means the ratio of the transmitted

158 output voltage at port 1 to the input voltage at port 2. Where S22 means the ratio of the reflected voltage

159 at port 2 to the input voltage at port 2. (see Figure 2).

160 NOTE Figure 2 shows the S Parameter block diagram for forward trnsmission of a 2-port RF device

161 Figure 2 - S Parameter block diagram for 2 port RF device

oSIST prEN IEC 61189

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...