ASTM F1392-00

(Test Method)Standard Test Method for Determining Net Carrier Density Profiles in Silicon Wafers by Capacitance-Voltage Measurements With a Mercury Probe

Standard Test Method for Determining Net Carrier Density Profiles in Silicon Wafers by Capacitance-Voltage Measurements With a Mercury Probe

SCOPE

1.1 This test method covers the measurement of net carrier density and net carrier density profiles in epitaxial and polished bulk silicon wafers in the range from about 4 X 10 13 to about 8 X 10 16 carriers/cm (resistivity range from about 0.1 to about 100 [omega][dot]cm in -type wafers and from about 0.24 to about 330 [omega][dot]cm in -type wafers).

1.2 This test method requires the formation of a Schottky barrier diode with a mercury probe contact to an epitaxial or polished wafer surface. Chemical treatment of the silicon surface may be required to produce a reliable Schottky barrier diode (1). The surface treatment chemistries are different for - and -type wafers. This test method is sometimes considered destructive due to the possibility of contamination from the Schottky contact formed on the wafer surface; however, repetitive measurements may be made on the same test specimen.

1.3 This test method may be applied to epitaxial layers on the same or opposite conductivity type substrate. This test method includes descriptions of fixtures for measuring substrates with or without an insulating backseal layer.

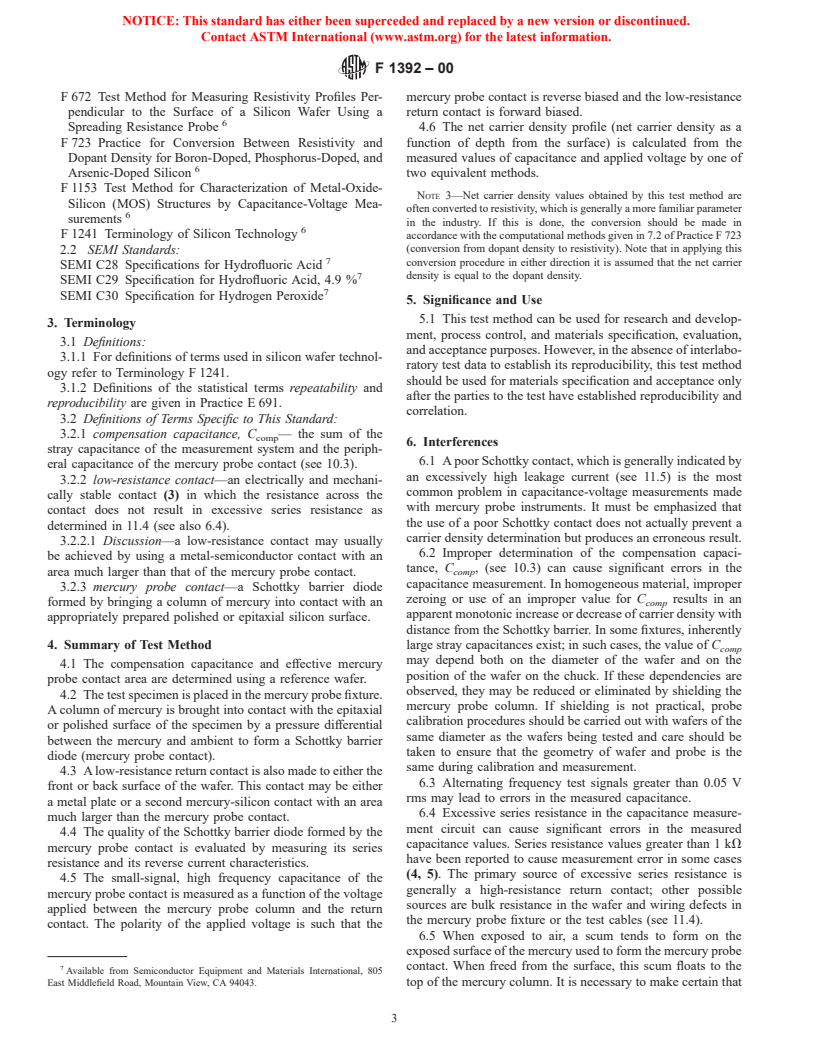

1.4 The depth of the region that can be profiled depends on the doping level in the test specimen. Based on data reported by Severin (1) and Grove (2), Fig. 1 shows the relationships between depletion depth, dopant density, and applied voltage together with the breakdown voltage of a mercury silicon contact. The test specimen can be profiled from approximately the depletion depth corresponding to an applied voltage of 1 V to the depletion depth corresponding to the maximum applied voltage (200 V or about 80% of the breakdown voltage, whichever is lower). To be measured by this test method, a layer must be thicker than the depletion depth corresponding to an applied voltage of 2 V.

1.5 This test method is intended for rapid carrier density determination when extended sample preparation time or high temperature processing of the wafer is not practical. Note 1-Test Method F419 is an alternative method for determining net carrier density profiles in silicon wafers from capacitance-voltage measurements. This test method requires the use of one of the following structures: ( ) a gated or ungated p-n junction diode fabricated using either planar or mesa technology or ( ) an evaporated metal Schottky diode.

1.6 This test method provides for determining the effective area of the mercury probe contact using polished bulk reference wafers that have been measured for resistivity at 23°C in accordance with Test Method F84 (Note 2). This test method also includes procedures for calibration of the apparatus for measuring both capacitance and voltage. Note 2-An alternative method of determining the effective area of the mercury probe contact that involves the use of reference wafers whose net carrier density has been measured using fabricated mesa or planar p-n junction diodes or evaporated Schottky diodes is not included in this test method but may be used if agreed upon by the parties to the test.

1.7 This standard does not purport to address all of the safety problems, if any, associated with its use. It is the responsibility of the user of this standard to establish appropriate safety and health practices and determine the applicability of regulatory limitations prior to use. Specific hazard statements are given in 7.1 (Note 4), 7.2, 7.10.3 (Note 8), 8.2, 11.5.1 (Note 18), 11.6.3, and 11.6.5.

General Information

Relations

Standards Content (Sample)

NOTICE: This standard has either been superceded and replaced by a new version or discontinued.

Contact ASTM International (www.astm.org) for the latest information.

Designation: F 1392 – 00

Standard Test Method for

Determining Net Carrier Density Profiles in Silicon Wafers

by Capacitance-Voltage Measurements With a Mercury

Probe

This standard is issued under the fixed designation F 1392; the number immediately following the designation indicates the year of

original adoption or, in the case of revision, the year of last revision. A number in parentheses indicates the year of last reapproval. A

superscript epsilon (e) indicates an editorial change since the last revision or reapproval.

1. Scope voltage (200 V or about 80 % of the breakdown voltage,

whichever is lower). To be measured by this test method, a

1.1 This test method covers the measurement of net carrier

layer must be thicker than the depletion depth corresponding to

density and net carrier density profiles in epitaxial and polished

an applied voltage of 2 V.

bulk silicon wafers in the range from about 4 3 10 to about

16 3

1.5 This test method is intended for rapid carrier density

8 3 10 carriers/cm (resistivity range from about 0.1 to

determination when extended sample preparation time or high

about 100 V·cm in n-type wafers and from about 0.24 to about

temperature processing of the wafer is not practical.

330 V·cm in p-type wafers).

1.2 This test method requires the formation of a Schottky

NOTE 1—Test Method F 419 is an alternative method for determining

barrier diode with a mercury probe contact to an epitaxial or

net carrier density profiles in silicon wafers from capacitance-voltage

measurements. This test method requires the use of one of the following

polished wafer surface. Chemical treatment of the silicon

structures: (1) a gated or ungated p-n junction diode fabricated using either

surface may be required to produce a reliable Schottky barrier

3 planar or mesa technology or ( 2) an evaporated metal Schottky diode.

diode (1). The surface treatment chemistries are different for

n- and p-type wafers. This test method is sometimes considered 1.6 This test method provides for determining the effective

area of the mercury probe contact using polished bulk refer-

destructive due to the possibility of contamination from the

Schottky contact formed on the wafer surface; however, ence wafers that have been measured for resistivity at 23°C in

accordance with Test Method F 84 (Note 2). This test method

repetitive measurements may be made on the same test

specimen. also includes procedures for calibration of the apparatus for

measuring both capacitance and voltage.

1.3 This test method may be applied to epitaxial layers on

the same or opposite conductivity type substrate. This test

NOTE 2—An alternative method of determining the effective area of the

method includes descriptions of fixtures for measuring sub-

mercury probe contact that involves the use of reference wafers whose net

strates with or without an insulating backseal layer.

carrier density has been measured using fabricated mesa or planar p-n

1.4 The depth of the region that can be profiled depends on junction diodes or evaporated Schottky diodes is not included in this test

method but may be used if agreed upon by the parties to the test.

the doping level in the test specimen. Based on data reported

by Severin (1) and Grove (2), Fig. 1 shows the relationships

1.7 This standard does not purport to address all of the

between depletion depth, dopant density, and applied voltage

safety concerns, if any, associated with its use. It is the

together with the breakdown voltage of a mercury silicon

responsibility of the user of this standard to establish appro-

contact. The test specimen can be profiled from approximately

priate safety and health practices and determine the applica-

the depletion depth corresponding to an applied voltage of 1 V

bility of regulatory limitations prior to use. Specific hazard

to the depletion depth corresponding to the maximum applied

statements are given in 7.1, ( 7.2, 7.10.3 (Note 7), 8.2, 11.5.1,

11.6.3, and 11.6.5.

2. Referenced Documents

This test method is under the jurisdiction of ASTM Committee F-1 on

2.1 ASTM Standards:

Electronics and is the direct responsibility of Subcommittee F01.06 on Silicon

D 5127 Guide for Ultra Pure Water Used in the Electronics

Materials and Process Control.

Current edition approved June 10, 2000. Published August 2000. Originally

and Semiconductor Industry

published as F 1392 – 92. Last previous edition F 1392 – 93.

D 4356 Practice for Establishing Consistent Test Method

DIN 50439, Determination of the Dopant Concentration Profile of a Single

Tolerances

Crystal Semiconductor Material by Means of the Capacitance-Voltage Method and

Mercury Contact, is technically equivalent to this test method. DIN 50439 is the E 691 Practice for Conducting an Interlaboratory Study to

responsibility of DIN Committee NMP 221, with which Committee F-1 maintains

close liaison. DIN 50439 is available from Beuth Verlag GmbH, Burggrafenstraße

4-10, D-1000, Berlin 30, Germany.

3 4

The boldface numbers in parentheses refer to the list of references at the end of Annual Book of ASTM Standards, Vol 11.01.

this test method. Annual Book of ASTM Standards, Vol 14.02.

Copyright © ASTM International, 100 Barr Harbor Drive, PO Box C700, West Conshohocken, PA 19428-2959, United States.

NOTICE: This standard has either been superceded and replaced by a new version or discontinued.

Contact ASTM International (www.astm.org) for the latest information.

F 1392 – 00

(a) Depletion Depth as a Function of Dopant Density with Applied Reverse Bias Voltage as a Parameter.

(b) Applied Reverse Bias Voltage as a Function of Dopant Density with Depletion as a Parameter.

NOTE 1—The light dashed line represents the applied reverse bias voltage at which breakdown occurs in a mercury-silicon contact; the heavy dashed

line represents 80 % of this voltage, it is recommended that the applied reverse bias voltage not exceed this value. The light chain-dot line represents the

maximum reverse bias voltage specified in this test method.

FIG. 1 Relationships Between Depletion Depth, Applied Reverse Bias Voltage, and Dopant Density

Determine the Precision of a Test Method F 81 Test Method for Measuring Radial Resistivity Varia-

F 26 Test Methods for Determining the Orientation of a

tion on Silicon Wafers

Semiconductive Single Crystal

F 84 Test Method for Measuring Resistivity of Silicon

F 42 Test Methods for Conductivity Type of Extrinsic 6

Wafers with an In-Line Four-Point Probe

Semiconducting Materials

F 419 Test Method for Determining Carrier Density in

Silicon Epitaxial Layers by Capacitance-Voltage Measure-

ments on Fabricated Junction or Schottky Diodes

Annual Book of ASTM Standards, Vol 10.05.

NOTICE: This standard has either been superceded and replaced by a new version or discontinued.

Contact ASTM International (www.astm.org) for the latest information.

F 1392 – 00

F 672 Test Method for Measuring Resistivity Profiles Per- mercury probe contact is reverse biased and the low-resistance

pendicular to the Surface of a Silicon Wafer Using a return contact is forward biased.

Spreading Resistance Probe 4.6 The net carrier density profile (net carrier density as a

F 723 Practice for Conversion Between Resistivity and function of depth from the surface) is calculated from the

Dopant Density for Boron-Doped, Phosphorus-Doped, and measured values of capacitance and applied voltage by one of

Arsenic-Doped Silicon two equivalent methods.

F 1153 Test Method for Characterization of Metal-Oxide-

NOTE 3—Net carrier density values obtained by this test method are

Silicon (MOS) Structures by Capacitance-Voltage Mea-

often converted to resistivity, which is generally a more familiar parameter

surements

in the industry. If this is done, the conversion should be made in

F 1241 Terminology of Silicon Technology

accordance with the computational methods given in 7.2 of Practice F 723

(conversion from dopant density to resistivity). Note that in applying this

2.2 SEMI Standards:

conversion procedure in either direction it is assumed that the net carrier

SEMI C28 Specifications for Hydrofluoric Acid

7 density is equal to the dopant density.

SEMI C29 Specification for Hydrofluoric Acid, 4.9 %

SEMI C30 Specification for Hydrogen Peroxide

5. Significance and Use

5.1 This test method can be used for research and develop-

3. Terminology

ment, process control, and materials specification, evaluation,

3.1 Definitions:

and acceptance purposes. However, in the absence of interlabo-

3.1.1 For definitions of terms used in silicon wafer technol-

ratory test data to establish its reproducibility, this test method

ogy refer to Terminology F 1241.

should be used for materials specification and acceptance only

3.1.2 Definitions of the statistical terms repeatability and

after the parties to the test have established reproducibility and

reproducibility are given in Practice E 691.

correlation.

3.2 Definitions of Terms Specific to This Standard:

3.2.1 compensation capacitance, C — the sum of the

comp

6. Interferences

stray capacitance of the measurement system and the periph-

6.1 A poor Schottky contact, which is generally indicated by

eral capacitance of the mercury probe contact (see 10.3).

an excessively high leakage current (see 11.5) is the most

3.2.2 low-resistance contact—an electrically and mechani-

common problem in capacitance-voltage measurements made

cally stable contact (3) in which the resistance across the

with mercury probe instruments. It must be emphasized that

contact does not result in excessive series resistance as

the use of a poor Schottky contact does not actually prevent a

determined in 11.4 (see also 6.4).

carrier density determination but produces an erroneous result.

3.2.2.1 Discussion—a low-resistance contact may usually

6.2 Improper determination of the compensation capaci-

be achieved by using a metal-semiconductor contact with an

tance, C , (see 10.3) can cause significant errors in the

area much larger than that of the mercury probe contact. comp

capacitance measurement. In homogeneous material, improper

3.2.3 mercury probe contact—a Schottky barrier diode

zeroing or use of an improper value for C results in an

formed by bringing a column of mercury into contact with an comp

apparent monotonic increase or decrease of carrier density with

appropriately prepared polished or epitaxial silicon surface.

distance from the Schottky barrier. In some fixtures, inherently

4. Summary of Test Method large stray capacitances exist; in such cases, the value of C

comp

may depend both on the diameter of the wafer and on the

4.1 The compensation capacitance and effective mercury

position of the wafer on the chuck. If these dependencies are

probe contact area are determined using a reference wafer.

observed, they may be reduced or eliminated by shielding the

4.2 The test specimen is placed in the mercury probe fixture.

mercury probe column. If shielding is not practical, probe

A column of mercury is brought into contact with the epitaxial

calibration procedures should be carried out with wafers of the

or polished surface of the specimen by a pressure differential

same diameter as the wafers being tested and care should be

between the mercury and ambient to form a Schottky barrier

taken to ensure that the geometry of wafer and probe is the

diode (mercury probe contact).

same during calibration and measurement.

4.3 A low-resistance return contact is also made to either the

6.3 Alternating frequency test signals greater than 0.05 V

front or back surface of the wafer. This contact may be either

rms may lead to errors in the measured capacitance.

a metal plate or a second mercury-silicon contact with an area

6.4 Excessive series resistance in the capacitance measure-

much larger than the mercury probe contact.

ment circuit can cause significant errors in the measured

4.4 The quality of the Schottky barrier diode formed by the

capacitance values. Series resistance values greater than 1 kV

mercury probe contact is evaluated by measuring its series

have been reported to cause measurement error in some cases

resistance and its reverse current characteristics.

(4, 5). The primary source of excessive series resistance is

4.5 The small-signal, high frequency capacitance of the

generally a high-resistance return contact; other possible

mercury probe contact is measured as a function of the voltage

sources are bulk resistance in the wafer and wiring defects in

applied between the mercury probe column and the return

the mercury probe fixture or the test cables (see 11.4).

contact. The polarity of the applied voltage is such that the

6.5 When exposed to air, a scum tends to form on the

exposed surface of the mercury used to form the mercury probe

7 contact. When freed from the surface, this scum floats to the

Available from Semiconductor Equipment and Materials International, 805

East Middlefield Road, Mountain View, CA 94043. top of the mercury column. It is necessary to make certain that

NOTICE: This standard has either been superceded and replaced by a new version or discontinued.

Contact ASTM International (www.astm.org) for the latest information.

F 1392 – 00

the mercury that contacts the wafer surface is clean by sustaining an external d-c bias of up to 200 V. Provision shall

changing the mercury periodically or by otherwise removing be made to compensate a compensation capacitance of up to 10

the scum from the exposed surface. pF.

6.6 A dirty or damaged capillary tube containing the mer-

NOTE 4—Capacitance meters or bridges capable of measuring the phase

cury column may also result in unstable measurements (see

angle, equivalent series resistance, conductance or total impedance in

10.4.2.2).

addition to the capacitance may be used.

6.7 If the reference wafer is not sufficiently uniform

NOTE 5—Capacitance meters with nominal frequencies from 100 kHz

throughout its thickness, the value of net carrier density, N ,

to 1 MHz have been used for measurements of the type covered by this

ref

test method. If an instrument with a nominal frequency other than 1 MHz

determined by the four-point probe measurement (see 8.4.3)

is employed, the user shall demonstrate that it obtains results equivalent to

may differ from the value of net carrier density at the surface

the specified instrument.

where the mercury probe measurement is made. Use of

erroneous values of N results in incorrect values for effective

7.4 Dc Power Supply, continuously variable from 0 V to the

ref

probe contact area (see 10.3). Further, if the resistivity profile

maximum expected reverse bias (Note 6) or 200 V, whichever

of the reference wafer is not uniform near the surface, an

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.