ASTM F533-02a

(Test Method)Standard Test Method for Thickness and Thickness Variation of Silicon Wafers (Withdrawn 2003)

Standard Test Method for Thickness and Thickness Variation of Silicon Wafers (Withdrawn 2003)

SCOPE

This standard was transferred to SEMI (www.semi.org) May 2003

1.1 This test method covers measurement of the thickness of silicon wafers, polished or unpolished, and estimation of the variation in thickness across the wafer.

1.2 This test method is intended primarily for use with wafers that meet the dimension and tolerance requirements of SEMI Specifications M1. However, it can be applied to circular silicon wafers, or substrates of any diameter and thickness that can be handled without breaking.

1.3 This test method is suitable for both contact and contactless gaging equipment. Precision statements have been established for each.

1.4 The values stated in inch-pound units are to be regarded as standard. The values in parentheses are for information only.

1.5 This standard does not purport to address all of the safety concerns, if any, associated with its use. It is the responsibility of the user of this standard to establish appropriate safety and health practices and determine the applicability of regulatory limitations prior to use.

General Information

Relations

Standards Content (Sample)

NOTICE: This standard has either been superceded and replaced by a new version or discontinued.

Contact ASTM International (www.astm.org) for the latest information.

Designation: F 533 – 02a

Standard Test Method for

1

Thickness and Thickness Variation of Silicon Wafers

This standard is issued under the fixed designation F 533; the number immediately following the designation indicates the year of

original adoption or, in the case of revision, the year of last revision. A number in parentheses indicates the year of last reapproval. A

superscript epsilon (e) indicates an editorial change since the last revision or reapproval.

INTRODUCTION

When this test method was developed in the 1970s, non-contact thickness gages employing manual

wafer positioning, which are the basis of this test method, were in routine use. More recently, faster,

automated instruments have replaced these manual gages for most common uses in the semiconductor

industry. In these automatic systems, microprocessors or microcomputers are used to control wafer

positioning, operate the instrument and to analyze the data. See Test Method F 1530.

Despite the fact that this test method is not commonly used in its present form, it embodies all the

basic elements of this test method and a simple analysis of data. Thus, it provides useful guidance in

the fundamentals and appplication of differential non-contact wafer thickness measurements.

1. Scope F 1530 Test Method for Measuring Flatness, Thickness and

2

Thickness Variation on Silicon Wafers by Automated

1.1 This test method covers measurement of the thickness

3

Noncontact Scanning

of silicon wafers, polished or unpolished, and estimation of the

2.2 SEMI Standard:

variation in thickness across the wafer.

SEMI M1, Specifications for Polished Monocrystalline

1.2 This test method is intended primarily for use with

4

Silicon Wafers

wafers that meet the dimension and tolerance requirements of

2.3 Federal Standards:

SEMI Specifications M1. However, it can be applied to circular

Fed. Std. No. 209E Controlled Environment Clean Room

silicon, wafers or substrates of any diameter and thickness that

5

and Work Station Requirements

can be handled without breaking.

Fed. Spec. GGG-G-15C Gage Blocks and Accessories (Inch

1.3 This test method is suitable for both contact and

6

and Metric), Nov. 6, 1970

contactless gaging equipment. Precision statements have been

2.4 ISO Standard

established for each.

ISO 14644-1, Cleanrooms and associated controlled envi-

1.4 The values stated in inch-pound units are to be regarded

7

ronments — Part 1: Classification of airborne particulates

as standard. The values in parentheses are for information only.

1.5 This standard does not purport to address all of the

3. Terminology

safety concerns, if any, associated with its use. It is the

3.1 Definitions:

responsibility of the user of this standard to establish appro-

3.1.1 back surface—of a semiconductor wafer, the exposed

priate safety and health practices and determine the applica-

surface opposite to that upon which active semiconductor

bility of regulatory limitations prior to use.

devices have been or will be fabricated.

2. Referenced Documents

2.1 ASTM Standards:

1 3

This test method is under the jurisdiction of ASTM Committee F01 on Annual Book of ASTM Standards, Vol 10.05.

4

Electronics and is the direct responsibility of Subcommittee F01.06 on Electrical Available from Semiconductor Equipment and Materials International, 3081

and Optical Measurement. Zanker Road, San Jose, CA 95134 (www.semi.org).

5

Current edition approved Dec. 10, 2002. Published February 2003. Originally Available from GSA Business Service Centers in Boston, New York, Atlanta,

approved in 1977 as F 533 – 77T. Last previous edition approved in 2002 as Chicago, Kansas City, Mo., Fort Worth, Denver, San Francisco, Los Angeles, and

F 533 – 02. Seattle.

2 6

DIN 50441/1 is an equivalent method. It is the responsibility of DIN Committee Available from the Superintendent of Documents, U.S. Government Printing

NMP 221, with which Committee F01 maintains close liaison. DIN 50441/1. Office, Washington, DC 20402.

7

Determinaton of the Geometric Dimensions of Semiconductor Slices; Measurement ISO Central Secretariat, C. P. 56, CH-1211 Genève 20, Switzerland; available

of Thickness, available from Beuth Verlag, Gmbh, Burggrafenstrasse 4-10, D-1000 in the U.S. from American National Standards Institute, 25 West 43rd Street, 4th

Berlin 30, Federal Republic of Germany. Floor, New York, NY 10036.

Copyright © ASTM International, 100 Barr Harbor Drive, PO Box C700, West Conshohocken, PA 19428-2959, United States.

1

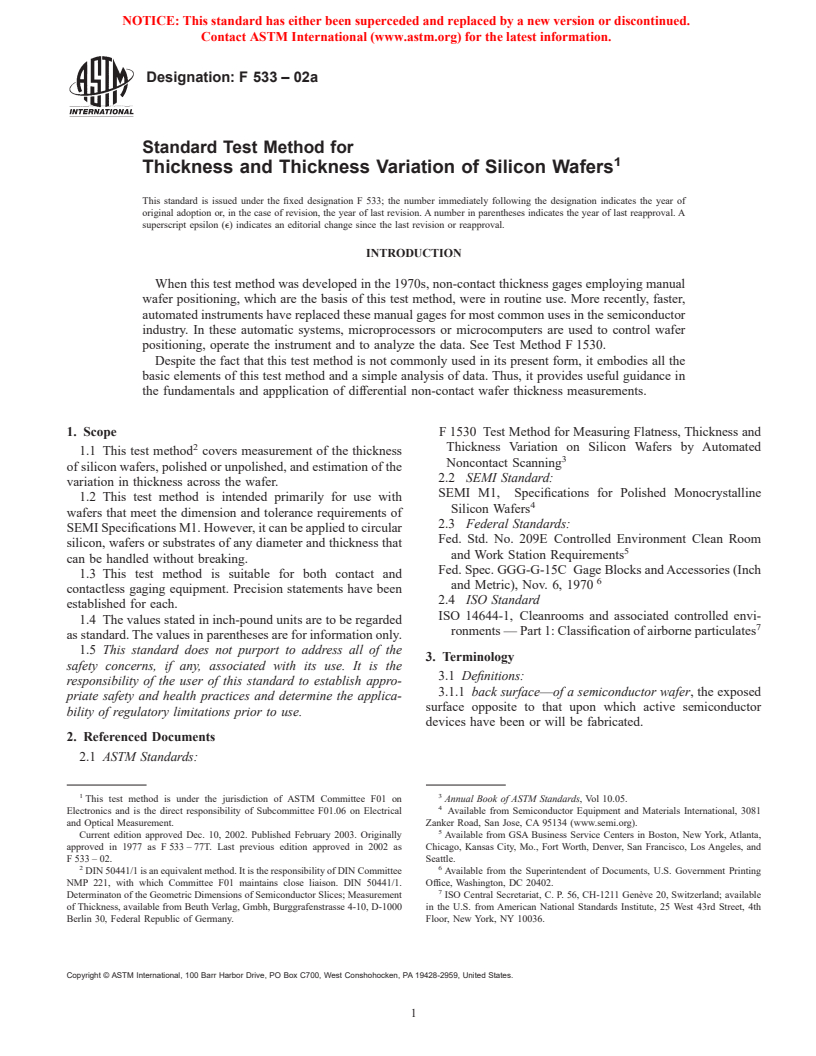

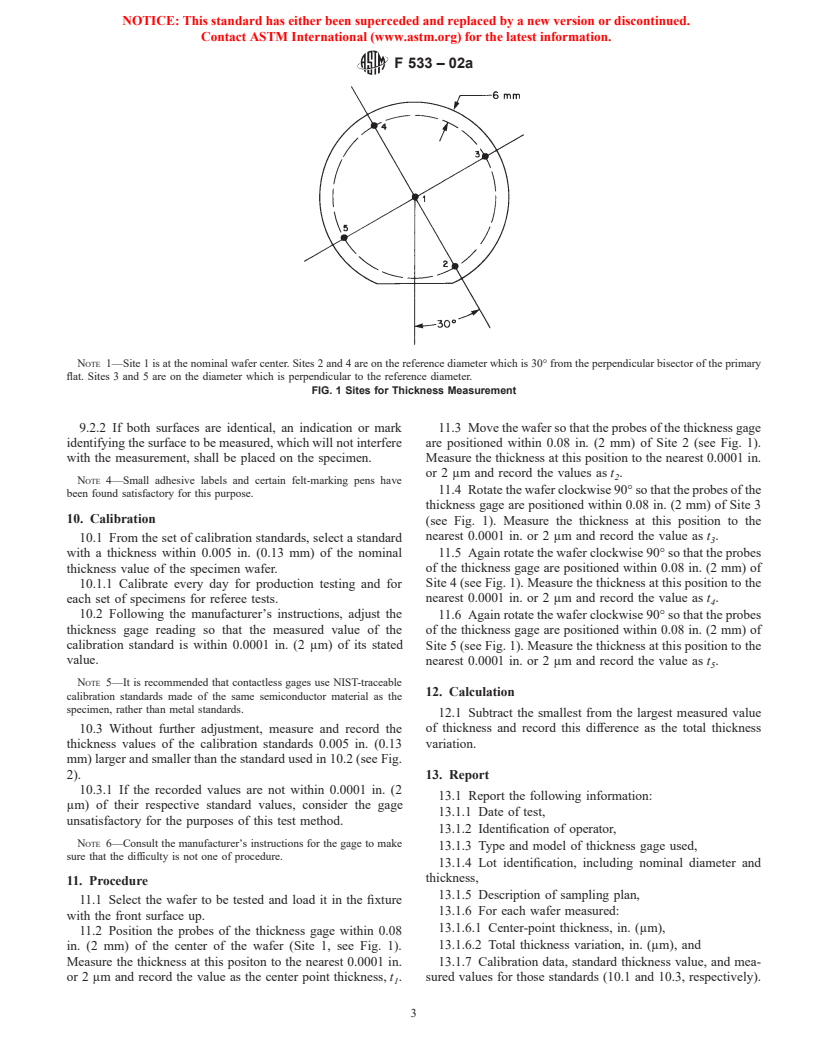

---------------------- Page: 1 ----------------------

NOTICE: This standard has either been superceded and replaced by a new version or discontinued.

Contact ASTM International (www.astm.org) for the latest information.

F 533 – 02a

3.1.2 front surface—of a semiconductor wafer, the exposed 7. Apparatus

surface upon which active semiconductor devices have been or

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.