IEC TS 62878-2-3:2015

(Main)Device embedded substrate - Part 2-3: Guidelines - Design guide

Device embedded substrate - Part 2-3: Guidelines - Design guide

IEC TS 62878-2-3:2015 describes the design guide of device embedded substrates. The design guide of device embedded substrate is essentially the same as that of various electronic circuit boards. This part of IEC 62878 enables a thorough understanding of circuit design, structure design, board design, board manufacturing, jisso (assembly processes) and tests of products. It is applicable to device embedded substrates fabricated by use of organic base material, which include for example active or passive devices, discrete components formed in the fabrication process of electronic wiring board, and sheet formed components.

Substrat avec appareil(s) intégré(s) - Partie 2-3: Directives - Guide de conception

L'IEC TS 62878-2-3:2015 décrit le guide de conception des substrats avec appareil(s) intégré(s). Le guide de conception du substrat avec appareil(s) intégré(s) est essentiellement identique à celui de différentes cartes de circuits électroniques. La présente partie de l'IEC 62878 permet une compréhension approfondie de la conception du circuit, de la conception de la structure, de la conception de la carte, de la fabrication de la carte, de jisso (processus d'assemblage) et des essais des produits. Il est applicable aux substrats avec appareil(s) intégré(s) fabriqués à partir de matériaux de base organiques, y compris par exemple les appareils actifs ou passifs, les composants discrets formés lors du processus de fabrication d'une carte de câblage électronique, ainsi que les composants de feuilles minces.

General Information

- Status

- Published

- Publication Date

- 26-Mar-2015

- Technical Committee

- TC 91 - Electronics assembly technology

- Drafting Committee

- WG 6 - TC 91/WG 6

- Current Stage

- PPUB - Publication issued

- Start Date

- 27-Mar-2015

- Completion Date

- 15-Mar-2015

Overview

IEC TS 62878-2-3:2015 is an international technical specification published by the International Electrotechnical Commission (IEC) providing comprehensive design guidelines for device embedded substrates (DES). Device embedded substrates are advanced electronic circuit boards with embedded discrete active and passive devices within organic base materials. This part of IEC 62878 offers crucial guidance on circuit design, structural layout, manufacturing, assembly (known as jisso), and testing principles for DES, enabling engineers and manufacturers to optimize design and production processes.

The standard plays a vital role in establishing a common understanding for industry players by addressing the key aspects involved in embedding devices, including electrical connections such as vias, conductor plating, and conductive printing. However, it specifically excludes re-distribution layers (RDL) and certain electronic modules defined by IEC 62421.

Key Topics

Design Principles for Device Embedded Substrates

The document outlines design considerations similar to traditional electronic circuit boards but tailored for embedded device integration. It covers layer definitions, conductor spacing at terminals, and surface specifications on both top and bottom surfaces of the substrate.Structure and Layer Definitions

IEC TS 62878-2-3 elaborates on the multi-layer architecture of device embedded substrates, including pad and via connections. It clarifies dielectric gaps, layer gaps, and interconnection positions essential for reliable substrate design.Base and Embedding Conditions

The specification details the necessary conditions for preparing substrates and embedding devices, offering recommendations for assembly techniques and materials used to ensure quality and performance.Assembly Processes (Jisso)

Guidance on embedding discrete components during substrate fabrication is provided, discussing optimal methodologies to integrate devices effectively without compromising substrate integrity.Design Specification Templates

The standard provides templates and graphical indications for device embedded substrate design specifications, ensuring consistent documentation and clear communication among stakeholders.

Applications

IEC TS 62878-2-3:2015 serves as a critical resource for industries involved in:

Electronic Circuit Board Manufacturing

Assisting PCB designers and manufacturers in embedding active and passive devices within substrates for enhanced miniaturization and functionality.Consumer Electronics and Telecommunications

Enabling compact and high-performance substrate design essential for smartphones, tablets, and high-frequency communication devices.Automotive and Industrial Electronics

Providing design methodologies that meet high reliability and environmental robustness requirements for embedded substrate technologies.Research & Development in Electronics Assembly

Facilitating innovation in electronic packaging by promoting a thorough understanding of structural and design parameters of device embedded substrates.

Related Standards

For comprehensive understanding and practical implementation, IEC TS 62878-2-3 is used alongside the following standards:

IEC 62878-1-1 – Test methods for device embedded substrates; for verifying quality and performance through defined testing procedures.

IEC TS 62878-2-1 – General description of device embedded substrate technology; foundational knowledge for the series.

IEC TS 62878-2-4 – Test element groups specifications; detailing the test structures used for process and performance evaluation.

IEC 60194 – Printed board design, manufacture, and assembly – Terms and definitions; essential for consistent terminology.

IEC 62421 – Defines electronic modules excluded by IEC 62878 series; relevant for understanding scope boundaries.

Conclusion

IEC TS 62878-2-3:2015 is an essential design guide standard for professionals engaged in the development, manufacturing, and assembly of device embedded substrates. By providing a detailed framework on structural design, embedding practices, and testing considerations, it supports electronic industries striving for miniaturization, integration, and enhanced substrate reliability.

Adhering to this IEC technical specification ensures that electronic circuits with embedded devices meet international best practices, thereby contributing to innovative, compact, and high-performance electronics solutions worldwide.

Keywords: Device embedded substrate design, IEC TS 62878-2-3, embedded devices, substrate design guide, electronic circuit board standards, PCB embedded components, jisso assembly processes, organic base material substrate, embedded passive devices, IEC standards for electronics.

Frequently Asked Questions

IEC TS 62878-2-3:2015 is a technical specification published by the International Electrotechnical Commission (IEC). Its full title is "Device embedded substrate - Part 2-3: Guidelines - Design guide". This standard covers: IEC TS 62878-2-3:2015 describes the design guide of device embedded substrates. The design guide of device embedded substrate is essentially the same as that of various electronic circuit boards. This part of IEC 62878 enables a thorough understanding of circuit design, structure design, board design, board manufacturing, jisso (assembly processes) and tests of products. It is applicable to device embedded substrates fabricated by use of organic base material, which include for example active or passive devices, discrete components formed in the fabrication process of electronic wiring board, and sheet formed components.

IEC TS 62878-2-3:2015 describes the design guide of device embedded substrates. The design guide of device embedded substrate is essentially the same as that of various electronic circuit boards. This part of IEC 62878 enables a thorough understanding of circuit design, structure design, board design, board manufacturing, jisso (assembly processes) and tests of products. It is applicable to device embedded substrates fabricated by use of organic base material, which include for example active or passive devices, discrete components formed in the fabrication process of electronic wiring board, and sheet formed components.

IEC TS 62878-2-3:2015 is classified under the following ICS (International Classification for Standards) categories: 31.180 - Printed circuits and boards; 31.190 - Electronic component assemblies. The ICS classification helps identify the subject area and facilitates finding related standards.

IEC TS 62878-2-3:2015 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

IEC TS 62878-2-3 ®

Edition 1.0 2015-03

TECHNICAL

SPECIFICATION

SPECIFICATION

TECHNIQUE

colour

inside

Device embedded substrate –

Part 2-3: Guidelines – Design guide

Substrat avec appareil(s) intégré(s) –

Partie 2-3: Directives – Guide de conception

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form

or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from

either IEC or IEC's member National Committee in the country of the requester. If you have any questions about IEC

copyright or have an enquiry about obtaining additional rights to this publication, please contact the address below or

your local IEC member National Committee for further information.

Droits de reproduction réservés. Sauf indication contraire, aucune partie de cette publication ne peut être reproduite

ni utilisée sous quelque forme que ce soit et par aucun procédé, électronique ou mécanique, y compris la photocopie

et les microfilms, sans l'accord écrit de l'IEC ou du Comité national de l'IEC du pays du demandeur. Si vous avez des

questions sur le copyright de l'IEC ou si vous désirez obtenir des droits supplémentaires sur cette publication, utilisez

les coordonnées ci-après ou contactez le Comité national de l'IEC de votre pays de résidence.

IEC Central Office Tel.: +41 22 919 02 11

3, rue de Varembé Fax: +41 22 919 03 00

CH-1211 Geneva 20 info@iec.ch

Switzerland www.iec.ch

About the IEC

The International Electrotechnical Commission (IEC) is the leading global organization that prepares and publishes

International Standards for all electrical, electronic and related technologies.

About IEC publications

The technical content of IEC publications is kept under constant review by the IEC. Please make sure that you have the

latest edition, a corrigenda or an amendment might have been published.

IEC Catalogue - webstore.iec.ch/catalogue Electropedia - www.electropedia.org

The stand-alone application for consulting the entire The world's leading online dictionary of electronic and

bibliographical information on IEC International Standards, electrical terms containing more than 30 000 terms and

Technical Specifications, Technical Reports and other definitions in English and French, with equivalent terms in 15

documents. Available for PC, Mac OS, Android Tablets and additional languages. Also known as the International

iPad. Electrotechnical Vocabulary (IEV) online.

IEC publications search - www.iec.ch/searchpub IEC Glossary - std.iec.ch/glossary

The advanced search enables to find IEC publications by a More than 60 000 electrotechnical terminology entries in

variety of criteria (reference number, text, technical English and French extracted from the Terms and Definitions

committee,…). It also gives information on projects, replaced clause of IEC publications issued since 2002. Some entries

and withdrawn publications. have been collected from earlier publications of IEC TC 37,

77, 86 and CISPR.

IEC Just Published - webstore.iec.ch/justpublished

Stay up to date on all new IEC publications. Just Published IEC Customer Service Centre - webstore.iec.ch/csc

details all new publications released. Available online and If you wish to give us your feedback on this publication or

also once a month by email. need further assistance, please contact the Customer Service

Centre: csc@iec.ch.

A propos de l'IEC

La Commission Electrotechnique Internationale (IEC) est la première organisation mondiale qui élabore et publie des

Normes internationales pour tout ce qui a trait à l'électricité, à l'électronique et aux technologies apparentées.

A propos des publications IEC

Le contenu technique des publications IEC est constamment revu. Veuillez vous assurer que vous possédez l’édition la

plus récente, un corrigendum ou amendement peut avoir été publié.

Catalogue IEC - webstore.iec.ch/catalogue Electropedia - www.electropedia.org

Application autonome pour consulter tous les renseignements

Le premier dictionnaire en ligne de termes électroniques et

bibliographiques sur les Normes internationales,

électriques. Il contient plus de 30 000 termes et définitions en

Spécifications techniques, Rapports techniques et autres

anglais et en français, ainsi que les termes équivalents dans

documents de l'IEC. Disponible pour PC, Mac OS, tablettes

15 langues additionnelles. Egalement appelé Vocabulaire

Android et iPad.

Electrotechnique International (IEV) en ligne.

Recherche de publications IEC - www.iec.ch/searchpub

Glossaire IEC - std.iec.ch/glossary

La recherche avancée permet de trouver des publications IEC Plus de 60 000 entrées terminologiques électrotechniques, en

en utilisant différents critères (numéro de référence, texte, anglais et en français, extraites des articles Termes et

comité d’études,…). Elle donne aussi des informations sur les Définitions des publications IEC parues depuis 2002. Plus

projets et les publications remplacées ou retirées. certaines entrées antérieures extraites des publications des

CE 37, 77, 86 et CISPR de l'IEC.

IEC Just Published - webstore.iec.ch/justpublished

Service Clients - webstore.iec.ch/csc

Restez informé sur les nouvelles publications IEC. Just

Published détaille les nouvelles publications parues. Si vous désirez nous donner des commentaires sur cette

Disponible en ligne et aussi une fois par mois par email. publication ou si vous avez des questions contactez-nous:

csc@iec.ch.

IEC TS 62878-2-3 ®

Edition 1.0 2015-03

TECHNICAL

SPECIFICATION

SPECIFICATION

TECHNIQUE

colour

inside

Device embedded substrate –

Part 2-3: Guidelines – Design guide

Substrat avec appareil(s) intégré(s) –

Partie 2-3: Directives – Guide de conception

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION

ELECTROTECHNIQUE

INTERNATIONALE

ICS 31.180; 31.190 ISBN 978-2-8322-2403-8

– 2 – IEC TS 62878-2-3:2015 © IEC 2015

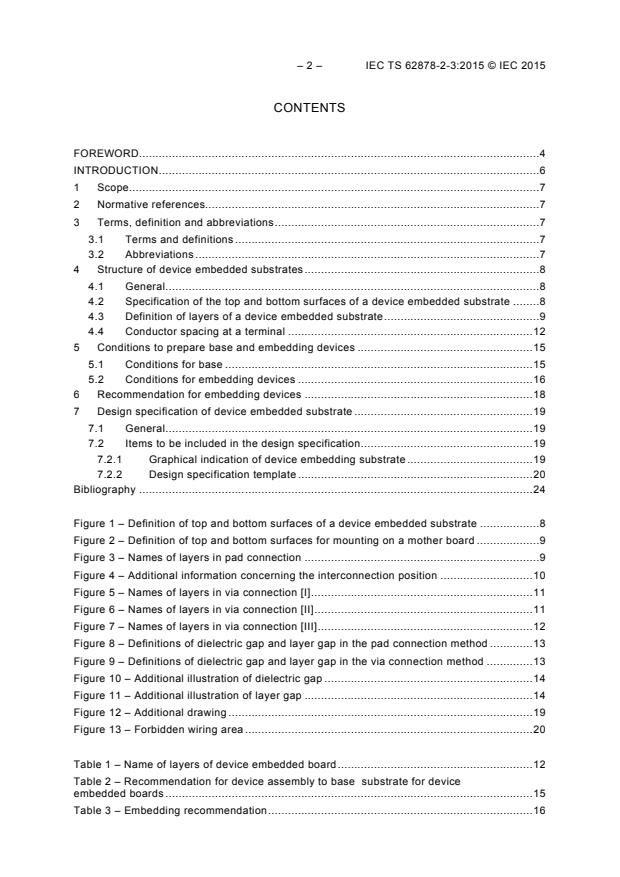

CONTENTS

FOREWORD . 4

INTRODUCTION . 6

1 Scope . 7

2 Normative references. 7

3 Terms, definition and abbreviations . 7

3.1 Terms and definitions . 7

3.2 Abbreviations . 7

4 Structure of device embedded substrates . 8

4.1 General . 8

4.2 Specification of the top and bottom surfaces of a device embedded substrate . 8

4.3 Definition of layers of a device embedded substrate . 9

4.4 Conductor spacing at a terminal . 12

5 Conditions to prepare base and embedding devices . 15

5.1 Conditions for base . 15

5.2 Conditions for embedding devices . 16

6 Recommendation for embedding devices . 18

7 Design specification of device embedded substrate . 19

7.1 General . 19

7.2 Items to be included in the design specification . 19

7.2.1 Graphical indication of device embedding substrate . 19

7.2.2 Design specification template . 20

Bibliography . 24

Figure 1 – Definition of top and bottom surfaces of a device embedded substrate . 8

Figure 2 – Definition of top and bottom surfaces for mounting on a mother board . 9

Figure 3 – Names of layers in pad connection . 9

Figure 4 – Additional information concerning the interconnection position . 10

Figure 5 – Names of layers in via connection [I] . 11

Figure 6 – Names of layers in via connection [II] . 11

Figure 7 – Names of layers in via connection [III] . 12

Figure 8 – Definitions of dielectric gap and layer gap in the pad connection method . 13

Figure 9 – Definitions of dielectric gap and layer gap in the via connection method . 13

Figure 10 – Additional illustration of dielectric gap . 14

Figure 11 – Additional illustration of layer gap . 14

Figure 12 – Additional drawing . 19

Figure 13 – Forbidden wiring area . 20

Table 1 – Name of layers of device embedded board . 12

Table 2 – Recommendation for device assembly to base substrate for device

embedded boards . 15

Table 3 – Embedding recommendation . 16

– 3 – IEC TS 62878-2-3:2015 © IEC 2015

Table 4 – Mounting methods of semiconductor devices . 17

Table 5 – Embedding device . 18

Table 6 – Specification of device embedded substrate 1 . 21

Table 7 – Specification of device embedded substrate 2 . 22

Table 8 – Specification of device embedded substrate 3 . 23

– 4 – IEC TS 62878-2-3:2015 © IEC 2015

INTERNATIONAL ELECTROTECHNICAL COMMISSION

____________

DEVICE EMBEDDED SUBSTRATE –

Part 2-3: Guidelines – Design guide

FOREWORD

1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising

all national electrotechnical committees (IEC National Committees). The object of IEC is to promote

international co-operation on all questions concerning standardization in the electrical and electronic fields. To

this end and in addition to other activities, IEC publishes International Standards, Technical Specifications,

Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as “IEC

Publication(s)”). Their preparation is entrusted to technical committees; any IEC National Committee interested

in the subject dealt with may participate in this preparatory work. International, governmental and non-

governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely

with the International Organization for Standardization (ISO) in accordance with conditions determined by

agreement between the two organizations.

2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international

consensus of opinion on the relevant subjects since each technical committee has representation from all

interested IEC National Committees.

3) IEC Publications have the form of recommendations for international use and are accepted by IEC National

Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC

Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any

misinterpretation by any end user.

4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications

transparently to the maximum extent possible in their national and regional publications. Any divergence

between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in

the latter.

5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity

assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any

services carried out by independent certification bodies.

6) All users should ensure that they have the latest edition of this publication.

7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and

members of its technical committees and IEC National Committees for any personal injury, property damage or

other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and

expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC

Publications.

8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is

indispensable for the correct application of this publication.

9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of

patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

The main task of IEC technical committees is to prepare International Standards. In

exceptional circumstances, a technical committee may propose the publication of a Technical

Specification when

• the required support cannot be obtained for the publication of an International Standard,

despite repeated efforts, or

• the subject is still under technical development or where, for any other reason, there is the

future but no immediate possibility of an agreement on an International Standard.

Technical Specifications are subject to review within three years of publication to decide

whether they can be transformed into International Standards.

IEC TS 62878-2-3, which is a Technical Specification, has been prepared by IEC technical

committee 91: Electronics assembly technology.

– 5 – IEC TS 62878-2-3:2015 © IEC 2015

The text of this Technical Specification is based on the following documents:

Enquiry draft Report on voting

91/1143/DTS 91/1164A/RVC

Full information on the voting for the approval of this Technical Specification can be found in

the report on voting indicated in the above table.

A list of all parts in the IEC 62878 series, published under the general title Device embedded

substrate, can be found on the IEC website.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

The committee has decided that the contents of this publication will remain unchanged until

the stability date indicated on the IEC website under "http://webstore.iec.ch" in the data

related to the specific publication. At this date, the publication will be

• transformed into an International standard,

• reconfirmed,

• withdrawn,

• replaced by a revised edition, or

• amended.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates

that it contains colours which are considered to be useful for the correct

understanding of its contents. Users should therefore print this document using a

colour printer.

– 6 – IEC TS 62878-2-3:2015 © IEC 2015

INTRODUCTION

This part of IEC 62878 provides guidance with respect to device embedded substrate,

fabricated by embedding discrete active and passive electronic devices into one or multiple

inner layers of a substrate with electric connections by means of vias, conductor plating,

conductive paste, and printing. Within the IEC 62878 series,

• IEC 62878-1-1 specifies the test methods,

• IEC TS 62878-2-1 gives a general description of the technology,

• IEC TS 62878-2-3, provides guidance on design, and

• IEC TS 62878-2-4 specifies the test element groups.

The device embedded substrate may be used as a substrate to mount SMDs to form

electronic circuits, as conductor and insulator layers may be formed after embedding

electronic devices.

The purpose of the IEC 62878 series is to achieve a common understanding with respect to

structures, test methods, design and fabrication processes and the use of the device

embedded substrate in industry.

– 7 – IEC TS 62878-2-3:2015 © IEC 2015

DEVICE EMBEDDED SUBSTRATE –

Part 2-3: Guidelines – Design guide

1 Scope

This part of IEC 62878 describes the design guide of device embedded substrates.

The design guide of device embedded substrate is essentially the same as that of various

electronic circuit boards. This part of IEC 62878 enables a thorough understanding of circuit

design, structure design, board design, board manufacturing, jisso (assembly processes) and

tests of products.

This part of IEC 62878 is applicable to device embedded substrates fabricated by use of

organic base material, which include for example active or passive devices, discrete

components formed in the fabrication process of electronic wiring board, and sheet formed

components.

The IEC 62878 series neither applies to the re-distribution layer (RDL) nor to the electronic

modules defined as an M-type business model in IEC 62421.

2 Normative references

The following documents, in whole or in part, are normatively referenced in this document and

are indispensable for its application. For dated references, only the edition cited applies. For

undated references, the latest edition of the referenced document (including any

amendments) applies.

IEC 60194, Printed board design, manufacture and assembly – Terms and definitions

3 Terms, definition and abbreviations

3.1 Terms and definitions

For the purposes of this document, the terms and definitions given in IEC 60194 apply.

3.2 Abbreviations

AABUS as agreed between user and supplier

BGA ball grid array

IPD integrated passive device

LGA land grid array

LSI large scale integration

MEMS micro electro mechanical systems

OSP organic solderability preservative

SMD surface mount device

TAB tape automated bonding

WLP wafer level package

– 8 – IEC TS 62878-2-3:2015 © IEC 2015

4 Structure of device embedded substrates

4.1 General

The name of each part of a device embedded substrate is specified in Clause 4 to assist

technical understanding of the structure and to avoid misinterpretation by engineers working

in the relevant industry sectors.

4.2 Specification of the top and bottom surfaces of a device embedded substrate

The definition of the top and bottom surfaces of a device embedded substrate depends on the

number of devices mounted on the surface of the substrate, as shown in Figure 1. The

surface on which more components are mounted is the top surface. If a substrate is mounted

on a printed wiring board (hereafter referred to as mother board), the surface of the substrate

connecting to the wiring board is defined as the bottom surface even if it contains more

input/output terminals (pads) (see Figure 2). If the design of the top and bottom surfaces has

been AABUS, this agreement takes priority, even if it differs from the definition stated in this

part of IEC 62878.

IEC

Figure 1 – Definition of top and bottom surfaces of a device embedded substrate

– 9 – IEC TS 62878-2-3:2015 © IEC 2015

IEC

Figure 2 – Definition of top and bottom surfaces for mounting on a mother board

4.3 Definition of layers of a device embedded substrate

Names and symbols of layers in a device embedded board are illustrated in Figure 3. Each

layer is numbered as L1, L2 to L6 (in case of 6 layers) from the top surface. The number

indicates the order of the layer with respect to the top surface.

C

A

L1

L2

L3

B

L4

L5

L6

IEC

D

Key

A Embedded component C Top surface

B Base D Bottom surface

Figure 3 – Names of layers in pad connection

In the case of via connection, the position of connecting terminals of the embedded device is

different from the surrounding layer number. The component symbol and connecting

position(s) are defined as illustrated in Figure 4 in order to clarify the interconnecting

positions of the embedded device and of its electrical terminals with respect to construction

design, pattern design, board fabrication and jisso (assembly).

It is recommended to use the component symbols and names as shown in a circuit diagram to

use 2 to 4 indications. The position of interconnection in the case of die-bonding or mounting

– 10 – IEC TS 62878-2-3:2015 © IEC 2015

of a device embedded device may be expressed using another name in addition to the name

of the layer in which the device is embedded.

The surface of a device is upward facing. Use upward (U) when connecting terminals are in

the upward facing surface, and downward (D) when the terminals are in the downward facing

surface.

A three digit number is used if multiple components are embedded and/or multiple connection

terminals are in the same layer. The left side number indicates the interconnecting layer

number and the right side number indicates the layer position of the embedded component. If

there are multiple layers involved, numbers 1, 2 indicate the layers from the top for upward

and numbers 1, 2 indicate the layers from the bottom for downward. The second number may

be omitted if there is only one embedded component in a layer. See the example in Figure 4.

Figure 4 shows additional information on the interconnection position. The active device is

mounted on the L2 layer and connected to the first layer with upward direction. In this case

the name of the interconnection layer is expressed as L2-U11. The last digit 1 indicates the

number of the embedded component. Passive components mounted on the L5 layer are

connected to L6 with downward direction. In this case, the name of the interconnection layer

is expressed as L5-D61.

A virtual layer is used as a virtual conductor layer and as the connecting points. The terminal

connection design of an embedded device is carried out by first establishing the connection

and hole machining data A and B, then the connection and hole machining data C and D for

L2 and L5 (in the case of the above structure). The terminal setting may be omitted if a via

connection and the positions of embedded device terminals and the conduction layer are the

same.

H

J

B

A

E

L1

F=L2-U11

L2

L3

D

L4

L5

G=L5-D61

L6

C

B

K

I

IEC

A Embedded active device G Name of the layer between L5 and L6

B Connecting terminal H Connection and machining data from L1 to a

virtual layer (L2-U11)

C Embedded passive device I Connection and machining data from L6 to a

virtual layer (L5-D61)

D Base J Connection and machining data from L1 to

L2

E Terminal position K Connection and machining data from L6 to

L5

F Name of the layer between L1 and L2

Figure 4 – Additional information concerning the interconnection position

Figure 5 shows the interconnection position. Active device (xxxx) is mounted on the L2 layer

and connected to the first layer with upward direction. In this case, the name of the

interconnection position is expressed as xxxx-L2-U11. Passive components (yyyy) mounted

– 11 – IEC TS 62878-2-3:2015 © IEC 2015

on the L5 layer are connected to L6 with downward direction. In this case, the name of the

interconnection position is expressed as yyyy-L5-D61.

A

L1

L2-U11

L2

L3

C

L4

L5

L5-D61

L6

B

IEC

A Embedded active device C Base

B Embedded passive device

Figure 5 – Names of layers in via connection [I]

Figure 6 shows a chip-stacked case. Active device 2 (xxx2) is mounted on the L2 layer and

active device 1 (xxx1) is stacked on active device 2. Both are connected to the L1 layer with

upward direction. In this case the name of the interconnection position of active device 2 is

expressed as xxx2-L2-U122. The name of the interconnection position of active device 1 is

expressed as xxx1-L2-U121. The second digit from the right (2) shows the number of the

embedded device.

A

B

L1

L2-U121

L2-U122

L2

L3

D

L4

L5

L5-D61

L6

C

IEC

A Embedded active device 1 C Embedded passive device

B Embedded active device 2 D Base

Figure 6 – Names of layers in via connection [II]

Figure 7 shows the interconnection position of an active device having multilayer connecting

pads. Active device (xxxx) is mounted and connected to the L5 layer and pads on the other

side are connected to the L1 layer with upward direction. Therefore, in this case, the name of

the interconnection position of the active device is expressed as xxxx-L5-U11.

– 12 – IEC TS 62878-2-3:2015 © IEC 2015

IEC

A Embedded active device

B Base

C Conductor layer in embedding layer

Figure 7 – Names of layers in via connection [III]

The content of Figure 4 toFigure 7 is summarized in Table 1.

Table 1 – Name of layers of device embedded board

Embedded device Embedding and connection of embedded device

No. of

Example

Component Terminal

components

Device Layer Layer

number direction

No. Layer

Active - A12 - L2 - U 1 1 Omit

Figure 4

Passive - 1 - L5 - D 6 1 Omit

Active - A13 - L2 - U 1 1 Omit

Figure 5

Passive - 2 - L5 - D 6 1 Omit

Active - A13 - L2 - U 1 2 1

IPD - 4 - L2 - U 1 2 2

Figure 6

Capacit - 1 - L5 - D 6 1 Omit

or

- 12 - L2 - U 1 1 Omit

IPD,

Figure 7

etc.

- B1 - L6 - D 6 1 Omit

Information on embedded components is necessary in embedded board design.

For example, in Figure 4 the interconnection position of active device A12 is expressed as A12-L2-U11.

4.4 Conductor spacing at a terminal

Subclause 4.4 defines the insulation layer thickness, the conductor spacing and the distance

between electrode and conductor spacing at a terminal. Conductor spacing is hereafter

referred to as electrode.

The insulation layer thickness and the distance between each conductive layer are defined

with respect to the position of each layer, as follows:

a) The insulation layer thickness is defined as the layer separating the conductors. The

thickness is not the thickness of each layer to be laminated but the thickness of the actual

insulation layer of the substrate.

b) The conductor spacing is defined as the distance between conductors formed on one layer.

c) The spacing between the electrode and conductor is the thickness of the insulator

between the terminals of the embedding device and the conductor layer to be connected.

– 13 – IEC TS 62878-2-3:2015 © IEC 2015

d) The following terms are used to indicate each distance:

1) insulation layer thickness DG1 (dielectric gap);

2) spacing between conductor layers LG1 (layer gap);

3) spacing between terminal and conductor EG11 (device embedding gap).

The number used in the indication is the number of layers. The left number in 3) designates

the conductor layer and the number on the right shows the step (first, second, etc.) of multi-

device embedding into the substrate. See 4.3 for the definition of steps (layers).

Figure 8 and Figure 9 show definition of layers of a device embedded substrate for pad and

via connections. Additional remarks are added to Figure 10 and Figure 11 for dielectric gap,

layer gap and device embedding gap.

TTTererermmmiiinalnalnal EEEmmmbebebedded devdded devdded deviiiccceee

L1L1L1

LGLGLG111

DGDGDG111

L2L2L2

LGLGLG222

DGDGDG222

L3L3L3

LGLGLG333 DGDGDG333

L4L4L4

DGDGDG444

LGLGLG444

L5L5L5

DGDGDG555

LGLGLG555

L6L6L6

IEC

Figure 8 – Definitions of dielectric gap and layer gap in the pad connection method

IEC

Figure 9 – Definitions of dielectric gap and layer gap in the via connection method

– 14 – IEC TS 62878-2-3:2015 © IEC 2015

Figure 10 indicates structure of insulation layer prior to the lamination. The active device is

embedded in the insulation layer DG1. DG51 indicates the minimum thickness of the

insulation layer in DG5.

IEC

Figure 10 – Additional illustration of dielectric gap

Figure 11 shows conductor gap and electrode/connector gap. EG11 indicates the insulation

gap between non-attached pads of the embedded active device to the conductor of the outer-

layer. EG41 indicates the insulation gap between L4 and L5.

IEC

Figure 11 – Additional illustration of layer gap

– 15 – IEC TS 62878-2-3:2015 © IEC 2015

5 Conditions to prepare base and embedding devices

5.1 Conditions for base

Base board and assembly conditions are given in Table 2.

Table 2 – Recommendation for device assembly to base

substrate for device embedded boards

Item Condition Remarks

Base Base material Organic: FR-4, FR-5, BT resin, polyimide, PPE, Copper foil carrier,

PTFE metal heat fin for

heat radiation, film

Board structure Single sided, double sided, multilayer, build-up

type carrier,

multilayer, single-sided flexible, double-sided

silicon interposer

flexible, multilayer flexible, electronic circuit

substrate

Number of layers 1 layer, 2 layers, …, arbitrary number of layers

Copper foil

5 µm, 9 µm, 12 µm, 18 µm, 35 µm, 70 µm

Insulator > 10 µm

Maximum size Variable based on

610 mm × 510 mm

the capability of

Minimum size 340 mm × 250 mm

die bonder and/or

chip mounter

Embedded layer Insulation material Prepreg such as FR-4, FR-5, BT resin, A cut-off may be

polyimide, PPE, PTFE (B stage type) required for a thick

embedding device

Resin such as FR-4, FR-5, BT resin, polyimide,

etc.

Sealing resin used for semiconductor packages

Others

Number of layers 1 layer, 2 layers, …, arbitrary number of layers

Copper foil 5 µm, 9 µm, 12 µm, 18 µm, 35 µm, 70 µm

Board size Depends on the base size

Condition Die bonder A carrier may be

Maximum: 330 mm × 250 mm × 2,5 mm

necessary if the

Minimum: 50 mm × 50 mm × 0,5 mm

thickness is less

than 0,3 mm

Mounter

Maximum: 510 mm × 460 mm × 4,0 mm

Minimum: 50 mm × 50 mm × 0,3 mm

Fiducial mark Fiducial mark shall be in accordance with

customers' process capabilities

Position accuracy To be agreed by customer based materials and

process capabilities

Condition for Die bonder

Maximum: 25 mm × 25 mm × 0,5 mm

sheet components

Minimum: 0,25 mm × 0,25 mm × 0,1 mm

Mounter

Maximum: 24 mm × 24 mm × 6,5 mm

Minimum: 0,4 mm × 0,2 mm × 0,12 mm

Thermal resistance Withstand for 120 min at 180 °C

Resistance to 3 MPa to 4 MPa

pressure

Resistance to To be agreed by customer based materials and

chemical solvent process capabilities

The above assembly recommendations are for reference purposes for the committee drafting the standard for

device embedding substrate. Actual recommendations shall be AABUS.

Pad bonding Via bonding

– 16 – IEC TS 62878-2-3:2015 © IEC 2015

5.2 Conditions for embedding devices

Work panel size, panel thickness and embedding condition are shown in Table 3 when

automatic device embedding equipment is used.

Table 3 – Embedding recommendation

Assembly Device Connection Direction Panel size Thickness Fiducial

a

(to mm mm

mark

embedded

Max. Min. Max. Min.

terminals)

WB 267×90 90×15 0,9 0,1 ―

Die

Bare die Up

bonding

TAB ― ― ― ― ―

US 330×250 50×50 2,5 0,5 *1

330×250 50×50 2,5 0,5 *1

C4 *4

4,0 0,3 *2

510×460 50×50

GBS

Mounting Bare die FC Down

ESC,

ESC5

330×250 50×50 2,5 0,5 *1

ACF(P)

NCF(P)

Others ― ― ― ― ―

WLP

Reflow

Down

Rectangular

Resin

chip

bonding

Mounting 4,0 0,3 *2

510×460 50×50

Rod ―

Module

Reflow Down

MEMS

Bare die

Die

310×215 50×30 3,0 0,1 *3

bonding

WLP

Copper

plating

Mounting Rectangular

Up

Conductive

chip

paste

4,0 0,3 *2

510×460 50×50

Module

MEMS

The above assembly recommendations are for reference purposes for the committee drafting the standard for

device embedded substrate. Actual recommendations shall be AABUS.

NOTE *4 (C4): on upper layer for terminal pitch ≧ 0,3 mm, on lower layer for terminal pitch > 0.3 mm.

a

Size and shape of fiducial mark:

Size — *1: 0,25 mm to 0,8 mm; *2: 0,5 mm to 1.6 mm; *3: 0,2 mm to 1,6 mm

Shape — circle, cross, square

– 17 – IEC TS 62878-2-3:2015 © IEC 2015

Table 4 shows the embedding methods of semiconductor devices and electronic devices.

Table 4 – Mounting methods of semiconductor devices

Method Schematic diagram Abbrevi- Name Explanation

ation

Metal US Ultra sonic Ultrasonic energy is applied

UUllttrrasasound cound cononnecnecttiionon

UUndernderffiillll

bonding bonding between semiconductor

terminal (bump) and board

electrode to metal bond and

then underfill thermosetting

resin for mechanical

reinforcement. Gold is often

used for the bumps and

connecting pads of the

board.

C4 Controlled Reflow solder bumps LSI

Solder bump, reflow soldering

collapse chip with high temperature solder

connection and underfill resin after

cleaning the joints. Solder

pre-coat, gold plating, OSP

are used.

GBS Gold bump LSI with Au bumps are

AAu bumu bump,p, r refefllowow ssololderderiingng

soldering pressed to board with solder

pre-coated pads and heated

to bond the junctions, then

underfill to mechanical

reinforcement curing

ESC5 Epoxy Use solder powder mixed

RResesiin wn wiitth sh sololderder po powwderder

thermosetting adhesive and

encapsulated

solder press and heat to bond the

connection 5th device to board. Gold plating

or OSP are used for the pads

of board.

ESC Epoxy Thermosetting resin is used

AAu bumu bump,p, s sololderder pr pree--ccoatoat

encapsulated between LSI bumps and

solder solder pre-coated board

connection pads. Press and heat to

establish electrical

interconnection.

Compression NCF (P) Non conductive Thermosetting resin is used

AAu bumu bump prp presesssed ced conneconnecttiionon

bonding film (paste) between LSI Au bumps and

board pads. Press and heat

to establish electrical

interconnection. Gold plating

is usually used for pads on

board.

RResesiin wn wiitth ch conduconducttiivve e

ACF (P) Anisotropic Thermosetting resin mixed

mmeettalal powpowderder

conductive film with conductive powder is

(paste) applied to the connecting

electrodes and then pressed

and heated to obtain

electrical connection. Au

plating is usually used for

pads on board.

Reflow — Soldering Bonding by reflow soldering.

SSololderder pas pastte re refefllooww

It is necessary to wash out

all flux used in reflow

soldering.

Pad bonding Via bonding

– 18 – IEC TS 62878-2-3:2015 © IEC 2015

Method Schematic diagram Initial Name Explanation

— Solder-resin Use solder powder mixed

RResesiin wn wiitth sh sololderder po powwderder

bonding adhesive and reflow to bond

the device to board.

Resin

RResesiin wn wiitth h — Conductive Use conductive thermosetting

adhesive bonding adhesive and cure the resin

cconduconducttiivve pe powowderder

after mounting a device on a

board to attain electrical

conduction

6 Recommendation for embedding devices

Conditions for embedding device are given in Table 5 and shall be AABUS in actual

application.

Table 5 – Embedding device

Assembly Device Connection Component size

Terminal

(l×w×h)

direction (to

mm

mounting

face)

max. min.

WB Up 25×25×0,5 0,25×0,25×0,1

Die

Bare die

bonding

TAB Up

US Down 10×10×0,5 3,0×3,0×0,1

C4 *4 Down

GBS Down

Mounting Bare die FC

ESC, ESC5 Down 20×20×0,5 1,0×1,0×0,1

ACF(P) Down

NCF(P) Down

Others Down

Reflow

WLP Down 24×24×6,5 0,4×0,2×0,12

Resin bonding

Rectangular Reflow

Down

62×45 0,4×0,2

Resin bonding

Mounting

Rod Reflow

― 62×45 16×08

Resin bonding

Module

Reflow Down

24×24×6,5 0,4×0,2×0,12

MEMS

Copper plating

Bare die Up 25×25×0,5 0,25×0,25×0,1

Conductive paste

Die

bonding

Copper plating

WLP Up 25×25×0,5 0,25×0,25×0,1

Conductive paste

Copper plating

Mounting Rectangular Up

62×45 0,4×0,2

Conductive paste

The above assembly recommendations are for reference purposes for the committee drafting the standard for

device embedded substrate. Actual recommendations shall be AABUS.

– 19 – IEC TS 62878-2-3:2015 © IEC 2015

7 Design specification of device embedded substrate

7.1 General

In general, the term “design” has broad meanings. In order to avoid misunderstanding and

confusion, it is recommended to include the follow items in the design specification:

a) circuit design;

b) structure design;

c) device embedding board design;

d) circuit pattern design.

7.2 Items to be included in the design specification

7.2.1 Graphical indication of device embedding substrate

The following indications shall be stated:

a) Indication of external form of device embedded substrate, of design drawing and of CAD

data is as follows. A perspective drawing seen from the top or bottom surface is used.

State if the drawing is seen from top or bottom.

Example: A top perspective or bottom perspective drawing is shown in Figure 12.

It is recommended to clarify the position of the relevant layer in the cross section drawing.

PPererssppececttiivve ve viiewew f frromom t toop (p (LL1)1)

[[LL11]]

L1L1L1

L2L2L2---U1U1U1111

[[LL22]]

L2L2L2

[[LL33]]

L3L3L3

L4L4L4

[[LL44]]

L5L5L5

[[LL55]]

L5L5L5---D6D6D6111

L6L6L6

[[LL66]]

IEC

Figure 12 – Additional drawing

b) List of parts of device embedded substrate and items to be stated:

1) device name, device number, name of manufacturer;

2) possibility of embedding (if not possible, embedding inside of substrate or surface

mounting, etc.);

3) table of parts of device embedded substrate and its structure.

c) Organization and structure of device embedded substrate:

1) entire organization and structure of device embedded substrate;

2) number of layers and types of electronic circuit board;

3) thickness of each conductor layer (copper foil + copper plating, etc.);

4) distance between insulating layers, and between the conductor and insulating layers;

– 20 – IEC TS 62878-2-3:2015 © IEC 2015

5) position of layer where device is to be embedded;

6) forbidden area(s) for wiring in each layer as illustrated in Figure 13;

7) thickness of the layer to embedded device(s).

d) Specification of device embedded substrate:

1) size and thickness of the substrate;

2) treatment to the surface where the device is not embedded (embedding on one side

only);

3) methods of embedding and connection to the device;

4) surface treatment to conductor surface (solder flux, gold plating, etc.).

e) Embedding:

1) die bonding;

2) methods of mounting and interconnection;

3) special treatment:

• underfill;

• resin mold;

• potting;

• others.

IEC

Figure 13 – Forbidden wiring area

f) Specification of device embedding:

1) embedding (resin embedding, stacking, etc.);

2) embedding material (resin, prepreg, etc.);

3) embedding conditions (heating, temperature, pressure, etc.);

4) mechanical loading condition.

Embedding condition shall be AABUS.

g) Design specification of electronic circuit board (pattern design).

The design principle of conductor gap, via diameter, via land diameter, etc. is basically the

same as for regular PWB. Details of design specification are to be AABUS.

7.2.2 Design specification template

Table 6 to Table 8 show the template of a design specification.

Table 6 is an example of a specification of a device embedded substrate.

– 21 – IEC TS 62878-2-3:2015 © IEC 2015

Table 6 – Specification of device embedded substrate 1

List of embedded devices

No. Device Name Device # Manufacturer Manufacturer Specification of Remarks

embedding device

Shall Yes No Or

Case 1 Memory

D-RAM MIC-002 TM-DRAM02 T ○

IC

Case 2 Stacked Chip C

CC-003 CCK-5V10 M ○

capacitor

Case 3 Stacked Electrolytic Low heat

DC-004 DCK-5V200 P ○

capacitor C resistance

Device embedded substrate – Construction and structure

Layer # 6 Base 4 Device

Dielectric

Layer and its thickness Layer gap embedded

gap

Type Build-up layer

gap

Embe

Conductor

N° dding

Embedding layer L2、L5

µm

layer

Lay t t t

Name Name Name

er µm µm µm

Construction and structure

Copper Copper

foil plating

- - - - - -

1 L1 12 20 -

DG1 138 LG1 100 EG11 40

2 L2 18 20 ○

DG2 73 LG2 40 - -

3 L3 18 15 -

DG3 80 LG3 80 - -

4 L4 18 15 -

DG4 73 LG4 40 EG41 40

5 L5 18 20 ○

DG-5 138 LG5 100 EG61 40

NOTE Magnifications are

different for vertical and 6 L6 12 20 -

- - - - - -

horizontal directions.

Substrate thickness (exclude solder resist)

0,57

mm

Table 7and Table 8 are examples of specifications of device embedded substrate

– 22 – IEC TS 62878-2-3:2015 © IEC 2015

Table 7 – Specification of device embedded substrate 2

Specification of device embedded substrate

Placement of embedded device and condition NO Item Specification

1 Device Layers 4 layers

FFididuucciaial ml maarrkk

SSpecpeciiffiiccatatiionon

embedded

ofof eaeacch sh seeccttiionon

Size

W: 250 mm × L: 320 mm

ofof eaeacch sh seeccttiionon

substrate

Thickness t = 0,2 mm

2 Embedding surface Double/single side

3 Treatment of back □ with pattern formation

surface

□ without pattern

in single-side embedding

formation

4 Embedding method □ Die bonding

□ Mounting

□ Others

5 Interconnection □ Via connection (Cu

plating)

□ Cu plating

□ Conductive paste

□ Others

FFididuucciaial ml maarrkk

□ Pad connection

FFororbibiddedden arn areea a

ofof t thhe se sheetheet FFididuucciaial hl hoolele

□ Cu plating

ffoorr as asssememblblyy

□ Conductive paste

□ Others

□ Others

6 Solder resist □ Yes □ No

7 Surface treatment □ Flux

□ Anti-rust treatment

□ Other

8 Reference hole □ Yes □ No

9 Fiducial mark □ Yes □ No

10 Bending after ±0,5

embedding %

11 Others

– 23 – IEC TS 62878-2-3:2015 © IEC 2015

Table 8 – Specification of device embedded substrate 3

Specification of device embedded substrate

Construction of device embedding and condition No. Item Specification

1 Structure 1 Assembly □ Die bonding

□ Adhesives

□ Others

□ Mounting

□ Soldering

□ Conductive paste

□ Others

□ Special

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...