ISO/IEC 14576:1999

(Main)Information technology - Synchronous split transfer type system bus (STbus) - Logical layer

Information technology - Synchronous split transfer type system bus (STbus) - Logical layer

This International Standard specifies the logical specifications of STbus which is a high-performance and highly reliable system bus. STbus adopts a synchronous transfer method with a high-speed clock and a split transfer method enabling to minimize bus holding time during one bus operation and to use a bus efficiently. This International Standard is applicable to a high-performance system bus or an I/O bus in a multiprocessor system. Typical STbus applications are a system bus and an I/O bus in a tightly coupled multiprocessor system, and a system bus in a loosely coupled multiprocessor system.

General Information

- Status

- Published

- Publication Date

- 15-Dec-1999

- Technical Committee

- ISO/IEC JTC 1/SC 25 - Interconnection of information technology equipment

- Current Stage

- PPUB - Publication issued

- Start Date

- 16-Dec-1999

- Completion Date

- 29-Feb-2000

Overview

ISO/IEC 14576:1999 defines the logical layer for the Synchronous Split Transfer type system bus (STbus). The standard specifies the protocol and logical interface for a high-performance, highly reliable system bus that uses a synchronous high-speed clock and a split transfer approach to minimize bus holding time and improve bus utilization. It is intended for use as a system or I/O bus in tightly coupled (TCMP) and loosely coupled (LCMP) multiprocessor systems.

Key topics and technical requirements

- Interface signals: Defines basic and optional bus interface signals and their semantics to ensure interoperability between function units.

- Bus operations and transfer protocol: Detailed command formats, transfer sequences, pipeline behavior, and arbitration mechanisms for bus masters and slaves.

- Data transfer types: Procedures for memory read/write, control space access, message transfer, and control register access.

- Cache coherency control: Specifies copyback and write-through coherency methods, cache block attributes (block size limited to 32 bytes), cache invalidation, retry indication, steal and steal-inhibit operations, and state transitions (I, SU, EM).

- Lock and synchronization operations: Support for lock transfer and related sequences to coordinate multiprocessor access.

- Error handling and reliability: Parity conventions (odd parity), error-reporting in answer transactions, fault detection methods, redundancy approaches and mechanisms to prevent fault propagation and support diagnosis.

- Auxiliary material: Informative annexes with performance estimates and lock/copyback interaction examples.

Applications and practical value

ISO/IEC 14576 (STbus logical layer) is practical for:

- Designing system buses and I/O buses in multiprocessor systems where low-latency, high-throughput shared access is required.

- Implementing cache-coherent multiprocessor platforms (both tightly and loosely coupled) that require well-defined copyback coherency and retry semantics.

- Hardware architects and SoC designers who need a standardized bus protocol for interoperability between CPUs, memory controllers, I/O adapters and bus handlers.

- Firmware and system integrators implementing bus arbitration, lock semantics, and error recovery consistent with international practice.

- Test, validation and verification teams evaluating bus protocol compliance, performance, and fault-handling behavior.

Who should use this standard

- Hardware architects and engineers designing multiprocessor boards and bus fabrics

- System integrators and OEMs building scalable CPU/memory/I/O subsystems

- Firmware developers implementing low-level bus protocols and coherency support

- Test engineers and compliance labs validating bus implementations

Related standards

ISO/IEC 14576 was prepared within ISO/IEC JTC 1 (microprocessor systems). Users will often consult other JTC 1 documents and industry bus-interface standards when designing complete hardware/software stacks to ensure broader interoperability and system integration.

Get Certified

Connect with accredited certification bodies for this standard

BSI Group

BSI (British Standards Institution) is the business standards company that helps organizations make excellence a habit.

NYCE

Mexican standards and certification body.

Sponsored listings

Frequently Asked Questions

ISO/IEC 14576:1999 is a standard published by the International Electrotechnical Commission (IEC). Its full title is "Information technology - Synchronous split transfer type system bus (STbus) - Logical layer". This standard covers: This International Standard specifies the logical specifications of STbus which is a high-performance and highly reliable system bus. STbus adopts a synchronous transfer method with a high-speed clock and a split transfer method enabling to minimize bus holding time during one bus operation and to use a bus efficiently. This International Standard is applicable to a high-performance system bus or an I/O bus in a multiprocessor system. Typical STbus applications are a system bus and an I/O bus in a tightly coupled multiprocessor system, and a system bus in a loosely coupled multiprocessor system.

This International Standard specifies the logical specifications of STbus which is a high-performance and highly reliable system bus. STbus adopts a synchronous transfer method with a high-speed clock and a split transfer method enabling to minimize bus holding time during one bus operation and to use a bus efficiently. This International Standard is applicable to a high-performance system bus or an I/O bus in a multiprocessor system. Typical STbus applications are a system bus and an I/O bus in a tightly coupled multiprocessor system, and a system bus in a loosely coupled multiprocessor system.

ISO/IEC 14576:1999 is classified under the following ICS (International Classification for Standards) categories: 35.160 - Microprocessor systems. The ICS classification helps identify the subject area and facilitates finding related standards.

ISO/IEC 14576:1999 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

INTERNATIONAL ISO/IEC

STANDARD

First edition

1999-12

Information technology –

Synchronous split transfer type system bus

(STbus) – Logical layer

Technologies de l'information –

Bus de système de transfert de fente synchrone (STbus) –

Couche logique

Reference number

INTERNATIONAL ISO/IEC

STANDARD

First edition

1999-12

Information technology –

Synchronous split transfer type system bus

(STbus) – Logical layer

Technologies de l'information –

Bus de système de transfert de fente synchrone (STbus) –

Couche logique

ISO/IEC 1999

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any

means, electronic or mechanical, including photocopying and microfilm, without permission in writing from the publisher.

ISO/IEC Copyright Office Case postale 56 CH-1211 Genève 20 Switzerland

•

PRICE CODE

X

For price, see current catalogue

– ii – 14576 © ISO/IEC:1999(E)

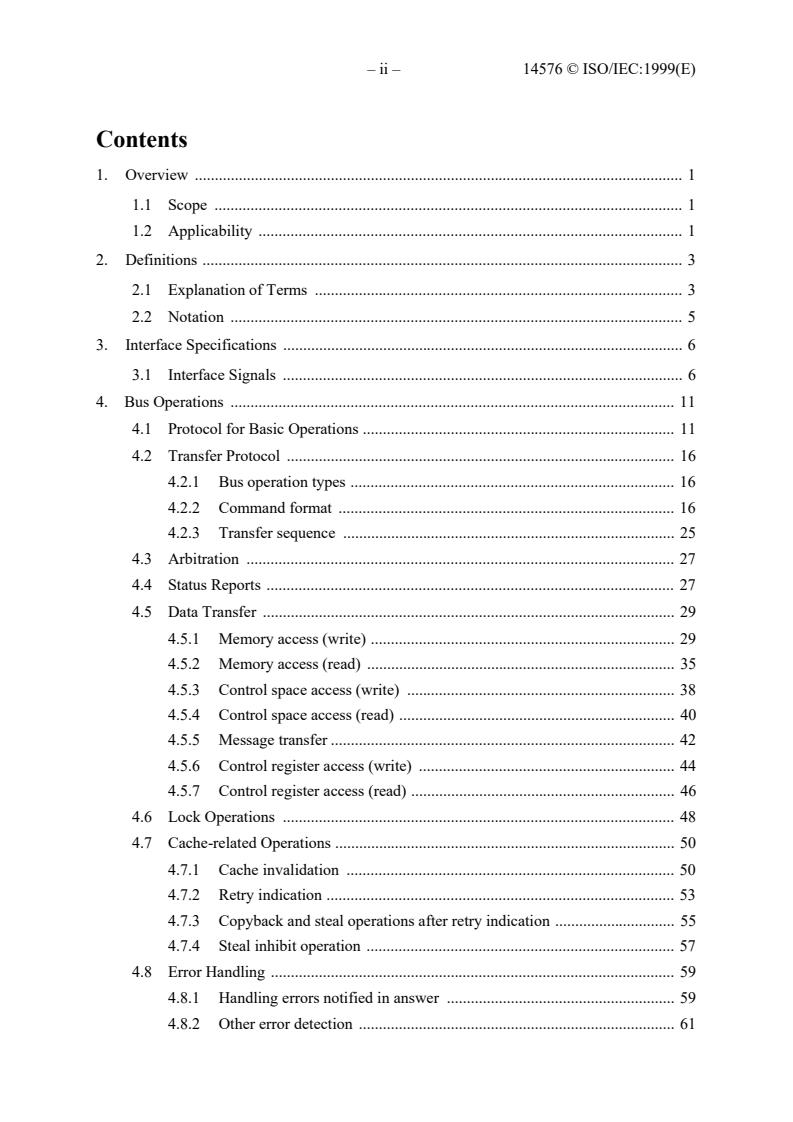

Contents

1. Overview . 1

1.1 Scope . 1

1.2 Applicability . 1

2. Definitions . 3

2.1 Explanation of Terms . 3

2.2 Notation . 5

3. Interface Specifications . 6

3.1 Interface Signals . 6

4. Bus Operations . 11

4.1 Protocol for Basic Operations . 11

4.2 Transfer Protocol . 16

4.2.1 Bus operation types . 16

4.2.2 Command format . 16

4.2.3 Transfer sequence . 25

4.3 Arbitration . 27

4.4 Status Reports . 27

4.5 Data Transfer . 29

4.5.1 Memory access (write) . 29

4.5.2 Memory access (read) . 35

4.5.3 Control space access (write) . 38

4.5.4 Control space access (read) . 40

4.5.5 Message transfer . 42

4.5.6 Control register access (write) . 44

4.5.7 Control register access (read) . 46

4.6 Lock Operations . 48

4.7 Cache-related Operations . 50

4.7.1 Cache invalidation . 50

4.7.2 Retry indication . 53

4.7.3 Copyback and steal operations after retry indication . 55

4.7.4 Steal inhibit operation . 57

4.8 Error Handling . 59

4.8.1 Handling errors notified in answer . 59

4.8.2 Other error detection . 61

14576 © ISO/IEC:1999(E) – iii –

5. Cache Coherency Control . 62

5.1 Cache Control Methods . 62

5.2 Cache Block Attributes . 62

5.3 Operations on System Bus . 63

5.4 Retry Indication . 65

5.5 Steal Operation . 66

5.6 Cache Data Management and State Transition . 67

5.6.1 Write-through cache . 67

5.6.2 Copyback cache . 70

5.7 Notes on Memory Access . 75

6. Functions for Enhanced Reliability . 76

6.1 Redundancy . 76

6.2 Detecting Faults . 77

6.3 Preventing Faults from Spreading . 77

6.4 Supporting Fault Handling and Diagnosis . 78

Annex A (informative) Performance (Estimated) . 79

Annex B (informative) Return of answer in a lock transfer .80

Annex C (informative) Lock transfer and write back of copyback cache .81

– iv – 14576 © ISO/IEC:1999(E)

Figures

Figure 1 - STbus Applications .2

Figure 2 - Connection interface between function units (basic pattern) .7

Figure 3 - Concept of bus operation protocol (for 1-cycle or 2-cycle transfer:

8-byte bus width specification, write operation) .11

Figure 4 - Concept of bus operation protocol (for transfer of 3-cycles or more:

8-byte bus width specification, read operation) .13

Figure 5 - Concept of bus operation protocol (for 1-cycle or 2-cycle transfer:

4-byte bus width specification, write operation) .15

Figure 6 - Pipeline operation.20

Figure 7 - BCT field.21

Figure 8 - RA and byte alignment.23

Figure 9 a) - One-word memory write (no-answer transaction) .31

Figure 9 b) - One-word memory write (basic transaction).32

Figure 9 c) - n-word memory write (no-answer transaction) .33

Figure 9 d) - n-word memory write (basic transaction) .34

Figure 10 a) - One-word memory read.36

Figure 10 b) - n-word memory read.37

Figure 11 - n-word write: control space access.39

Figure 12 - n-word read: control space access .41

Figure 13 - n-word message transfer.43

Figure 14 - One-word write: control register access .45

Figure 15 - One-word read: control register access .47

Figure 16 - Bus lock transfer.49

Figure 17 - Cache invalidation.52

Figure 18 - Retry indication .54

Figure 19 - Copyback and steal operations after retry indication .56

Figure 20 - Steal inhibit operation .58

Figure 21 - Error report in answer transaction when DUT detects error .60

Figure 22 - When function unit (0#) detects time out.61

Figure 23 - Relation between CPU operation and commands on system bus .64

Figure 24 - STbus write-through cache coherency control protocol.69

Figure 25 - STbus copyback cache coherency control protocol .74

Figure A.1 - STbus performance (in 8-byte bus width and 32-bit addressing mode).79

Figure B.1 - Example of dead lock problem .80

Figure C.1 - Example of lock transfer to EM cache data.81

14576 © ISO/IEC:1999(E) – v –

Tables

Table 1 - Basic Interface Signals (function unit interfaces other than bus handler) .6

Table 2 - Optional Interface Signals (function unit interfaces other than bus handler) .6

Table 3 - Command Format for Information Transfer Bus.17

Table 4 - OPT Code Definitions .18

Table 5 - M Bit Definition .19

Table 6 - Message Sequence .22

Table 7 - Answer Code Definition .28

Table 8 - System Bus Command Types.63

Table 9 - Semantics of Discrepancy between Base and Spare Signals.76

– vi – 14576 © ISO/IEC:1999(E)

INFORMATION TECHNOLOGY –

SYNCHRONOUS SPLIT TRANSFER TYPE

SYSTEM BUS (STbus) –

LOGICAL LAYER

FOREWORD

ISO (the International Organization for Standardization) and IEC (the International

Electrotechnical Commission) form the specialized system for worldwide

standardization. National bodies that are members of ISO or IEC participate in the

development of International Standards through technical committees established by

the respective organization to deal with particular fields of technical activity. ISO and

IEC technical committees collaborate in fields of mutual interest. Other international

organizations, governmental and non-governmental, in liaison with ISO and IEC, also

take part in the work.

In the field of information technology, ISO and IEC have established a joint technical

committee, ISO/IEC JTC 1. Draft International Standards adopted by the joint

technical committee are circulated to national bodies for voting. Publication as an

International Standard requires approval by at least 75 % of the national bodies casting

a vote.

International Standard ISO/IEC 14576 was prepared by subcommittee 26:

Microprocessor systems, of ISO/IEC joint technical committee 1: Information

technology.

International Standards are drafted in accordance with the rules given in the ISO/IEC

Directives, Part 3.

Annexes A, B and C are for information only.

14576 © ISO/IEC:1999(E) – 1 –

INFORMATION TECHNOLOGY –

SYNCHRONOUS SPLIT TRANSFER TYPE

SYSTEM BUS (STbus) –

LOGICAL LAYER

1. Overview

1.1 Scope

This International Standard specifies the logical specifications of STbus which is a high-

performance and highly reliable system bus. STbus adopts a synchronous transfer method with a

high-speed clock and a split transfer method enabling to minimize bus holding time during one

bus operation and to use a bus efficiently.

The contents given in this specifications are as follows:

a) System bus interface signal provisions;

b) Bus operations and transfer protocol for each bus operation;

c) Copyback cache coherency control for maintaining consistency between a shared memory and

a cache memory of each processor in a multiprocessor system;

d) Fault detection function using parity check and duplex configuration for control signals.

1.2 Applicability

This International Standard is Applicable to a high-performance system bus or an I/O bus in a

multiprocessor system. Typical STbus applications are indicated in Figure 1:

a) A System bus and an I/O bus in a TCMP system;

b) A System bus in an LCMP system.

- TCMP: tightly coupled multiprocessor system

(A system consisting of two or more processors sharing the same memory, with the

entire system controlled by one OS.)

- LCMP: loosely coupled multiprocessor system

(A system in which each processor is connected by a shared memory or other medium,

with each processor operated by an individual OS.)

– 2 – 14576 © ISO/IEC:1999(E)

Processor Processor

Shared

.

CPU

CPU

memory

System

bus

TCMP

system

I/O bus

.

I/O I/O

Processor

Processor

Local memory

Local memory

.

LCMP

system

CPU Local I/O

CPU Local I/O

System bus

Figure 1 - STbus Applications

14576 © ISO/IEC:1999(E) – 3 –

2. Definitions

2.1 Explanation of Terms

For the purposes of this International Standard, the following terms and definitions apply.

1) Answer transaction

An information transfer operation by which a function unit receiving a command returns

answer information, to notify the unit issuing the command that the command has been

completed (in some cases the requested data is appended) and to indicate status information.

2) Basic signal

Those bus interface signals that must be implemented in every STbus system, and thus for

which compatibility is assured among different systems.

3) Block

The minimum unit registered in cache memory. In STbus this is limited to 32 bytes.

4) Bus handler (BH)

A concentrated bus control mechanism for sorting out competing bus requests from different

function units, selecting one of the requests, and granting the bus right to that function unit.

5) Bus master

A function unit that has the bus right (a grant signal has been asserted) and is transferring

information on the bus.

6) Bus slave

A function unit to which information is being transferred by the bus master.

7) Bus snoop

Monitoring of the bus for read operations from external memory and write operations to

external memory.

8) Cache invalidation

A request to invalidate a block in cache memory. For example, when a write access is made

to a Shared & Unmodified (SU) area, this is used to invalidate the same area in another

cache.

9) CPU

A central processing element with functions for interpreting and executing instructions. In

these specifications, cache memory is included with the CPU.

10) Copyback scheme

A cache updating method in which data written by the processor or instruction execution

part is updated only in the cache, without being reflected directly in memory. The copyback

– 4 – 14576 © ISO/IEC:1999(E)

cache supported in STbus has the following three internal states: Invalid state (I), Shared &

Unmodified state (SU), Exclusive & Modified state (EM).

11) DUT (Destination Unit)

A function unit performing an answer transaction.

12) Exclusive & Modified state (EM)

An internal state in a copyback cache, whereby the only place in the system an access area is

registered is in cache memory, and the contents are not the same as shared memory. In this

state, only the cache has been updated.

13) Function unit

A hardware unit connected to the bus and having a mechanism for bus interface control.

Normally one function unit consists of one board.

14) I/O adapter

A function unit that controls I/O devices under control of a processor.

15) Invalid state (I)

A state in which an area accessed by the processor is not registered in cache memory.

16) Modified read command

A command issued to the system bus by a copyback cache memory when a write access by

the processor results in a write miss.

17) Optional signal

Those bus interface signals that users are free to adopt or not in system implementation.

18) Order transaction

An information transfer operation for sending a command and requesting processing by

another function unit.

19) Parity

When not otherwise noted in these specifications, parity is always odd. Here odd parity

means that when a given signal (e.g., 8 bits) is augmented by a parity bit (e.g., 8 + 1 = 9

bits), then if the sum of 1-bits in the augmented set is an even number (including 0) an error

is detected.

20) Processor

A function unit with the capability of executing instructions and controlling the various I/O

adapters. Processor consists of CPU and memory in general.

21) Read hit/read miss

When an instruction or operand to be read by the processor is registered in cache memory,

this is called a read hit. If not, it is a read miss.

14576 © ISO/IEC:1999(E) – 5 –

In the case of a read miss, if the object of the read is cacheable, one block containing the

object is newly registered in the cache.

22) Retry indication

The temporary suspension of access by external devices to a copyback cache area that has

been updated without the change having been reflected in main memory.

23) Shared & Unmodified state (SU)

An internal state in a write-through or copyback cache, whereby an access area is registered

in a cache and has the same contents as shared memory. Sharing by more than one cache is

possible.

24) SUT (Source Unit)

A function unit performing an order transaction.

25) Write hit/write miss

If an area to be written by the processor is registered in cache memory, this is called a write

hit. If not, it is a write miss.

In the case of a write-through cache, the write data is immediately reflected in shared

memory.

If a copyback cache scheme is used, in the case of a write hit the write data is reflected in the

cache only. If a write miss occurs, one block of the write area is read from shared memory

and newly registered, then the write data is written over that area in the cache only.

26) Write-through scheme

A cache updating method in which data written by the processor or instruction execution

part is reflected directly in memory. The internal states are: Invalid state (I), Shared &

Unmodified state (SU).

2.2 Notation

The following symbols and other notation are used in these specifications.

- Function unit numbers are indicated by (#n), and control signals to each unit are written as

[signal line name + (function unit number)], e.g., RQL*(#n), GR*(#n).

- When the values of control signals are indicated, the following notation is used.

- When indicating the logical value of a signal line: 1 and 0 are used, with 1 meaning assert

and 0 meaning negate.

- When indicating the actual value on a signal line: "H" and "L" are used, with "H"

meaning high and "L" meaning low signal potential.

- Hexadecimal notation in these specifications is indicated by H'## (e.g., H'FF, H'00).

– 6 – 14576 © ISO/IEC:1999(E)

3. Interface Specifications

3.1 Interface Signals

The STbus basic interface signals are listed in Table 1, as seen from one function unit.

In this table, RQL*, RQH*, GR*, and ET* are signals connected individually to each function

unit.

Table 1 - Basic Interface Signals (function unit interfaces other than bus handler)

No. Signal name Count Functional category Connection type

1RQL (Request low) 1

*

2RQH (Request high) 1 Arbitration control Individually

*

connected

3GR (Grant) 1

*

4ET (End of bus transaction) 1

*

5BS (Bus transaction start) 1

*

6BUR (Burst) 1 Transfer control

*

7CSP (Control signal parity) 1

*

8LCK (Lock) 1 Bus connection

*

9 AD [00.63] (Command/address/data) 64 Command/address/data

*

10 ADP [0.7] (AD parity) 8

*

11 RTY (Retry) 1 Cache coherency control

*

12 RST (Reset) 1 Reset signal

*

13 CK (Clock) 1 Clock See Note 2.

Total number of signals 83

Note 1: A after a signal name indicates negative logic.

*

Note 2: For clock connection, a connection configuration must be adopted that can guarantee

the skew specified in the physical specifications.

The optional interface signal lines as seen from one function unit are listed in Table 2. Since

these signals are optional, the system implementor can choose whether or not to use them.

Table 2 - Optional Interface Signals (function unit interfaces other than bus handler)

No. Signal name Count Functional category Connection type

14 LCKS* (Lock spare) 1 Transfer control

15 RTYS* (Retry spare) 1 Bus connection

16 STI* (Steal inhibit) 1 Cache coherency control

17 STIS* (Steal inhibit spare) 1

14576 © ISO/IEC:1999(E) – 7 –

Connection structure

Function

Function

Function

Clock generator

....

unit(#n)

unit(#1)

unit(#0)

(CK)

Bus handler

(BH)

RQL*

(#0)

ET*

RQH*

RQL*

(#1)

ET*

.

RQH*

.

.

.

.

.

RQL* .

.

(#n)

ET*

RQH*

GR*(#0)

GR*(#1)

.

.

.

.

GR*(#n)

BS*

BUR*

CSP*

LCK*

RTY*

RST*

AD[00.63]*

ADP[0.7]*

n+1: Connected function unit count

CK signal: lndividual signal or bus signal

For clock connection, a connection configuration must be adopted

that can guarantee the skew specified in the physical specifications.

Figure 2 - Connection interface between function units (basic pattern)

– 8 – 14576 © ISO/IEC:1999(E)

Explanation of each signal

1) RQL* (Request low)

This signal is used by a source unit (SUT) to request the bus. Each unit asserts this signal

when performing an order transaction, for requesting the bus right from the bus handler. A

function unit for which the GR signal is asserted, granting the right to use the bus, must

*

negate this signal.

This signal is notified to the bus handler by each function unit using individual lines.

This signal has a lower priority than that of RQH , RQL and RQH cannot be asserted

* * *

simultaneously.

2) RQH* (Request high)

This signal is used by a destination unit (DUT) to request the bus. Each unit asserts this

signal when performing an answer transaction, in order to request the bus right from the bus

handler. A function unit for which the GR signal is asserted, granting the right to use the

*

bus, must negate this signal.

This signal is notified to the bus handler by each function unit using individual lines.

This signal has a higher priority than that of RQL , RQH and RQL cannot be asserted

* * *

simultaneously.

While a LCK signal is asserted, the bus handler will not assert GR in response to a RQL

* * *

signal from another function unit. However, GR will be asserted in response to RQH , so

* *

any unit is capable of executing an answer transaction.

3) GR* (Grant)

This signal is for granting the bus right to a bus master in response to a RQL or RQH bus

* *

request signal. Only while this signal is asserted, a function unit enables bus drivers (Nos. 5

- 7, 9,10, in Table 1) and send information on the bus. This signal is supplied to each

function unit by the bus handler on individual lines.

4) ET* (End of bus transaction)

This signal is issued by the bus master to give advance notice of the end of transfer data.

This signal is negated two cycles prior to the actual end of a data transfer.

If this signal is not asserted at the same time as RQL or RQH , this is taken to mean that

* *

the requested transaction is a one-cycle transfer.

For a transfer of two cycles or more, ET is asserted at the same time as RQL or RQH .

* * *

This signal is notified to the bus handler by each function unit using individual lines.

5) BS* (Bus transaction start)

When a function unit that has obtained the bus right performs an order transaction or answer

transaction, this signal is asserted at the same time as the command or answer information is

sent on the bus, indicating to the destination function unit the start of transfer information.

14576 © ISO/IEC:1999(E) – 9 –

This signal is asserted only during the first bus cycle of an order transaction or answer

transaction.

When data is sent following the initial command or answer information, information receipt

must be performed at the initiative of the receiving function unit, using the BS signal as a

*

reference.

6) BUR* (Burst)

This signal indicates burst transfer mode, consisting of two or more data transfer cycles.

The sending function unit asserts this signal, and while it is asserted the receiving function

unit continues to receive data.

This signal is negated one cycle prior to the end of data transfer. When the receiving

function unit detects the negation of this signal, it ends the receiving operation after one

cycle.

If a BS signal is asserted and BUR is not asserted, one-cycle transfer is indicated.

* *

7) CSP* (Control signal parity)

This is a parity signal for the transfer control signals BS and BUR . It indicates odd parity.

* *

8) LCK* (Lock)

This is a bus lock signal. It is asserted at the same time as the SUT starts an order

transaction, and is negated when the SUT itself indicates the end of a transaction.

Split transfer is the main method adopted for STbus, but interlock transfer using this signal

is also possible.

9) AD [00.63]* (Command / address / data 00-63)

This is a 64-bit two-way information transfer bus for time division transfer of control

information, address information, and data.

10) ADP [0.7]* (AD parity 0-7)

These are parity signals for each byte of AD[00-63] . They indicate odd parity.

*

11) RTY* (Retry)

This signal is used for coherency control when a copyback cache scheme is used in a TCMP

system. When this signal is asserted, the bus master must retry the current transaction. See

5.4 Retry Indication for details.

12) RST* (Reset)

A function unit connected to STbus uses this signal to indicate a reset to other function

units. While this signal is asserted, reset is in effect. Assertion time of this signal is

specified to be 5 μs-10 μs. Assertion timing shall be synchronized with the bus clock.

13) CK (Clock)

This is the STbus common clock signal. Bus operations are synchronized with the falling

edge of this signal.

– 10 – 14576 © ISO/IEC:1999(E)

14) LCKS*(Lock spare)

This is a spare LCK* signal. When this signal is used, LCK* must also be used at the same

time. If either LCK* or this signal is asserted alone, the lock transfer is not effective. The

lock transfer is performed, only when both LCK* and this signal are asserted. This signal is

optional.

15) RTYS* (Retry spare)

This is a spare RTY signal. When this signal is used, RTY must also be used at the same

* *

time. If either RTY or this signal is asserted alone, the bus master must retry the current

*

transaction. This signal is optional.

16) STI* (Steal inhibit)

This is a signal used in copyback cache coherency control. It is connected only between

function units. This signal is optional.

When this signal is asserted, the bus master prohibits a steal operation during copyback of

data concerned. See 5.5 Steal Operation for details.

17) STIS* (Steal inhibit spare)

This is a spare STI signal. When this signal is used, STI must also be used at the same

* *

time. If either STI or this signal is asserted alone, the bus master prohibits a steal operation

*

during copyback of data concerned. This signal is optional.

14576 © ISO/IEC:1999(E) – 11 –

4. Bus Operations

4.1 Protocol for Basic Operations

Examples of basic STbus operations (one-cycle transfer and two-cycle transfer) are given here,

along with an explanation of the operations.

.

.

Clock signal CK Time

Bus request signal

[3]

[10]

. .

RQL (#0)

(Unit#0→BH) RQH (#1)

*

* (Unit#1→ BH)

[8]

End-of-bus-transaction [1]

[12]

.

signal ET (#0)

[6]

*

Bus grant signal

GR (#0) [2]

(BH→ #1)

*

[7] (BH→ #0) GR (#1)

*

[9]

BS BS

* *

Transfer control signals

[4]

[11]

BUR

*

[5]

Unit #0 Unit #1

↓ ↓

CAW

Co D0 Unit #1 Unit #0

Data transfer bus AD[00.31]

*

(8 bytes) AD[32.63]

* A D1

Abbreviations:

Co: Order command Di: Data A: Address CAW: Answer command BH: Bus handler

[1]-[12]: Change point of each signal line (numbers correspond to explanation below)

Figure 3 - Concept of bus operation protocol (for 1-cycle or 2-cycle transfer:

8-byte bus width specification, write operation)

All function units and the bus handler operate in synchronization with the common clock CK.

[1] In the figure above, function unit (#0) performs a two-word information transfer to

function unit (#1). First, function unit (#0) asserts a bus request signal RQL (#0),

*

requesting the bus handler to grant the bus right. At the same time, since the number of

words to be transferred is two, it also asserts an end-of-bus-transaction signal ET (#0).

*

[2] If the RQL (#0) signal can be accepted, the bus handler asserts a bus grant signal

*

GR (#0) to function unit (#0), granting it the bus right.

*

[3] Function unit (#0), obtaining the bus right, negates the RQL (#0) signal upon the

*

assertion of GR (#0).

*

[4] At the same time as the above, function unit (#0) upon receiving GR (#0) validates the

*

information transfer bus and sends information on the bus. In the initial cycle of

information transfer, it asserts a BS transfer control signal.

*

– 12 – 14576 © ISO/IEC:1999(E)

[5] Since in this example a two-word information transfer is performed, a BUR signal is

*

asserted at the same time as BS , informing the other function units of the start of burst

*

transfer. The BUR signal is negated one cycle prior to the end of the transaction.

*

[6] The ET (#0) asserted at the same time as GR (#0) is negated two cycles prior to the end

* *

of the transaction, notifying the bus handler in advance that the bus is about to be freed.

[7] When the bus handler detects the negation of ET (#0) it negates GR (#0).

* *

[8] When answer information (one word) is returned in response to the information from

function unit (#0), function unit (#1) asserts a bus request signal RQH (#1), requesting the

*

bus handler to grant the bus right. As long as the number of words to be transferred in the

answer is one, ET (#1) is not asserted.

*

[9] If the RQH (#1) signal can be accepted, the bus handler asserts a bus grant signal

*

GR (#1) to function unit (#1).

*

[10] Function unit (#1), obtaining the bus right, negates the RQH (#1) signal upon the

*

assertion of GR (#1).

*

[11] At the same time as the above, function unit (#1) upon receiving GR (#1) validates the

*

information transfer bus and sends information on the bus. In the initial cycle of

information transfer, it asserts a BS transfer control signal. Since the number of words to

*

be transferred in the answer is one, BUR (#1) is not asserted.

*

[12] Since ET (#1) is negated, the bus handler negates GR (#1) in one-word transfer.

* *

Since a split transfer method is adopted, the bus can be used for transactions between other

function units during steps [7] to [9] above.

14576 © ISO/IEC:1999(E) – 13 –

.

. .

Clock signal CK Time

[8]

Bus request signal

[3]

.

.

RQH (#1) (Unit#1→ BH)

*

RQL (#0)

*

[1]

[6]

End-of-bus-transaction

. .

ET (#1)

*

signal ET (#0)

[11]

*

Bus grant signal

.

GR (#1) [7]

[5] *

[2]

[12]

GR (#0)

*

BS

*

BS

*

[4]

[9]

Transfer control signals

BUR [10]

*

Unit #0

Unit #1

↓

↓

.

CAW D0 . . Dn-3 Dn-1

Co

Unit #1

Unit #0

Data transfer bus AD[00.31]

.

*

.

D1 Dn-2 Dn

(8 bytes) AD[32.63]

A

*

.

Figure 4 – Concept of bus operation protocol (for transfer of 3-cycles or more:

8-byte bus width specification, read operation)

[1] The figure above shows one-word information transfer between function unit (#0) and

function unit (#1). First, function unit (#0) asserts a bus request signal RQL (#0),

*

requesting the bus handler to grant the bus right. Since the number of words to be

transferred is one, ET (#0) is not asserted.

*

[2] If the RQL (#0) signal can be accepted, the bus handler asserts a bus grant signal

*

GR (#0) to function unit (#0), granting it the bus right.

*

[3] Function unit (#0), obtaining the bus right, negates the RQL (#0) signal upon the

*

assertion of GR (#0).

*

[4] At the same time as the above, function unit (#0) upon receiving GR (#0) validates the

*

information transfer bus and sends information on the bus. In the initial cycle of

information transfer, it asserts a BS transfer control signal. Since the number of words to

*

be transferred in this example is one, BUR (#0) is not asserted.

*

[5] Since RQL (#0) and ET (#0) are negated, the bus handler negates GR (#0) in one-word

* * *

transfer.

[6] When answer information of three words or more is returned in response to the

information from function unit (#0), function unit (#1) asserts a bus request signal

RQH*(#1), requesting the bus handler to grant the bus right. In a multi-word answer,

ET*(#1) must be asserted at the same time.

[7] If the RQH (#1) signal can be accepted, the bus handler asserts a bus grant signal

*

GR (#1) to function unit (#1).

*

[8] Function unit (#1), obtaining the bus right, negates the RQH (#1) signal upon the

*

assertion of GR (#1).

*

– 14 – 14576 © ISO/IEC:1999(E)

[9] At the same time as the above, function unit (#1) upon receiving GR (#1) validates the

*

information transfer bus and sends information on the bus. In the initial cycle of

information transfer, it asserts a BS transfer control signal.

*

[10] Since in this example three words or more of information are transferred, a BUR signal is

*

asserted at the same time as BS , informing the other function unit of the start of burst

*

transfer. The BUR signal is negated one cycle prior to the end of the transaction.

*

[11] The ET (#1) asserted at the same time as GR (#1) is negated two cycles prior to the end

* *

of the transaction, notifying the bus handler in advance that the bus is about to be freed.

[12] The bus handler monitors the bus for negation of the ET (#1) signal, and when this is

*

detected it negates GR (#1).

*

14576 © ISO/IEC:1999(E) – 15 –

The operation when a 4-byte bus width is used (one-cycle or two-cycle transfer) is shown below for

reference.

.

.

Clock signal CK Time

Bus request signal

[3]

[10]

.

.

RQL (#0)

(Unit#0→BH) RQH (#1)

*

* (Unit#1→ BH)

[8]

End-of-bus-transaction [1]

[12]

.

signal ET (#0) [6]

*

Bus grant signal

[7] GR (#1)

GR (#0) [2] *

*

[9]

BS BS

* *

Transfer control signals

[4]

[11]

BUR

*

Unit #0

Unit #1

[5]

↓

↓

Unit #1

Unit #0

CAW

Data transfer bus AD[00.31] Co A D0 D1

*

(4 bytes)

Figure 5 - Concept of bus operation protocol (for 1-cycle or 2-cycle transfer:

4-byte bus width specification, write operation)

When the width of the information bus is 4 bytes, the operation by which function unit (#0)

sends two-word information to function unit (#1) is essentially the same as with an 8-byte bus.

Since, however, the bus width is 4 bytes, the information that is sent on an 8-byte bus in one

cycle requires two cycles on a 4-byte bus, as shown in the figure above.

The explanation of each signal change point is the same as for the 8-byte specification.

– 16 – 14576 © ISO/IEC:1999(E)

4.2 Transfer Protocol

4.2.1 Bus operation types

The bus operations on STbus can be classified broadly into four types; memory access, control

space access, message transfer and control register access.

1) Memory access

This is a bus operation in which a function unit performs a read or write operation in shared

memory or in the local memory of any other function unit. In the basic bus specification

any transfer byte size can be designated up to the maximum of 256 bytes.

2) Control space access

This is a bus operation in which a program running on a function unit directly reads or

writes data mapped to the control space of any other function unit. In the basic bus

specification any transfer unit byte size can be designated up to the maximum of 256 bytes.

3) Message transfer

This is a bus operation in which a function unit sends a message to any other function unit.

4) Control register access

This is a bus operation in which a program running on a function unit directly reads or

writes up to 8 bytes in the control registers (up to 256) of any other function unit.

4.2.2 Command format

The information transfer bus is 64 bits wide (or 32 bits), and adopts a big endian. The bit order

is AD [00.63] (or AD [00.31] ) starting from the MSB.

* *

The information transfer bus is divided into byte units, in the order from byte 0 to byte 7 starting

from the MSB.

Information transferred on the bus can be classified broadly into the four types commands,

addresses, data, and message communication operands.

In information transfer, the commands are sent first to the destination unit. The format is shown

in Table 3. Although not indicated specifically in the table, a single parity bit is attached to the

above byte units.

14576 © ISO/IEC:1999(E) – 17 –

Table 3 - Command Format for Information Transfer Bus

Byte 0 Byte 1 Byte 2 Byte 3

Bus Operation OPT OPT OPT

0 1 2

00 01.07 08 09.15 16 17 18 19 20 21 22 23 24.31

Memory access 0 BMID 0 BSID 0 BT R/W A64 M NAT AID BCT

Control space 0 BMID 0 BSID 1 BT R/W A64 0 NAT AID BCT

access

Message 0 BMID 1 BSID 0 BT MD SQ NAT AID BCT

transfer

Control register 0 BMID 1 BSID 1 BT R/W BCT AID RA

access

Reserved 1 BMID 0 BSID 0 BT * * * * * * * * * * * * * *

Reserved 1 BMID 0 BSID 1 BT * * * * * * * * * * * * * *

Reserved 1 BMID 1 BSID 0 BT * * * * * * * * * * * * * *

Answer 1 BMID 1 BSID 1 BT ROPT RNAT RAID ANS

Notation:

OPT: Operation Type BCT: Byte Count

BMID: Bus Master ID MD: Mode

BSID: Bus Slave ID SQ: Sequence

BT: Bus Type RA: Register Address

R/W: Read/Write ROPT: Return Operation Type

A64: 64-bit Address Space RNAT: Return NAT

M: Modify RAID: Return Access ID

NAT: No-Answer Transaction ANS: Answer code

AID: Access ID

*: Reserved

– 18 – 14576 © ISO/IEC:1999(E)

1) Operation type codes

Commands are either for order transactions, from SUT to DUT, or for answer transactions, from

DUT to SUT. There are eight command types, including Reserved. Together these are called

operation types, and are defined in a 3-bit OPT (operation type) consisting of bit 0 of byte 0, bit

8 of byte 1, and bit 16 of byte 2.

The OPT codes are given in Table 4.

Table 4 - OPT Code Definitions

OPT Operation type

0 1 2

0 0 0 Memory Access

0 0 1 Control Space Access

0 1 0 Message Transfer

0 1 1 Control Register Access

1 0 0 Reserved

1 0 1 Reserved

1 1 0 Reserved

1 1 1 Answer

2) ID (Identifier) and Bus Type (BT)

In an order transaction, a BMID (Bus Master Identifier) and BSID (Bus Slave Identifier) are sent

in bytes 0 and 1 of the information transfer bus.

Bit 17 of byte 2 indicates the BT (Bus Type).

The semantics of each field are as follows.

BMID (Bus Master Identifier):

Function unit ID of the bus master, consisting of 7 bits.

BSID (Bus Slave Identifier):

Function unit ID of the bus slave, consisting of 7 bits.

BT (Bus Type):

0: 4-byte bus 1: 8-byte bus

14576 © ISO/IEC:1999(E) – 19 –

3) Memory access

The semantics of each field are as follows.

R/W (Read/Write):

0: Write operation by SUT to DUT

1: Read operation by SUT from DUT

A64 (64-bit Address Space)

0: 32-bit address space

1: 64-bit address space

M (Modify):

This signal is used in cache coherency control in a TCMP configuration. It is used in

combination with R/W, as specified in Table 5.

Table 5 - M Bit Definition

R/W M Bus operation

0 0 Memory Write Operation

1 Cache Invalidation

1 0 Memory Read Operation

1 Memory Read Operation and Cache Invalidation

When the R/W field is 0 and the M field is 1, the BCT field is invalid, so that only

commands and addresses can be transferred on the bus. Write operations to memory are

not performed. If a cache hit occurs in another function unit, the cache is invalidated.

Note: If copyback cache is not supported, the M field is cleared to 0.

AID (Access Identifier):

An identifier used when multiple access is made to memory. Applications include

simultaneous operation of multiple DMA ports, or pipeline operation of a single DMA

port.

An example of multiple memory access operation in a split transfer bus is shown in

Figure 6 below.

– 20 – 14576 © ISO/IEC:1999(E)

Processor

Shared memory

(Shared memory)

(I/O adapter)

board

board

Read order

STbus

Port 1

(AID=00)

Answer data

(AID=00)

Read order

I/O adapter board

Port 2

(AID=01)

Port 1 Port 2

Answer data

Port 1

(AID=01)

I/O BUS

Port 2

I/O Device 1

I/O Device 2

Figure 6 - Pipeline operation

NAT (No-Answer Transaction):

This indicates that the transaction to follow is a no-answer transaction. When this bit is set

in an order transaction, the bus slave does not perform an answer transaction in response.

However, if an error occurs in the order transaction, an answer to indicate the error is

returned.

0: Transaction with answer returned

1: Transaction without answer returned

BCT (Byte Count):

This indicates the number of bytes of transfer data sent from SUT to DUT or demanded

from DUT by SUT. The number of transfer bytes are defined as shown in Figure 7 a). Up

to 256 bytes can be sent consecutively in one bus operation. When t="00", the number of

valid bytes transferred on the bus must equal the contents of n plus 1. For example, t=

"00" & n="00000" means 1-byte transfer, while t="00" & n="11111" means 32 bytes

transfer.

Byte alignment in case o

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...