SIST EN 16602-70-60:2019

(Main)Space product assurance - Qualification and Procurement of printed circuit boards

Space product assurance - Qualification and Procurement of printed circuit boards

This standard addresses the qualification and procurement of printed circuit boards, which are necessary for all type of space projects.

Raumfahrtproduktsicherung - Qualifizierung und Beschaffung von Leiterplatten

Assurance produit des projets spatiaux - Qualification et approvisionnement des circuits imprimés

Zagotavljanje kakovosti proizvodov v vesoljski tehniki - Kvalifikacija in nabava plošč tiskanih vezij

Ta standard obravnava kvalifikacijo in nabavo plošč tiskanih vezij, ki so potrebna za vse vrste vesoljskih projektov.

General Information

- Status

- Published

- Public Enquiry End Date

- 20-Dec-2017

- Publication Date

- 08-Aug-2019

- Technical Committee

- I13 - Imaginarni 13

- Current Stage

- 6060 - National Implementation/Publication (Adopted Project)

- Start Date

- 24-Jul-2019

- Due Date

- 28-Sep-2019

- Completion Date

- 09-Aug-2019

Relations

- Replaces

SIST EN 16602-70-10:2015 - Space product assurance - Qualification of printed circuit boards - Effective Date

- 17-Jul-2019

- Effective Date

- 17-Jul-2019

- Effective Date

- 16-Nov-2016

- Effective Date

- 16-Nov-2016

Overview

SIST EN 16602-70-60:2019 - Space product assurance: Qualification and Procurement of printed circuit boards is the European standard for qualification, manufacturing control and procurement of printed circuit boards (PCBs) used in space projects. Published by CEN/CENELEC and adopted by the Slovenian standards body (SIST), it supersedes EN 16602-70-10:2015 and EN 16602-70-11:2015. The standard sits at the intersection of space product assurance, PCB qualification, and procurement for space systems (ICS 31.180; 49.140).

Key topics and technical requirements

The standard defines a comprehensive quality assurance and test framework for PCBs intended for space applications. Major topics include:

- Quality assurance for qualification: roles, qualification process, requests for qualification, qualification vehicles, PID (Process Identification Document), audit and QA reporting, qualification renewal and delta qualification.

- QA for manufacture and procurement: procurement specifications, quotations, purchase orders, design reviews (DR), manufacturing readiness reviews (MRR), incoming/outgoing inspection, traceability, operator training, repair processes, packaging, storage and baking, shelf-life considerations.

- Test and inspection requirements: selection of tests for qualification and procurement including visual inspection, electrical continuity and high-resistance tests, impedance, dielectric properties, microsectioning, solderability, peel strength, flexural fatigue, interconnect stress test (IST), thermal cycling, reflow/rework simulation, and ECM-related tests such as Temperature–Humidity–Bias (THB) and Conductive Anodic Filament (CAF).

- Coupons and microsections: configuration, delivery and evaluation of test coupons and microsections as part of outgoing inspection and first article inspection (FAI).

- Acceptance criteria and reporting: standardized acceptance tables, inspection criteria (visual and microsection), and normative annexes including Qualification Letter, Certificate of Conformity (CoC), Qualification Test Report and PID templates.

Practical applications - who uses this standard

SIST EN 16602-70-60:2019 is intended for organizations involved in space hardware that depend on reliable PCB performance, including:

- Space prime contractors and system integrators specifying PCB procurement and acceptance criteria.

- PCB manufacturers and suppliers seeking qualification to supply flight-use boards.

- Quality assurance and procurement teams defining contracts, purchase orders and inspection plans for space projects.

- Test laboratories and inspection houses performing microsectioning, electrical and environmental tests.

- Design and reliability engineers assessing PCB technologies (rigid, flexible, ceramic) and changes impacting qualification.

Related standards

- Supersedes: EN 16602-70-10:2015 and EN 16602-70-11:2015.

- Published as a CEN/CENELEC European Standard (available in EN, FR, DE).

Using this standard helps reduce procurement risk, ensure traceability and compliance, and establish consistent PCB qualification and PCB testing practices for demanding space projects.

Frequently Asked Questions

SIST EN 16602-70-60:2019 is a standard published by the Slovenian Institute for Standardization (SIST). Its full title is "Space product assurance - Qualification and Procurement of printed circuit boards". This standard covers: This standard addresses the qualification and procurement of printed circuit boards, which are necessary for all type of space projects.

This standard addresses the qualification and procurement of printed circuit boards, which are necessary for all type of space projects.

SIST EN 16602-70-60:2019 is classified under the following ICS (International Classification for Standards) categories: 31.180 - Printed circuits and boards; 49.140 - Space systems and operations. The ICS classification helps identify the subject area and facilitates finding related standards.

SIST EN 16602-70-60:2019 has the following relationships with other standards: It is inter standard links to SIST EN 16602-70-10:2015, SIST EN 16602-70-11:2015, SIST EN 16602-70-11:2015, SIST EN 16602-70-10:2015. Understanding these relationships helps ensure you are using the most current and applicable version of the standard.

SIST EN 16602-70-60:2019 is associated with the following European legislation: Standardization Mandates: M/496. When a standard is cited in the Official Journal of the European Union, products manufactured in conformity with it benefit from a presumption of conformity with the essential requirements of the corresponding EU directive or regulation.

SIST EN 16602-70-60:2019 is available in PDF format for immediate download after purchase. The document can be added to your cart and obtained through the secure checkout process. Digital delivery ensures instant access to the complete standard document.

Standards Content (Sample)

SLOVENSKI STANDARD

01-september-2019

Nadomešča:

SIST EN 16602-70-10:2015

SIST EN 16602-70-11:2015

Zagotavljanje kakovosti proizvodov v vesoljski tehniki - Kvalifikacija in nabava

plošč tiskanih vezij

Space product assurance - Qualification and Procurement of printed circuit boards

Raumfahrtproduktsicherung - Qualifizierung und Beschaffung von Leiterplatten

Assurance produit des projets spatiaux - Qualification et approvisionnement des circuits

imprimés

Ta slovenski standard je istoveten z: EN 16602-70-60:2019

ICS:

31.180 Tiskana vezja (TIV) in tiskane Printed circuits and boards

plošče

49.140 Vesoljski sistemi in operacije Space systems and

operations

2003-01.Slovenski inštitut za standardizacijo. Razmnoževanje celote ali delov tega standarda ni dovoljeno.

EUROPEAN STANDARD

EN 16602-70-60

NORME EUROPÉENNE

EUROPÄISCHE NORM

July 2019

ICS 31.180; 49.140

Supersedes EN 16602-70-10:2015, EN 16602-70-

11:2015

English version

Space product assurance - Qualification and Procurement

of printed circuit boards

Assurance produit des projets spatiaux - Qualification Raumfahrtproduktsicherung - Qualifizierung und

et approvisionnement des circuits imprimés Beschaffung von Leiterplatten

This European Standard was approved by CEN on 9 November 2018.

CEN and CENELEC members are bound to comply with the CEN/CENELEC Internal Regulations which stipulate the conditions for

giving this European Standard the status of a national standard without any alteration. Up-to-date lists and bibliographical

references concerning such national standards may be obtained on application to the CEN-CENELEC Management Centre or to

any CEN and CENELEC member.

This European Standard exists in three official versions (English, French, German). A version in any other language made by

translation under the responsibility of a CEN and CENELEC member into its own language and notified to the CEN-CENELEC

Management Centre has the same status as the official versions.

CEN and CENELEC members are the national standards bodies and national electrotechnical committees of Austria, Belgium,

Bulgaria, Croatia, Cyprus, Czech Republic, Denmark, Estonia, Finland, Former Yugoslav Republic of Macedonia, France, Germany,

Greece, Hungary, Iceland, Ireland, Italy, Latvia, Lithuania, Luxembourg, Malta, Netherlands, Norway, Poland, Portugal, Romania,

Serbia, Slovakia, Slovenia, Spain, Sweden, Switzerland, Turkey and United Kingdom.

CEN-CENELEC Management Centre:

Rue de la Science 23, B-1040 Brussels

© 2019 CEN/CENELEC All rights of exploitation in any form and by any means Ref. No. EN 16602-70-60:2019 E

reserved worldwide for CEN national Members and for

CENELEC Members.

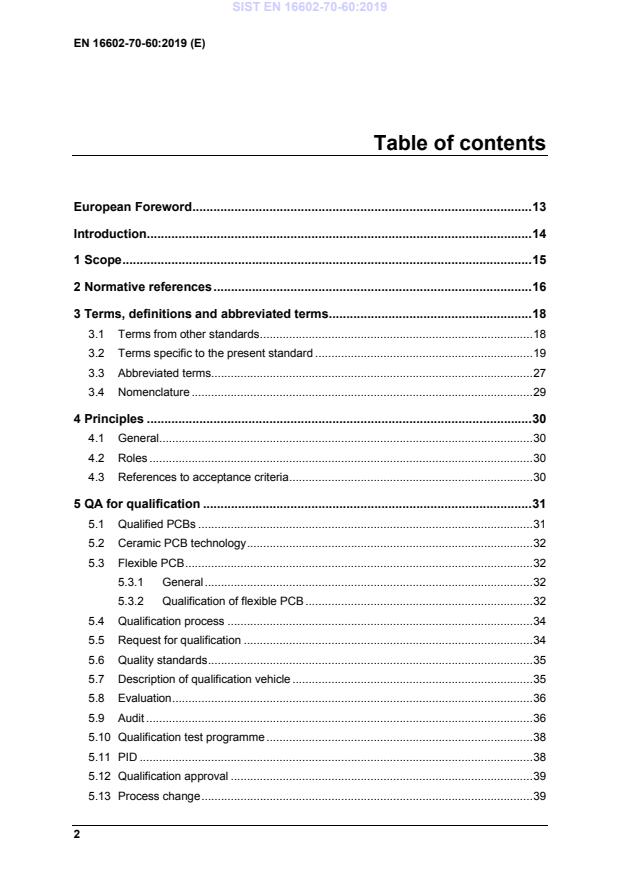

Table of contents

European Foreword . 13

Introduction . 14

1 Scope . 15

2 Normative references . 16

3 Terms, definitions and abbreviated terms . 18

3.1 Terms from other standards . 18

3.2 Terms specific to the present standard . 19

3.3 Abbreviated terms. 27

3.4 Nomenclature . 29

4 Principles . 30

4.1 General . 30

4.2 Roles . 30

4.3 References to acceptance criteria . 30

5 QA for qualification . 31

5.1 Qualified PCBs . 31

5.2 Ceramic PCB technology . 32

5.3 Flexible PCB . 32

5.3.1 General . 32

5.3.2 Qualification of flexible PCB . 32

5.4 Qualification process . 34

5.5 Request for qualification . 34

5.6 Quality standards . 35

5.7 Description of qualification vehicle . 35

5.8 Evaluation . 36

5.9 Audit . 36

5.10 Qualification test programme . 38

5.11 PID . 38

5.12 Qualification approval . 39

5.13 Process change . 39

5.14 QA report . 40

5.15 Qualification renewal . 40

5.16 Nonconformances during qualification renewal . 41

6 QA for manufacture and procurement . 43

6.1 Overview . 43

6.2 Procurement process . 43

6.2.1 Overview . 43

6.2.2 Procurement specification . 44

6.2.3 Quotation . 44

6.2.4 Purchase order . 45

6.2.5 Design review (DR) . 45

6.2.6 MRR . 45

6.3 Final and in-process inspection. 46

6.4 Quality records for manufacture and procurement . 47

6.5 Control of materials and chemistry . 48

6.6 Control of plating chemistry . 49

6.7 Cleanliness of PCB processes . 50

6.7.1 Overview . 50

6.7.2 Cleanliness control . 51

6.8 Traceability . 52

6.9 Operator and inspector training. 53

6.10 Repair of bare PCBs . 54

6.10.1 Overview . 54

6.10.2 General . 54

6.11 Packaging . 56

6.12 Storage and baking of PCB and coupons . 57

6.13 Shelf-life and relife testing . 57

6.14 QA for PCB procurement in space projects. 58

7 Test and inspection for qualification . 61

7.1 Overview . 61

7.2 Test selection for qualification activities . 64

7.3 Initial qualification of PCB manufacturer . 68

7.4 Initial qualification of PCB technology . 68

7.5 Qualification renewal . 68

7.6 Delta qualification . 68

7.7 Project qualification and RFA . 69

7.7.1 Overview . 69

7.7.2 Requirements for project qualification and RFA . 69

8 Test and inspection for procurement . 74

8.1 Outgoing inspection on PCB . 74

8.2 Outgoing inspection on coupons . 75

8.2.1 Overview . 75

8.2.2 Configuration of coupons for plated holes . 78

8.2.3 Configuration of dedicated coupons . 81

8.2.4 Evaluation of coupons . 82

8.2.5 Delivery of coupons, microsections and spare coupons . 84

8.3 Reporting of outgoing inspection and delivery . 85

8.4 Incoming inspection by procurement authority . 85

8.5 FAI on PCB by microsectioning . 86

9 Test descriptions . 88

9.1 Overview . 88

9.2 Additional tests . 88

9.2.1 Cleanliness . 88

9.2.2 Bake-out . 88

9.2.3 Plated copper tensile strength and elongation . 89

9.2.4 Steam ageing . 89

9.3 Group 1 – Visual inspection and non-destructive tests . 90

9.3.1 Visual inspection - general . 90

9.3.2 Visual inspection for qualitative aspects . 90

9.3.3 Visual inspection for dimensional verification . 90

9.3.4 Impedance test . 94

9.3.5 Dielectric constant and loss tangent . 94

9.3.6 Cleanliness . 94

9.3.7 High resistance electrical test . 95

9.3.8 Continuity test . 97

9.4 Group 2 - Miscellaneous tests . 99

9.4.1 Overview . 99

9.4.2 Peel strength . 100

9.4.3 Flexural fatigue . 101

9.4.4 Bending test . 102

9.4.5 Coating adhesion – tape test . 103

9.4.6 Analysis of tin-lead coating . 104

9.4.7 Outgassing . 104

9.4.8 Thermal analysis . 105

9.4.9 Flammability . 105

9.4.10 Offgassing . 106

9.4.11 Solderability . 106

9.5 Group 3 – Thermal stress and as-received . 110

9.5.1 Overview . 110

9.5.2 Microsectioning . 110

9.5.3 Solder bath float . 115

9.5.4 Rework simulation . 115

9.5.5 Interconnect stress test (IST) . 117

9.6 Group 4 – Assembly and life test - extended. 124

9.6.1 Overview . 124

9.6.2 Test flow for group 4 . 124

9.6.3 Insulation resistance . 126

9.6.4 Dielectric withstanding voltage (DWV) . 127

9.7 Group 5 – ECM tests . 128

9.7.1 Overview . 128

9.7.2 Temperature, Humidity, Bias (THB) . 128

9.7.3 Conductive Anodic Filament (CAF) . 134

9.8 Group 6 – Assembly and life test - short . 140

9.8.1 Overview . 140

9.8.2 Test flow for group 6 . 140

9.8.3 Reflow simulation . 141

9.8.4 Thermal cycling . 141

10 Acceptance criteria . 143

10.1 Overview . 143

10.2 Inspection by microsectioning for dimensional verification . 143

10.3 Inspection by microsectioning for qualitative aspects . 164

10.4 Visual inspection . 194

10.5 Visual inspection of sculptured flex PCB . 210

10.6 Additional requirement to the tables . 229

10.6.1 Annular ring. 229

10.6.2 Pad lift and associated laminate cracks . 230

10.6.3 Miscellaneous . 232

Annex A (normative) Qualification letter – DRD . 235

Annex B (normative) CoC for PCB – DRD . 236

Annex C (normative) Qualification test report – DRD . 250

Annex D (normative) Process Identification Document (PID) for PCB

manufacturing – DRD . 251

Annex E (normative) Process change notice (PCN) – DRD . 254

Annex F (normative) QA report – DRD . 255

Annex G (normative) PCB approval sheet – DRD . 256

Annex H (informative) Example of platedthrough hole microsection . 261

Annex I (informative) Cleanliness requirements for laminate and prepreg . 262

Annex J (informative) Example qualification programme . 265

Bibliography . 268

Figures

Figure 3-1: Example of material supplier treatment side of foil (white arrows) and PCB

manufacturer treatment side of foil (opposite side) . 25

Figure 7-1: Test flow for qualification . 62

Figure 8-1: Flow for preparation, test and inspection of procurement coupons . 78

Figure 8-2: Example of Bn coupon with 3 holes per drilling sequence . 79

Figure 8-3: Example of placement of coupons and PCB in usable area of

manufacturing panel . 80

Figure 8-4: Example of vias manufactured at different plating and drilling sequences . 81

Figure 8-5: Example of target quality of microsection of rigid-flex interface with UV

fluorescent resin and polarised light . 84

Figure 9-1: Conductor width (w) measured at the foot as seen in a cross-section. . 91

Figure 9-2: Warp . 92

Figure 9-3: Twist. 93

Figure 9-4: Horizontal adjacency on layer Ln and vertical adjacency on the layers

above and below. . 97

Figure 9-5: Midpoint classification . 97

Figure 9-6: Setting of test point assignments. The numbers 1 to 7 correspond to the

conditions of requirement 9.3.8.2g. . 99

Figure 9-7: Example of target quality of microsection of innerlayer (top) and knee of the

hole (bottom), as-polished (left) and after micro-etch (right). . 113

Figure 9-8: Examples of inadequate quality of microsection showing in the top image

inadequate polishing, leaving scratches on surface, in the middle image

over-etched sample and in the bottom image inadequate lighting, revealing

no detail on metallisation, nor on laminate by transparency. 114

Figure 9-9: Examples of barrel cracks after IST testing showing a nominal crack size

(left) and a large crack filled with SnPb (right) . 123

Figure 9-10: THB test pattern . 130

Figure 9-11: Build-up for THB test vehicle . 130

Figure 9-12: Insulation resistance during THB Ambient (until sample nr 1000) and THB

ECM showing continuous breach of insulation on 4 patterns in the lower

graph. The top graph shows stable insulation. . 133

Figure 9-13: Horizontal microsection showing fibre contamination on tracks in prepreg

resin causing breach of insulation. . 133

Figure 9-14: Lay-out of CAF pattern . 137

Figure 9-15: Schematic for CAF growth . 137

Figure 10-1: Annular ring internal . 145

Figure 10-2: Annular ring external . 146

Figure 10-3: Copper foil thickness . 147

Figure 10-4: Three measurements of copper plating thickness at locations that are at 25

%, 50 % and 75 % of the height of the hole . 149

Figure 10-5: Measurement “average on resin” is performed on zone A. Measurement

“on any local thin areas on resin or glass” is performed on Zone B . 149

Figure 10-6: Glass fibre protrusion in case of negative etchback (left) and positive

etchback (right) . 150

Figure 10-7: Example of negative etchback (left) and approximately neutral etchback

(right) . 150

Figure 10-8: Wicking is measured from resin of hole wall (red arrows). In case it

exceeds the annular ring, the insulation distance to adjacent circuitry (blue

arrow) can be reduced. . 151

Figure 10-9: Example of wicking . 151

Figure 10-10: Wrap target condition . 152

Figure 10-11: Wrap thickness below requirement, not acceptable . 152

Figure 10-12:Projected-peak-to-peak insulation . 153

Figure 10-13: Example of glass compression . 153

Figure 10-14: Microvia insulation . 154

Figure 10-15: Penetration of capture pad for µvia, not acceptable . 154

Figure 10-16: Microvia aspect ratio, X ≥ Z. 155

Figure 10-17: Dimple in microvia . 155

Figure 10-18: ICD on capture pad (pictures are unetched) . 155

Figure 10-19: Microvia plating, target condition . 156

Figure 10-20: Example of void in microvia plating . 156

Figure 10-21: Tin-lead thickness in PTH schematic (left) and a typical microsection

(right) . 158

Figure 10-22: Tin-lead thickness on PTH corner – target thickness (left), coverage of less

than 1 µm (middle), absence of SnPb on IMC (right) . 158

Figure 10-23: Tin-lead thickness on pad . 158

Figure 10-24: Undercut. 161

Figure 10-25: Example of spurious copper . 161

Figure 10-26: Overhang of electrolytic Au . 162

Figure 10-27: Example of dimensional verification of rigid-flex interface . 163

Figure 10-28: Examples of acceptable voids . 167

Figure 10-29: Examples of unacceptable voids . 167

Figure 10-30: Examples of separation between hole wall and resin inside blind via . 167

Figure 10-31: Example of acceptable thin line separation . 168

Figure 10-32: Example of non-acceptable bulging . 168

Figure 10-33: Example of dimple on blind via . 169

Figure 10-34: Example of bump on blind via . 169

Figure 10-35: Example of plating nodule . 170

Figure 10-36: Example of burrs reducing hole diameter . 170

Figure 10-37: Example of voids – top image shows etch-out and bottom image shows

an encapsulated void or inclusion. 172

Figure 10-38: Skip plating on flex laminate as-polished (top) and after micro-etch

(bottom). 172

Figure 10-39: Skip plating on glass fibres . 172

Figure 10-40: Open wedge void (top), enclosed wedge void (middle), copper filled

wedge (bottom) . 174

Figure 10-41: Schematic of wedge void dimensions . 174

Figure 10-42: Example of wedge voids . 174

Figure 10-43: Example of resin void . 175

Figure 10-44: Example of delamination . 176

Figure 10-45: Pad lift schematic . 177

Figure 10-46: Examples of pad lift cracks. The right image is unacceptable because

cracks continue until the hole wall . 178

Figure 10-47: Acceptable (green) and non-acceptable (red) dielectric cracks . 180

Figure 10-48: Examples of laminate cracks . 180

Figure 10-49: Example of C foil separation as-polished and after micro-etch . 182

Figure 10-50: Example of interface line between plated copper layers on a non-etched

microsection . 182

Figure 10-51: Interconnect after stress, target condition, after microetch (top) and as-

polished (bottom) . 183

Figure 10-52: Examples of ICD . 183

Figure 10-53: Example of smear . 184

Figure 10-54: Example of hole wall pull away - showing separation of copper in a straight

line (left) or slightly bulging outward (right) . 185

Figure 10-55: Example of resin recession - showing concave retraction of resin . 185

Figure 10-56: Target condition . 186

Figure 10-57: Acceptable nail heading . 186

Figure 10-58:Unacceptable nail heading, exceeding 50 % of innerlayer copper

thickness . 186

Figure 10-59: Examples of CIC connection, target condition (left), nailheading (middle),

separation to CIC (right) . 187

st nd

Figure 10-60: Examples of swirl (1 and 2 image) and demarcation line (3rd). In the

nd

2 picture the difference between no-flow prepreg (top) and laminate

(bottom) is noticeable . 189

Figure 10-61: Example of dotted interface line observed in dark field out of focus (right),

which is not visible in focus (middle) and in bright field (left) . 189

Figure 10-62: Example of metallic contamination in laminate . 190

Figure 10-63: Acceptable adhesion between coverlay and prepreg . 191

Figure 10-64: Delamination between coverlay and prepreg . 191

Figure 10-65 Example of voids in acrylic adhesive in rigid-to-flex interface. 192

Figure 10-66: Example of adhesive filet recession into rigid section as observed in

microsection . 193

Figure 10-67: Conductor width . 195

Figure 10-68: Conductor spacing . 196

Figure 10-69: Example of lifted land . 197

Figure 10-70: Example of visible copper on top surface (left) and on side of track (right) . 197

Figure 10-71: Example of measling . 198

Figure 10-72: Examples of crazing . 198

Figure 10-73: Examples of contamination and inhomogeneity . 199

Figure 10-74: Example of scratches on conductors and dielectric . 200

Figure 10-75: Haloing at edge . 202

Figure 10-76: Haloing from non-plated hole to footprint for stiffener . 202

Figure 10-77: Granular aspect . 203

Figure 10-78: Dewetting . 203

Figure 10-79: Example of unclear marking . 204

Figure 10-80: Example of resin squeeze out . 205

Figure 10-81: Example of adhesive filet recession into rigid section as observed in

visual inspection . 205

Figure 10-82: Examples of fibre protrusion . 206

Figure 10-83: Example of acceptable incidental haloing ≤ 1 mm into rigid section . 207

Figure 10-84: Example of an acceptable superficial scratch . 209

Figure 10-85: Examples of non-acceptable cut and blister, evident by a sharp

indentation . 209

Figure 10-86: Examples of burrs on edge of flex . 209

Figure 10-87: Misregistration of top and bottom coverlay . 212

Figure 10-88: Misregistration of hole in coverlay to the conductor . 212

Figure 10-89: Examples of white spot configurations and black spot contamination . 214

Figure 10-90: Examples of fibre contamination . 214

Figure 10-91: Examples of SnPb infiltration on sculptured pad (left) and on tracks

(right) . 215

Figure 10-92: Bare copper on fingers . 216

Figure 10-93: Misregistration of pads . 217

Figure 10-94: Hole misregistration causing reduced annular ring . 218

Figure 10-95: Schematic of conductor width and spacing and local defects . 220

Figure 10-96: Examples of nick near pad, nick on conductor, overetching reducing

thickness of conductor, nick on finger, pinhole and local reduced track width

(left to right) . 220

Figure 10-97: Examples of insufficient spacing between conductors, copper residue

between pads, copper residue to edge of flex, bump on conductor (left to

right) . 220

Figure 10-98: Adhesive in plated holes . 221

Figure 10-99: Example of adhesive in plated holes . 221

Figure 10-100: SnPb coverage on pads . 222

Figure 10-101: Pad diameter reduction due to local coverage by coverlay or resin

squeeze out . 222

Figure 10-102: Copper wrinkle . 223

Figure 10-103: Tear in hole and edge of coverlay . 224

Figure 10-104: Burrs on holes . 224

Figure 10-105: Nick on edge of coverlay . 224

Figure 10-106: Coverlay scratch – Non acceptable . 225

Figure 10-107: Acceptable aspect of finger after bending . 226

Figure 10-108: Unacceptable aspect of finger after bending . 226

Figure 10-109: Cross-section of hole: Copper conductor shown . 228

Figure 10-110: Calculation of remaining insulation distance . 233

Figure H-1 : Typical phenomena in cross-section of PTH. Not all phenomena are

specified in ECSS-Q-ST-70-60 in the same way. . 261

Tables

Table 6-1: Example of lead time in weeks (wk) for various phases of PCB procurement,

manufacture, test and inspection. . 43

Table 7-1: List of coupons with pattern ID, description and references to definition

requirements . 63

Table 7-2: Test matrix for qualification and procurement . 66

Table 8-1: Sampling plan for outgoing visual inspection on PCB . 75

Table 8-2: Overview of coupons . 76

Table 9-1: Nonconformance criteria for solderability of PTH . 109

Table 9-2: CAF pattern dimensions – via-to-via straight . 136

Table 9-3: CAF pattern dimensions – via-to-via staggered . 136

Table 9-4: CAF pattern dimensions – via-to-plane . 136

Table 10-1: Annular ring internal . 145

Table 10-2: Annular ring external . 146

Table 10-3: Copper foil thickness . 147

Table 10-4: Copper plating thickness . 148

Table 10-5: Etchback and glass fibre protrusion . 150

Table 10-6: Wicking . 151

Table 10-7: Wrap copper . 152

Table 10-8: Dielectric thickness – standard technology . 153

Table 10-9: Dielectric thickness – microvia layers . 154

Table 10-10: Dimension and aspect of microvias . 155

Table 10-11: Microvia plating voids . 156

Table 10-12: Tin-lead thickness and composition . 157

Table 10-13: Dimensional requirements for electrolytic and chemical Ni, Pd, Au . 159

Table 10-14: Undercut and spurious copper . 160

Table 10-15: Overhang. 162

Table 10-16: Rigid-flex interface -dimensional verification . 163

Table 10-17: Blind, buried and plugged via filling. 166

Table 10-18: Cap lift on blind via and plugged via . 168

Table 10-19: Blind and plugged via planarity . 169

Table 10-20: Burrs and nodules . 170

Table 10-21: Voids and inclusions in copper plating . 171

Table 10-22: Wedge voids . 173

Table 10-23: Resin void . 175

Table 10-24: Delamination, blistering, crazing, measling . 176

Table 10-25: Pad Lift . 177

Table 10-26: Dielectric cracks . 179

Table 10-27: Cracks and separation in copper . 181

Table 10-28: Interconnect defect, ICD .

...

Questions, Comments and Discussion

Ask us and Technical Secretary will try to provide an answer. You can facilitate discussion about the standard in here.

Loading comments...